Spyglass CDC rule

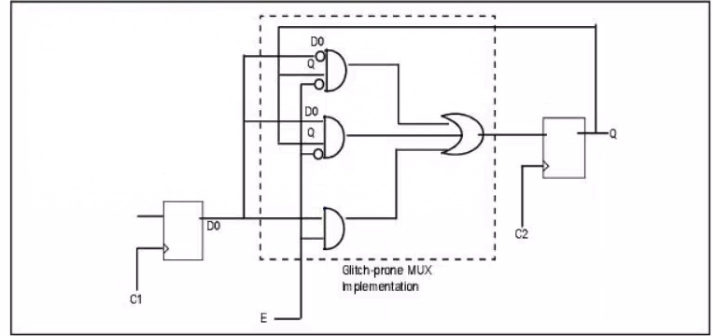

Ac_glitch01 由于易产生毛刺的mux电路导致跨时钟存在问题。

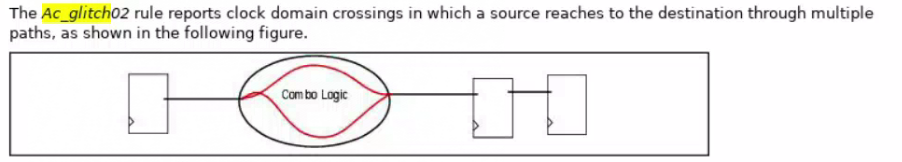

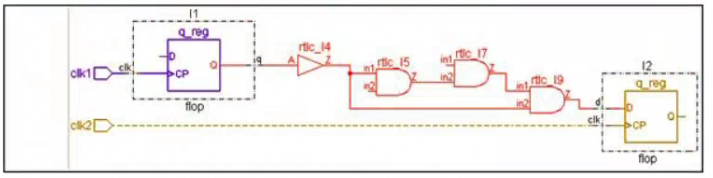

Ac_glitch02 它时用于检查 source signal recovergence 产生刺导致跨时钟域出现问题。

如下图所示q_reg/O -> I1/q_reg/D存在两条组合路径,由于传输延迟就导致destination端存在glitch。

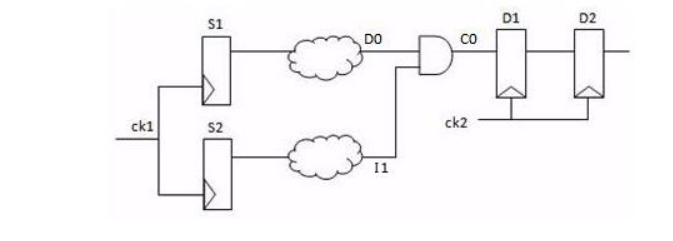

Ac_glitch03 不同信号的路径延迟导致destination 端存在glitch。

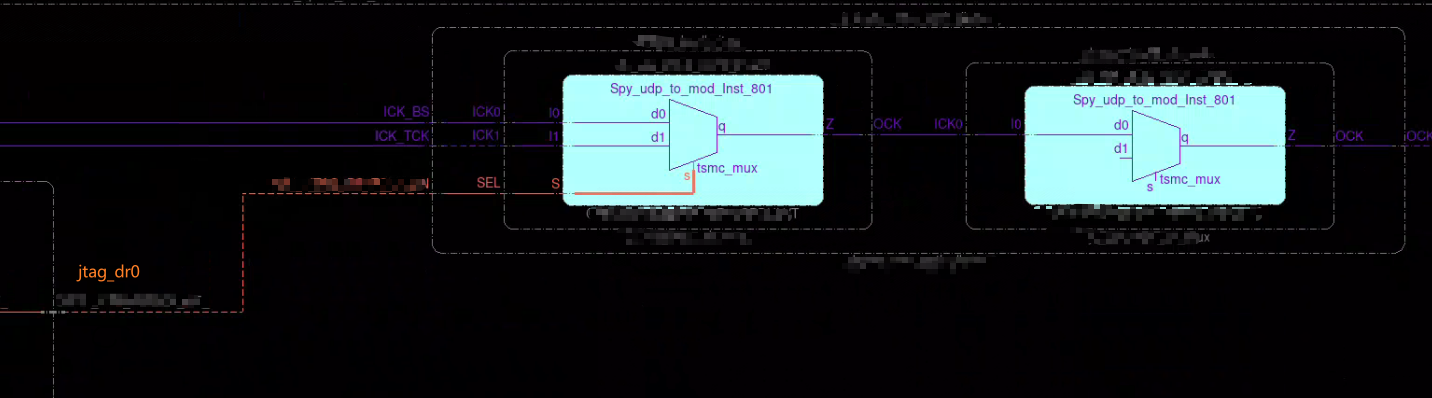

clock_glitch03 会报告一个异步信号与一个clock信号汇聚,导致存在潜在的clock glitch风险。

如上图所示工具报告jtag_dr0与ICK_TCK ICK_BS发生汇聚,但由于汇聚发生在clock_mux中,做了glitchfree处理,因此可以直接waive了。

clock_info03 主要是报告clock未正确约束。

clock_info05b 报告clock在组合逻辑单元而不是mux单元汇聚,通过设置set_case_analysis解决。

clock_sync05 PI被多个domain时钟采样,

clock_sync06 多个domain的clock驱动Primary output