[硬件电路-73]:模拟器件 - 什么是电路的信号振铃现象?其根本原因?如何解决?

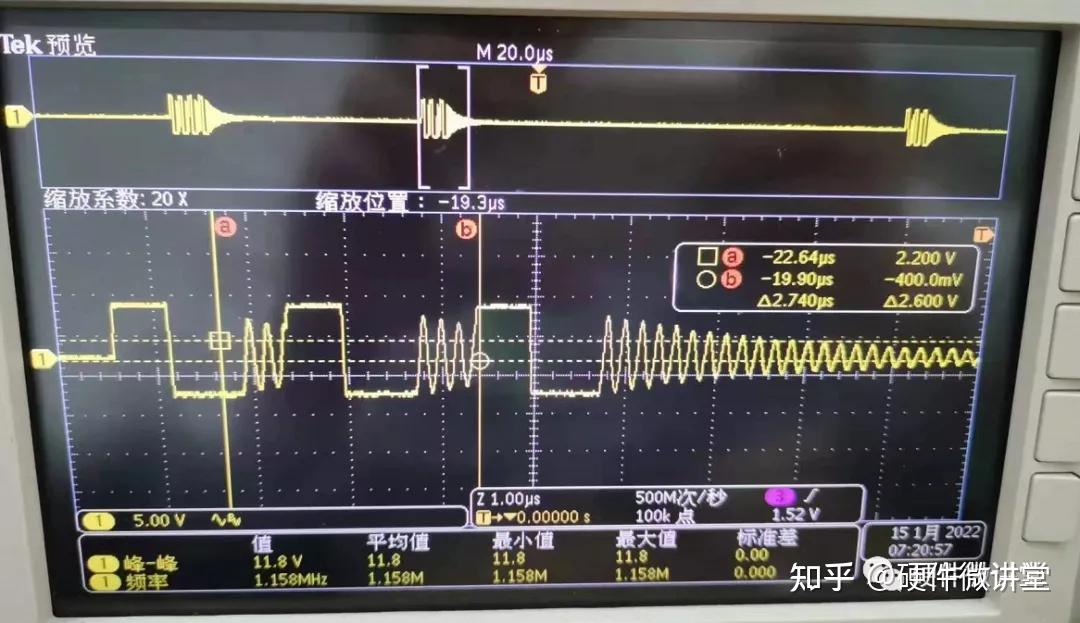

电路中的信号振铃现象(Ringing)是信号在传输或切换过程中出现的周期性过冲(Overshoot)和下冲(Undershoot)振荡,表现为信号边缘的“振荡尾巴”。这种现象常见于高速数字电路、射频电路和电源电路中,可能引发信号失真、时序错误甚至硬件损坏。以下是详细分析:

一、信号振铃现象的表现

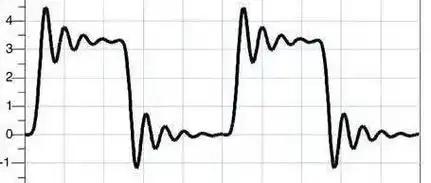

- 数字电路中的振铃:

- 现象:信号在上升沿或下降沿后出现多次振荡,幅度逐渐衰减(如图1所示)。

- 影响:导致接收端误判逻辑电平(如将“0”误判为“1”),引发时序错误或数据错误。

- 示例:PCIe总线、DDR内存信号线中常见振铃,可能造成系统不稳定。

- 模拟/射频电路中的振铃:

- 现象:信号波形出现周期性振荡,可能伴随幅度衰减或持续振荡。

- 影响:增加噪声、降低信噪比(SNR),甚至导致放大器自激振荡。

二、信号振铃的根本原因

振铃的本质是电路中存在能量存储与释放的反复过程,主要由以下因素引起:

2. 寄生参数(LC谐振主导)

- 原理:电路中的寄生电感(L)和寄生电容(C)形成LC谐振回路,当信号能量在LC回路中反复交换时,产生振荡。

- 典型场景:

- 电源完整性(PDN)问题:电源平面与地平面之间的寄生电感与去耦电容形成谐振,导致电源噪声振铃。

- 封装寄生效应:芯片引脚、键合线等存在寄生电感,与封装电容谐振。

3. 信号边沿过陡(高频分量丰富)

- 原理:快速变化的信号(如上升时间tr极短的数字信号)包含丰富的高频分量,高频信号更容易因阻抗不匹配或寄生参数引发振铃。

- 数学表达:信号频谱中高频分量幅度与1/f成正比,边沿越陡,高频分量越多。

4. 非线性元件(如二极管、晶体管)

- 原理:非线性元件在特定工作点可能引入负阻抗,导致电路自激振荡(如运算放大器的相位裕度不足)。

三、信号振铃的解决方案

针对不同原因,需采取针对性措施:

1. 阻抗匹配(消除反射)

- 方法:

- 源端匹配:在源端串联电阻Rs,使Zs+Rs=Z0(适用于低功耗场景)。

- 负载端匹配:

- 并联电阻Rp=Z0(适用于单端传输线)。

- 戴维南匹配(两个电阻分压至VCC/2,适用于高速串行总线)。

- AC耦合匹配(通过电容隔离直流,适用于差分信号)。

- 传输线优化:使用控制阻抗的PCB设计(如微带线、带状线),确保Z0一致。

- 工具:使用TDR(时域反射计)测量阻抗连续性。

2. 抑制寄生LC谐振(阻尼控制)

- 方法:

- 增加阻尼电阻:在LC回路中串联小电阻(如铁氧体磁珠),消耗振荡能量。

- 优化去耦电容布局:在电源引脚附近放置多个不同容值的去耦电容(如0.1μF + 10nF),覆盖宽频段噪声。

- 减少寄生参数:缩短走线长度、增加线宽、使用低介电常数材料。

- 示例:在DDR内存电源引脚处添加0欧姆电阻作为阻尼器。

3. 限制信号边沿速率(频谱控制)

- 方法:

- 串联电阻(Series Resistor):在驱动端串联22Ω~100Ω电阻,减缓信号上升时间。

- 预加重/去加重(Pre-emphasis/De-emphasis):在发送端增强高频分量(预加重)或衰减低频分量(去加重),补偿传输线损耗,同时避免过冲。

- 使用低速信号:在满足时序要求的前提下,降低信号速率(如从1GHz降至500MHz)。

4. 非线性元件的稳定性设计

- 方法:

- 增加相位裕度:在运放反馈网络中添加补偿电容,确保闭环稳定性。

- 避免自激振荡:在功率放大器输出端添加隔离电阻或RC网络,破坏谐振条件。

5. 仿真与测试验证

- 仿真工具:使用HyperLynx、ADS等软件进行信号完整性(SI)和电源完整性(PI)仿真,预测振铃风险。

- 测试方法:

- 眼图测试:观察数字信号质量,评估振铃对时序的影响。

- 频谱分析:通过频谱仪检测高频谐振峰。

四、案例分析

案例1:PCIe总线振铃问题

- 现象:信号在上升沿后出现200mV振荡,持续1ns。

- 原因:传输线末端未端接,反射系数Γ=+0.5。

- 解决方案:在接收端并联50Ω终端电阻,振铃幅度降低至50mV。

案例2:电源平面振铃

- 现象:电源噪声在100MHz处出现峰值,幅度达50mV。

- 原因:电源平面与地平面之间的寄生电感(2nH)与去耦电容(10nF)形成谐振。

- 解决方案:在电源引脚附近添加0.1μF去耦电容,谐振峰移至500MHz,幅度降至10mV。

五、总结

信号振铃是电路设计中常见的信号完整性问题,其根本原因包括阻抗不匹配、寄生谐振、边沿过陡和非线性效应。解决方案需结合仿真与测试,从阻抗匹配、寄生参数抑制、边沿速率控制和稳定性设计等多方面入手。通过系统化的设计流程,可有效消除振铃,提升电路性能和可靠性。