RISC-V基金会Datacenter SIG月会圆满举办,探讨RAS、PMU性能分析实践和经验

一直以来,龙蜥社区在 RISC-V 生态建设中持续投入,并积极贡献上游社区。多位龙蜥社区成员在 RISC-V 国际基金会担任主席/副主席角色,与来自阿里云、阿里达摩院、中兴通讯、浪潮信息、中科院软件所、字节跳动、Google、 MIT、Akeana 等企业的专家共同推动基金会 Datacenter SIG 的运作及相关标准的制定。

(图/Datacenter SIG 6月月会分享)

近日,RISC-V 基金会 Datacenter SIG 月度会议于线上召开,来自阿里云、中兴通讯、字节跳动等企业的郭任、贾云翔、宋卓、王子昂、朱友欣等 18 位委员及代表参会。在 Datacenter SIG 的 5 月[2]和 6 月[3]度会议中分别分享了阿里云在 X86 和 ARM 架构下 RAS、PMU 性能分析的实践和经验,提出了 4 个 Proposal 用于优化 RSIC-V 架构的 RAS 和 PMU,其中包括同步 RAS 错误处理,统一 uncore PMU 架构等,后续也将和基金会共同推进后续的工作开展。龙蜥社区还将与伙伴们持续推进 RISC-V 与云计算结合的场景,包括虚拟化、QoS、加速器等高性能软硬件技术和生态的共同完善。

在 5 月月会上,RISC-V SIG 成员、阿里云技术专家薛帅分享了 X86 和 ARM 架构的云中 RAS(可靠性、可用性、可维护性)技术的经验和实践。他详细介绍了全栈软硬件协同技术解决方案(包括硬件、固件、内核和应用程序层)、RAS 工具的上游开源贡献(包括开发工具和测试用例)、阿里云在故障预测方面的工作进展(参考 HPCA 2025 论文)以及与 NVIDIA 在与 GPU 相关的 RAS 优化方面的合作。针对 RISC-V SSE 无法有效处理同步错误的问题,薛帅提出了两项关于同步错误处理结合 RISC-V 的建议,并提议成立专项技术组(TG)。该建议是继续促进 SIG 与各企业间的合作以提升 RISC-V RAS 技术能力,并进一步增强在规范、固件和内核层的支持。

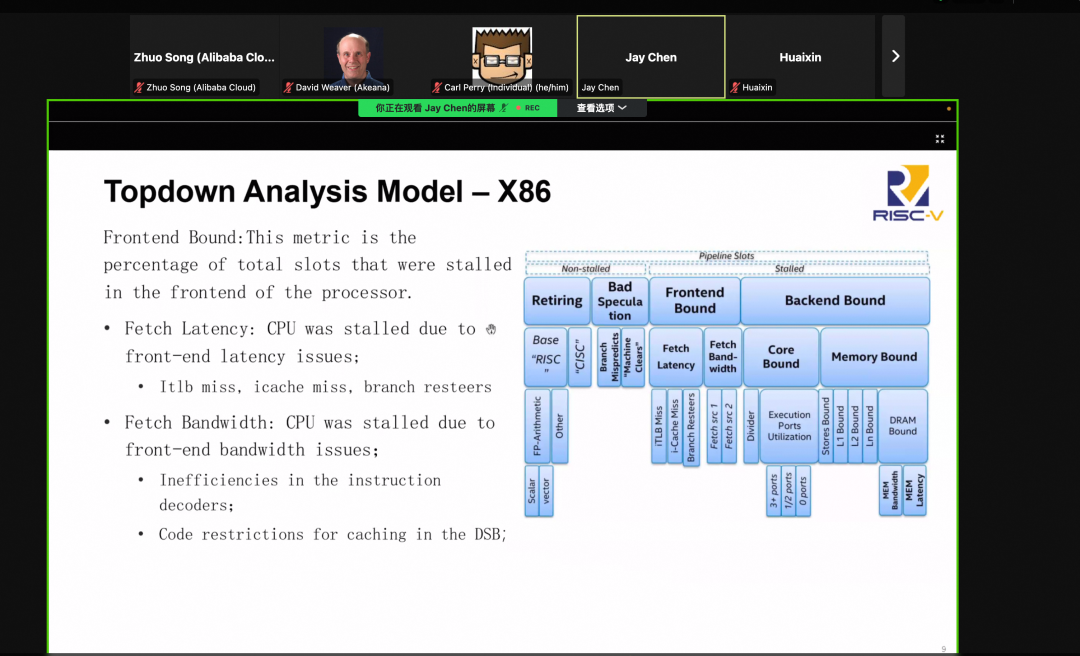

在 6 月月会上,RISC-V SIG 成员、阿里云技术专家陈健康分享了 X86 和 ARM 架构的云中 PMU 技术的经验和实践。他详细介绍了云计算场景下的性能分析挑战和解决方案,包括处理复杂业务场景(如存储、网络、AI、电商等)的需求,以及在多架构硬件环境(X86/ARM/RISC-V)下的分析方法,并与参会嘉宾重点讨论了 CPU 瓶颈分析和多架构支持,通过 Topdown 分析模型在不同架构上的应用,以及多平台分析框架 PAS 的设计实现来解决性能分析问题。此外,陈健康还详细介绍了先进的核心 PMU 特性,如 BRBE(用于优化数据库服务前端性能)和 SPE(用于指令级精确采样)等技术,并通过实际案例展示了这些技术在云环境中的应用,特别是在内存访问延迟检测和伪共享问题分析等方面的实践。由于 RISC-V 对精确内存延迟采集的缺失以及 uncore PMU 统一架构缺失,会上,陈健康提出了两项关于 RISC-V 架构下内存延迟采集以及统一 uncore PMU 的建议,并提议成立专项技术组(TG)。来自 Google 的 Snehasish Kumar (RISC-V Performance Analysis SIG 副主席)认同访存延迟 PMU 对云场景特别关键,建议后续 Datacenter SIG 和 Performance Analysis SIG 共同合作推进。

近期,龙蜥社区在 RISC-V 也有一些进展,包括 Anolis OS 23.3 RISC-V 预览版的发布、 龙蜥社区多位专家参加 2025 RISC-V 中国峰会,分享龙蜥社区在 RISC-V 领域后续的规划等。

本次会议内容已同步在 Datacener SIG:

[1] https://github.com/riscv-admin/datacenter

[2]https://github.com/riscv-admin/datacenter/blob/main/minutes/2025-05-30-minutes.md

[3]https://github.com/riscv-admin/datacenter/blob/main/minutes/2025-06-27-minutes.md

—— 完 ——