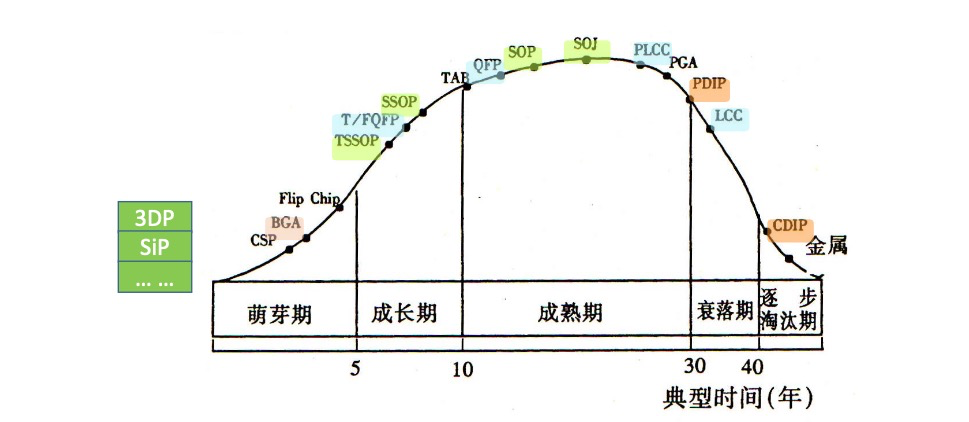

封装技术生命周期 从CDIP到CSP到SiP先进封装

这张图展示了半导体封装技术的演化周期图,包括不同封装类型在其生命周期中的“萌芽期-成长期-成熟期-衰落期-逐步淘汰期”的演进轨迹。下方和图中列出的是各类封装的缩写(Package Type Abbreviations)

🟧 早期与传统封装(CDIP、PDIP 等)

| 缩写 | 全称 | 技术简介 |

|---|---|---|

| CDIP | Ceramic Dual In-line Package | 陶瓷双列直插封装,70年代常用于军工、早期微处理器,气密性强、散热好,成本高。 |

| PDIP | Plastic Dual In-line Package | 塑料双列直插封装,适合插入 PCB 孔中,曾广泛用于早期 MCU 与逻辑器件。 |

| LCC | Leadless Chip Carrier | 无引脚芯片载体,封装四周有金属垫片,体积更小,常用于高频器件。 |

| PGA | Pin Grid Array | 插针阵列封装,适用于大面积芯片,曾是高端 CPU 的主流封装。 |

🟨 成熟期引脚式封装(90年代)

| 缩写 | 全称 | 技术简介 |

|---|---|---|

| QFP | Quad Flat Package | 四边引脚扁平封装,广泛应用于消费电子、MCU、DSP。 |

| PLCC | Plastic Leaded Chip Carrier | 塑料引线芯片载体,类似 QFP,但用于插座或表贴更灵活。 |

| SOP | Small Outline Package | 小型外形封装,外形更紧凑,适用于中低引脚数的模拟和逻辑器件。 |

| SSOP | Shrink Small Outline Package | 缩小版 SOP,引脚间距更小,节省 PCB 空间。 |

| TSOP | Thin Small Outline Package | 超薄小型封装,常用于存储器(如 SDRAM)。 |

| TQFP/FQFP | Thin/Fine-pitch Quad Flat Package | 超薄/细间距 QFP,用于空间有限、需较高引脚密度的应用。 |

| SOJ | Small Outline J-lead | J 型引脚小外形封装,常用于 DRAM 存储器件。 |

| TAB | Tape Automated Bonding | 胶带自动键合封装,早期用于高频信号传输,现较少使用。 |

🟦 2000 年前后先进封装技术

| 缩写 | 全称 | 技术简介 |

|---|---|---|

| BGA | Ball Grid Array | 球栅阵列封装,信号通过焊球连接到底部,散热性和引脚密度优异,是现代主流封装之一。 |

| FC PKG | Flip-Chip Package | 倒装芯片封装,芯片倒置焊接在载体上,布线短、性能高、散热好。 |

| WLCSP | Wafer-Level Chip Scale Package | 晶圆级芯片封装,封装尺寸与裸芯片几乎相同,适合小型化、便携设备。 |

| CSP | Chip Scale Package | 芯片级封装,封装尺寸不超过裸芯片的1.2倍,适合手机、IoT等轻量产品。 |

🟩 新一代系统级与三维封装(2010s~)

| 缩写 | 全称 | 技术简介 |

|---|---|---|

| SiP | System in Package | 系统级封装,在一个封装内集成多个芯片(逻辑+存储+射频等),实现功能模块化。 |

| 3DP | 3D Package | 三维封装,通过 TSV(通孔硅)堆叠芯片,提升集成密度与带宽。 |

| 3D IC | 3D Integrated Circuit | 真正意义上的芯片级堆叠与互连,已用于高端 AI 芯片、HBM、异构集成场景。 |

🔁 演进规律简述:

- 封装形式从“引脚式” → “焊球式” → “堆叠式”;

- 设计目标从结构简洁转向高性能、高集成、高散热;

- 当前主流方向:SiP、3D IC、Chiplet-based封装(如Intel Foveros, TSMC CoWoS)。