调试原理[简要描述]

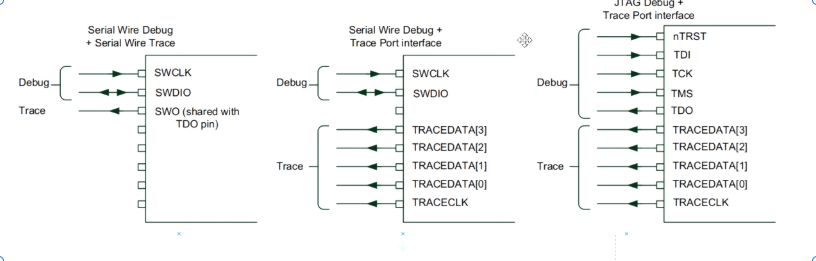

1.不同模式下的调试接口

-

相对于JTAG SWD的有效载荷会更高

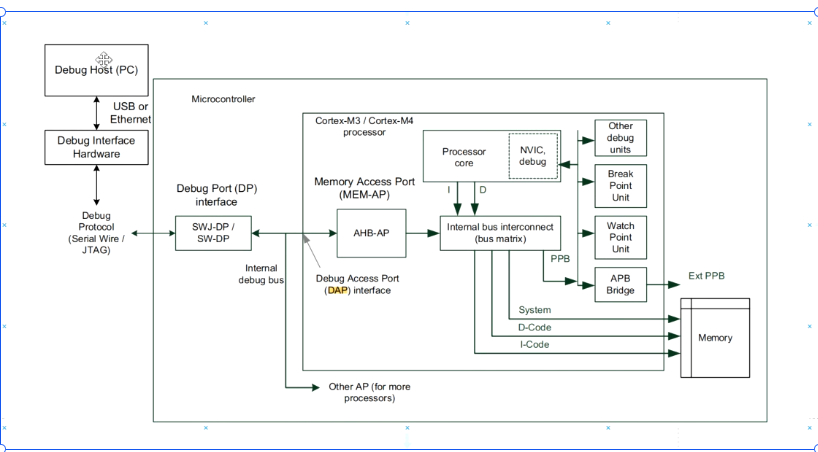

2.调试架构

-

调试主机(Debug Host, PC)

作为调试的发起端,通过USB 或以太网与 “调试接口硬件” 通信,发送调试指令(如设置断点、读取寄存器、下载程序等)。

-

调试接口硬件(Debug Interface Hardware)

负责将 PC 的指令转换为调试协议(Serial Wire 或 JTAG),是 PC 与微控制器之间的 “硬件翻译层”。

-

调试端口(Debug Port, DP)接口

微控制器的外部调试入口,包含 SWJ-DP/SW-DP 模块:

-

SWJ-DP:支持 Serial Wire 和 JTAG 两种调试协议的复用端口; -

SW-DP:仅支持 Serial Wire 协议的简化端口。它通过内部调试总线将调试信号传入微控制器内部。

-

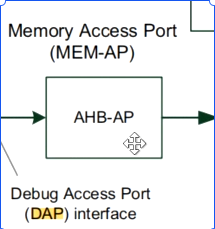

调试访问端口(Debug Access Port, DAP)

微控制器内部的调试控制核心,包含 Memory Access Port(MEM-AP):

-

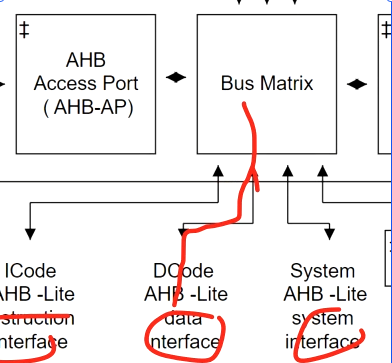

AHB-AP:基于 AHB 总线的访问端口,负责将调试指令转换为总线操作,访问微控制器的内部总线互联(bus matrix)。

-

内部总线互联(Internal bus interconnect, bus matrix)

微控制器的总线调度中心,连接以下核心模块:

-

处理器核心(Processor core):Cortex-M3/M4 内核,是程序执行的核心。

-

NVIC 调试模块(NVIC, debug):嵌套向量中断控制器的调试组件,支持中断相关的调试操作。

-

断点单元(Break Point Unit):用于设置代码断点,使程序在指定位置暂停。

-

观察点单元(Watch Point Unit):用于监控数据访问(如变量读写),触发调试动作。

-

其他调试单元(Other debug units):支持覆盖率分析、性能统计等扩展调试功能。

-

APB 桥(APB Bridge):连接到扩展私有外设总线(Ext PPB),用于访问外设。

-

存储器(Memory):通过

System、D-Code(数据总线)、I-Code(指令总线)三类总线访问程序存储区和数据存储区。

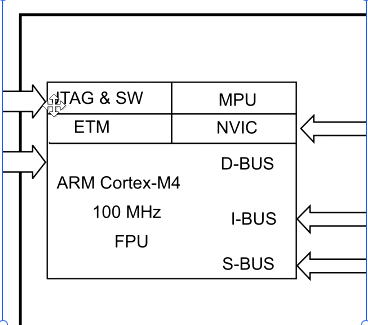

3.内核总线侵入式调试(交互过程)

-

AHB Access Port就会接再那个debug口(SW-DP or SWJ-DP),那么就可以和我们的系统进行一个交互

通过内核这个JTAG&SW(DAP外设)进行访问(通信协议)

3.

通过DAP进来找到一个AP,ap就可以找内部总线上寻址(对应上面的Bus Matrix)

4.

继续访问SRAM或Flash和外设寄存器 也可以往内核走 看cpu或nvic的寄存器

因为要访问总线 整个cpu的运行速度和外部沟通的速度会变慢。无法解决 所以叫侵入式调试

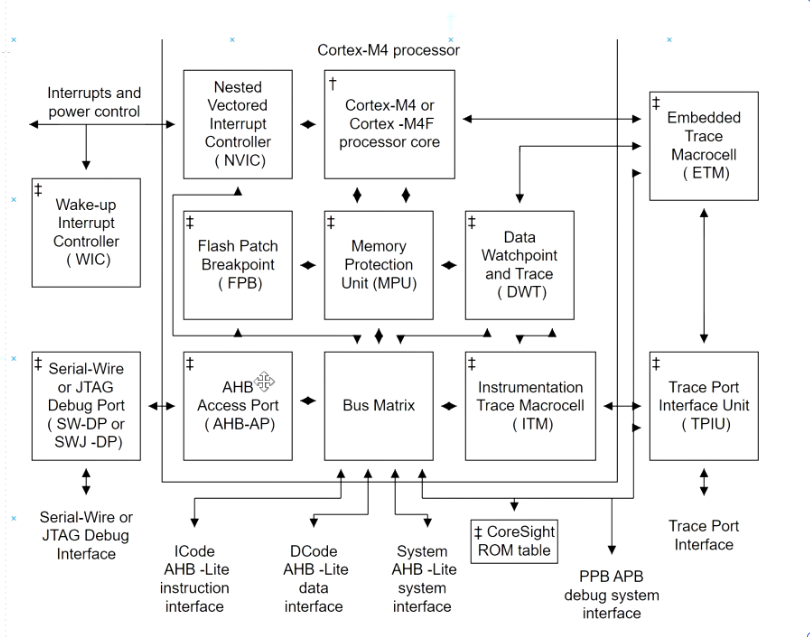

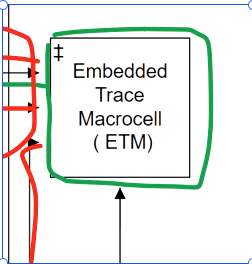

3.非侵入式调试(高阶调试)

-

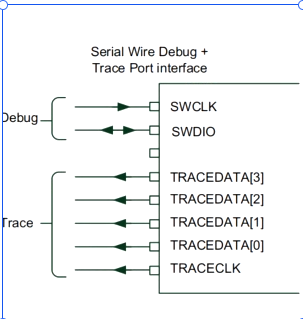

与上面不同 通过ETM单元 可以直接与cpu DWT和Bus Matrix对接,这可以让cpu没有任何的延迟,直接获取cpu的指令

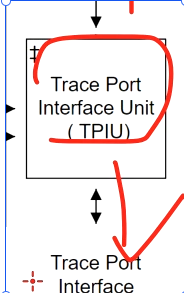

2.获取到的数据就通过tpiu出来

3.通过trace通道输出出来 数据量庞大

拓展知识

. 总线矩阵(Internal bus interconnect, bus matrix)的核心作用

总线矩阵是内核内部的总线调度中心,负责管理多主设备对多从设备的并发访问,核心功能包括:

-

多主设备仲裁:支持多个主设备(如处理器核心、DMA、调试模块的 AHB-AP)同时发起总线请求,通过仲裁机制(如优先级配置)确保高优先级访问(如中断、调试)优先响应。

-

多总线并行访问:I-Code、D-Code、System 总线可并行操作,例如处理器同时从 I-Code 取指令、从 D-Code 读数据、从 System 总线访问外设,大幅提升内核吞吐量。

-

从设备路由:将主设备的访问请求路由到对应的从设备(如指令 Flash、数据 SRAM、外设寄存器),实现 “一主多从” 的灵活访问。

-

与 AHB/APB 总线的区别与关联

-

区别:Cortex-M4 内部总线(I-Code、D-Code、System)是内核级总线,专注于内核与最核心的存储 / 外设交互;而 AHB/APB 属于芯片级总线(由芯片厂商在 Cortex-M4 内核外扩展),AHB 用于高速外设 / 存储器,APB 用于低速外设,属于 “内核外的总线层级”。

-

关联:总线矩阵通过APB 桥(APB Bridge) 连接到芯片级的 APB 总线,实现内核与外部低速外设的通信;同时,调试模块的 AHB-AP 通过总线矩阵,可访问内核的 I-Code、D-Code、System 总线,从而实现对指令、数据、外设的调试操作(如断点、寄存器读取)。