总结与建议

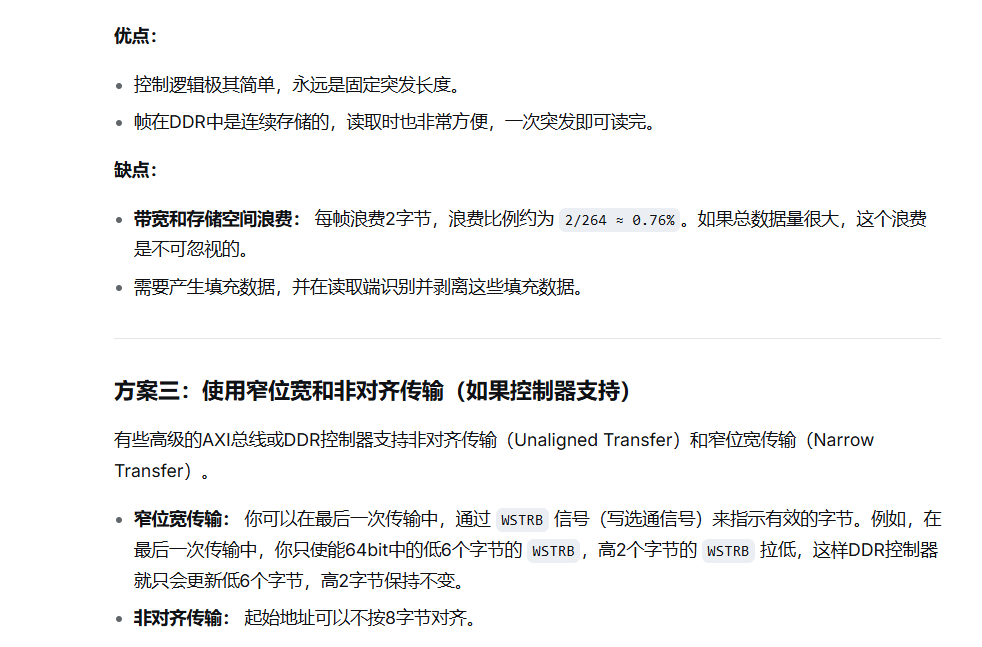

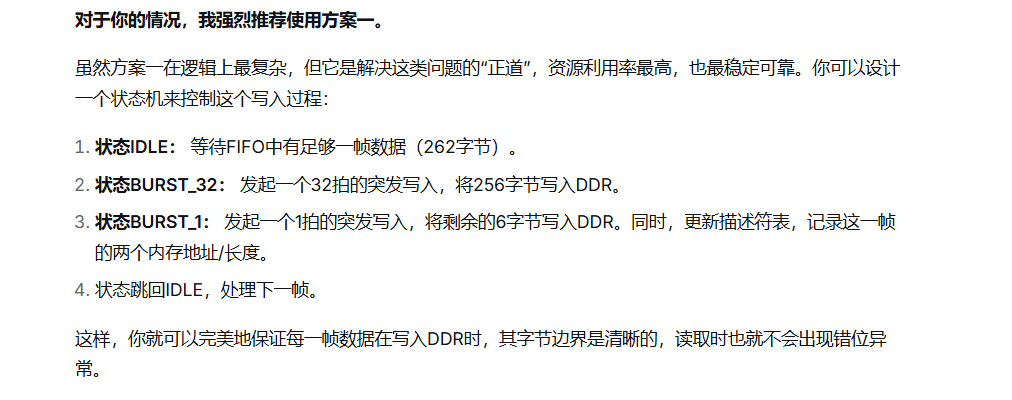

| 方案 | 原理 | 优点 | 缺点 | 适用场景 |

|---|

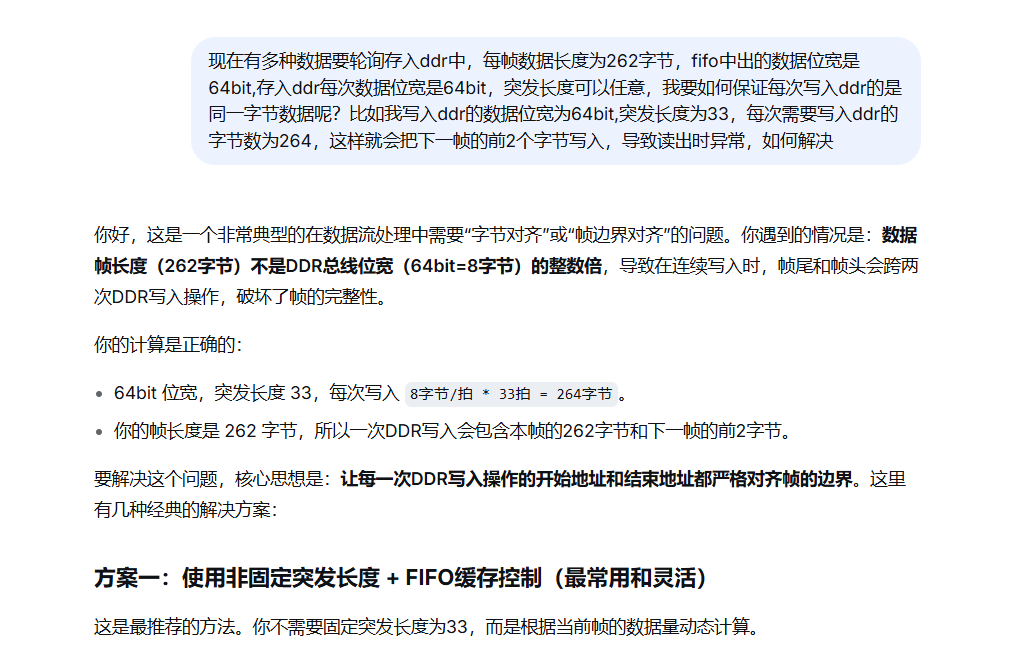

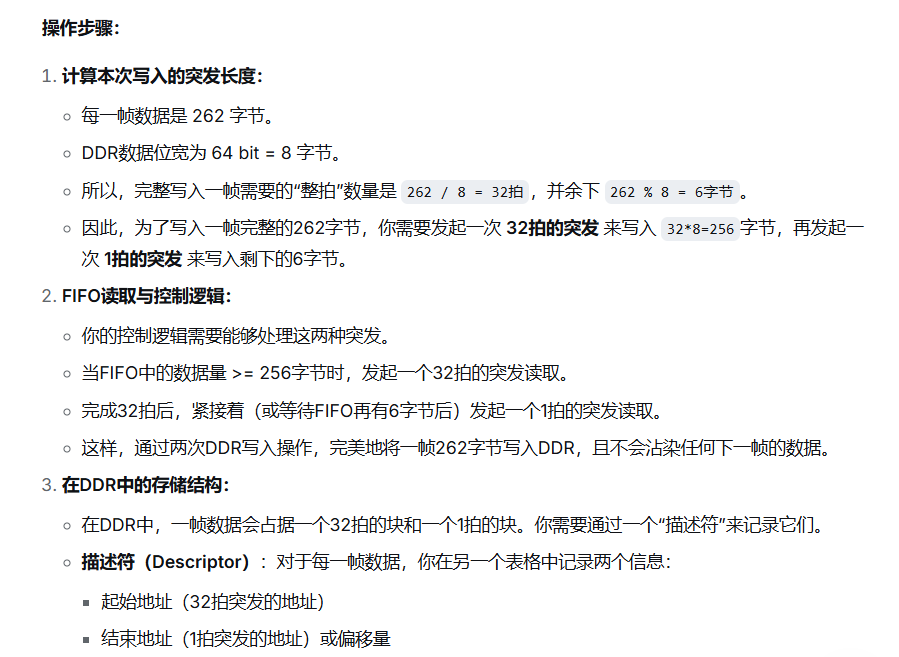

| 方案一(推荐) | 分两次突发写入,用描述符管理 | 存储效率100%,通用性强 | 控制逻辑复杂,需要描述符 | 对带宽和存储空间敏感的大流量应用 |

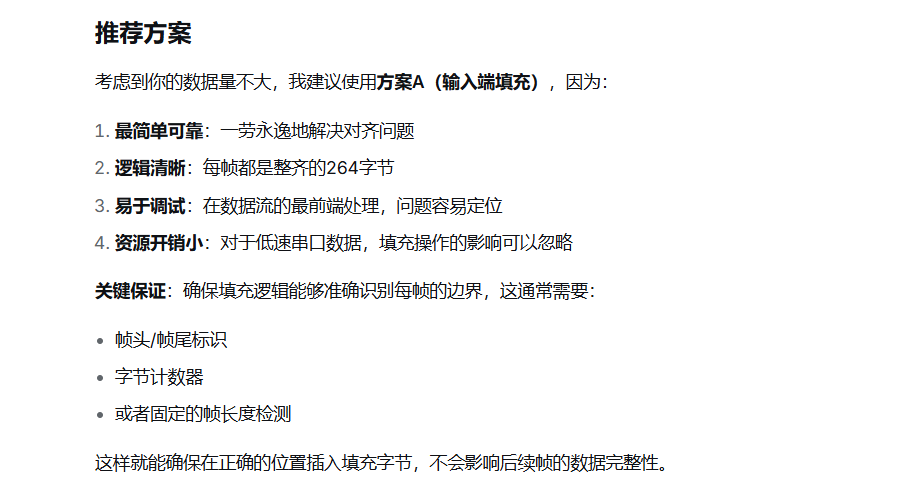

| 方案二 | 填充数据至对齐边界 | 控制逻辑最简单 | 浪费带宽和存储空间 | 小数据量,或对开发速度要求高、资源充裕的场景 |

| 方案三 | 利用控制器的特殊功能 | 存储效率100%,控制相对简单 | 依赖硬件支持,有风险 | 明确知道控制器支持且对逻辑简化有要求的场景 |

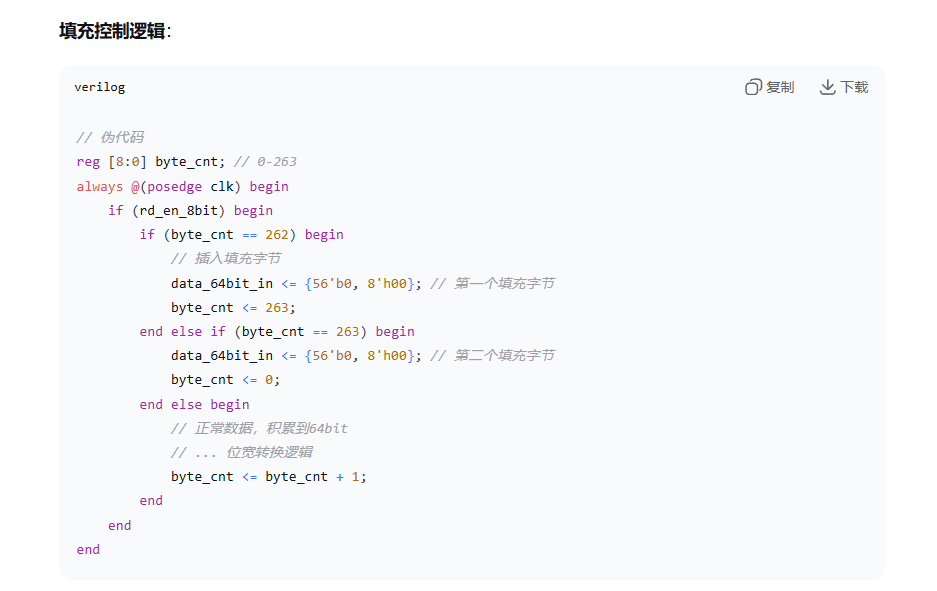

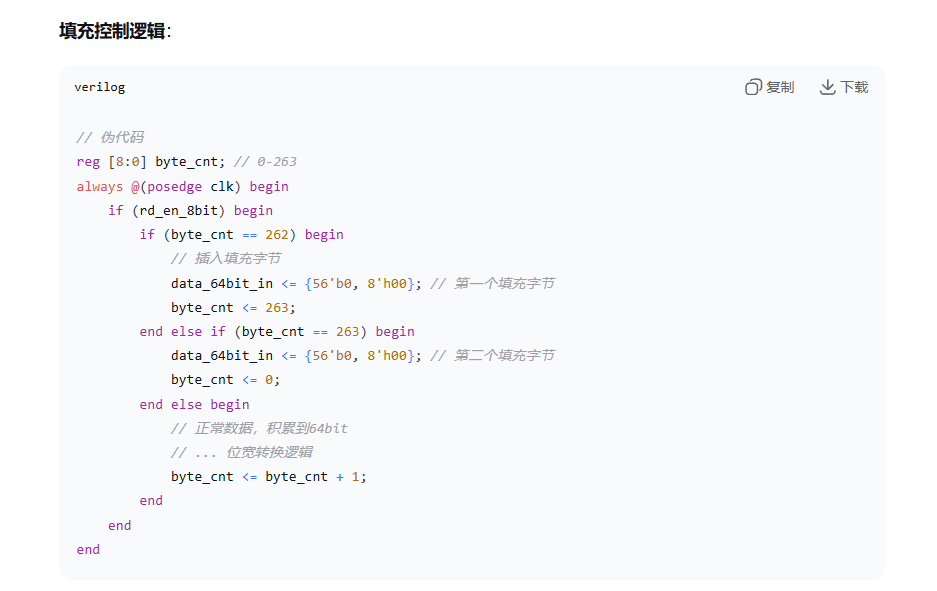

// 伪代码示例

reg [8:0] byte_counter; // 0-263的计数器

reg [7:0] tx_data;

reg tx_valid;always @(posedge clk) beginif (uart_data_valid) beginif (byte_counter < 262) begin// 正常数据tx_data <= uart_data;tx_valid <= 1'b1;byte_counter <= byte_counter + 1;end else begin// 填充阶段tx_data <= 8'h00; // 填充0tx_valid <= 1'b1;byte_counter <= byte_counter + 1;if (byte_counter == 263) beginbyte_counter <= 0; // 下一帧开始endendend else begintx_valid <= 1'b0;end

end

// DDR写入控制状态机

typedef enum {IDLE,WRITE_MAIN, // 写入32个突发(256字节)WRITE_REMAIN // 写入1个突发(6字节)

} state_t;state_t current_state;

reg [7:0] burst_counter;always @(posedge clk) begincase(current_state)IDLE: if (frame_ready) begincurrent_state <= WRITE_MAIN;burst_counter <= 32;endWRITE_MAIN:if (burst_done) beginif (burst_counter == 0) begincurrent_state <= WRITE_REMAIN;endendWRITE_REMAIN:if (burst_done) begincurrent_state <= IDLE;// 更新帧描述符endendcase

end