分频器介绍

分频器包括: 奇数和偶数分频器。

偶数分频:

偶数分频器最常见的是二分频【源时钟的2个半周期==分频后时钟的半周期】。 也就是在时钟的一个沿垫片信号发生跳变(可以选择在上升沿/ 下降沿跳变)。 扩展到4 、6、8、……分频后。 需要增加例如4分频【源时钟的4个半周期==分频后时钟的半周期哦】,增加一个1bit的计数器。 在时钟上升沿计数器cnt 跳动(0-1-0-1) ,最后四分频是:

reg cnt;

reg clk_div4;always@(posedge clk or negedge rst_n)beginif(~rst_n)cnt<=1'b0;else if(cnt==1'b1)cnt <=1'b0;else {cnt_nc,cnt} <=cnt+1'b1;

end always@(posedge clk or negedge rst_n)beginif(~rst_n)clk_div4<=1'b0;else if(cnt==1'b1)clk_div4<=~clk_div4;

end 所以偶数分频器是: 计数器+ 上升沿的方式可以实现任意偶数分频,且频占比是50%-50%;

若实现N的偶数分频,需要增加的cnt 位宽为: $clog(n/2) 或者$clog(n/2)+1 【取决于是否为2的幂次方】

奇数分频:

级数分频,因为数奇数个源时钟的半周期== 分频后时钟的半周期。也就是分频后时钟的中间一段拼接起来是源时钟的一个周期。

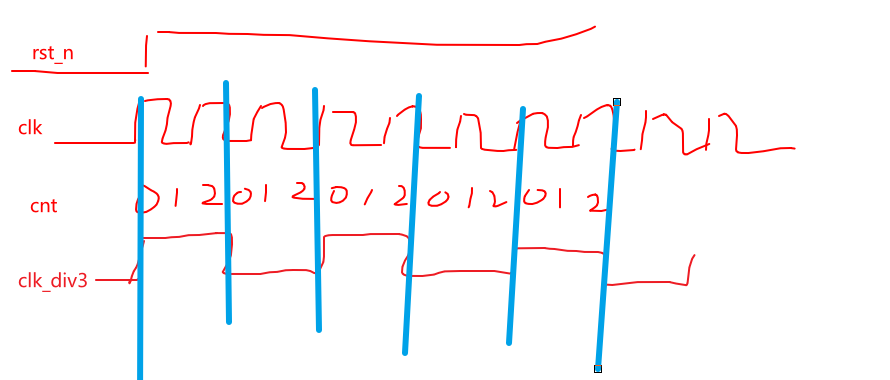

如下图显示的3分频,蓝色部分是原时钟的一个完成周期。

可以使用类似2分频的方法,涉及到源时钟的一个周期的切割,所以计数器不能只统计单沿。奇数分频需要统计双沿。

例如3分频的计数器,计数器位宽为 $clog(3)+1= 2bit 。

但是会出现如下问题: 在0 的上升沿和2 的下降沿都要跳变。 不符合编码 ???

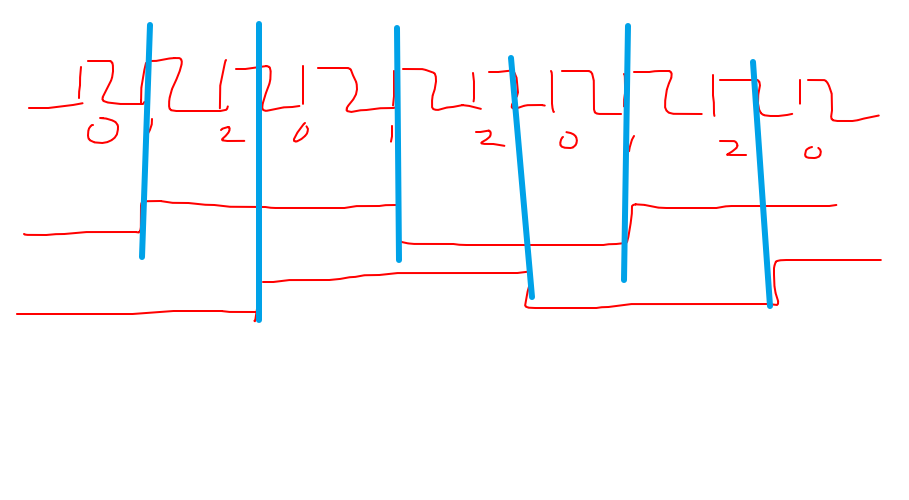

所以采用另外一种方式,将3 分频扩展为6分频。 然后分别在上升沿和下降沿做分频。

最后将生产的2路电平信号& 或者 ^ (取决于电平生成方式先高后低还是先低后高)。

module d3(input clk,input reset,output div_three

);

reg [1:0] cnt=2'b00;

reg div_clk1;

reg div_clk2;

always @(posedge clk or negedge reset)begin

if(reset == 1'b0)begincnt <= 0;end

else if(cnt == 2)cnt <= 0;

else begincnt <= cnt + 1;end

end

always @(posedge clk or negedge reset)beginif(reset == 1'b0)begindiv_clk1 <= 0;endelse if(cnt == 0)begindiv_clk1 <= ~div_clk1;endelsediv_clk1 <= div_clk1;end

always @(negedge clk or negedge reset)beginif(reset == 1'b0)begindiv_clk2 <= 0;endelse if(cnt == 2)begin //注意:此处cnt==1的话可以实现占空比为1/6的波形div_clk2 <= ~div_clk2;endelsediv_clk2 <= div_clk2;end

assign div_three = div_clk2 ^ div_clk1;//相同为0,相异为1.a1:assert property( //SVA断言语句

@(posedge clk)div_three ##2(!div_three));//断言

endmodule上面的代码修改div_clk2的电平拉起时间,可以实现多种屏占比的3分频电路。