5 Simplified LPDDR6 State Diagram(简化LPDDR6状态图)

1 Simplified LPDDR6 State Diagram(简化LPDDR6状态图)

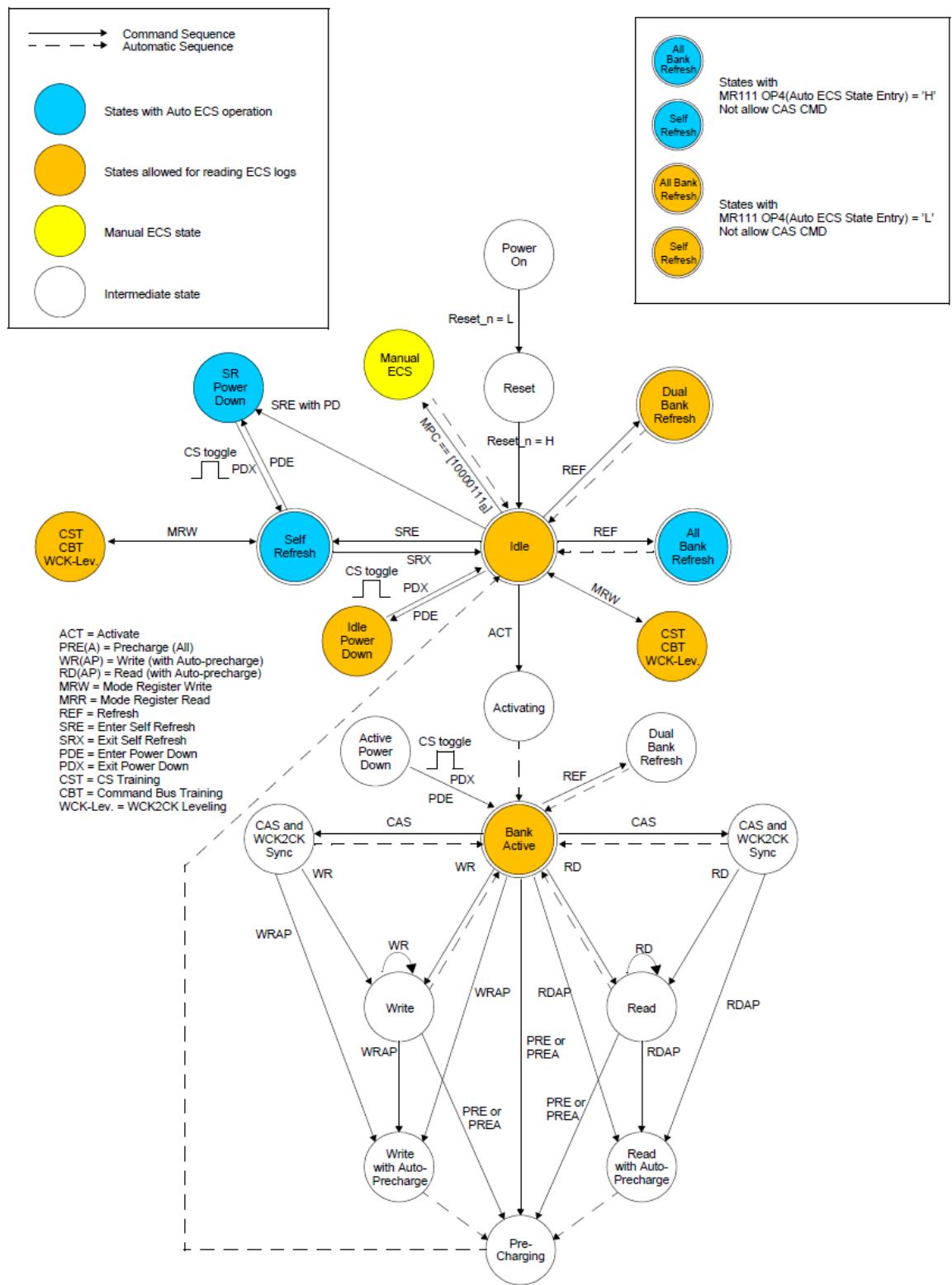

LPDDR6 SDRAM 状态图提供了允许状态转换及相关控制命令的简化示意图。要完整定义器件行为,需将状态图提供的信息与真值表和时序规范结合使用。

真值表为状态图提供了补充信息;当考虑所有 Bank 的实际状态时,它们阐明了设备行为及所施加的限制。

命令定义参见第4节“Initialization and Training”及第7节“Command and Operation”。

图46—LPDDR6:简化总线接口状态图

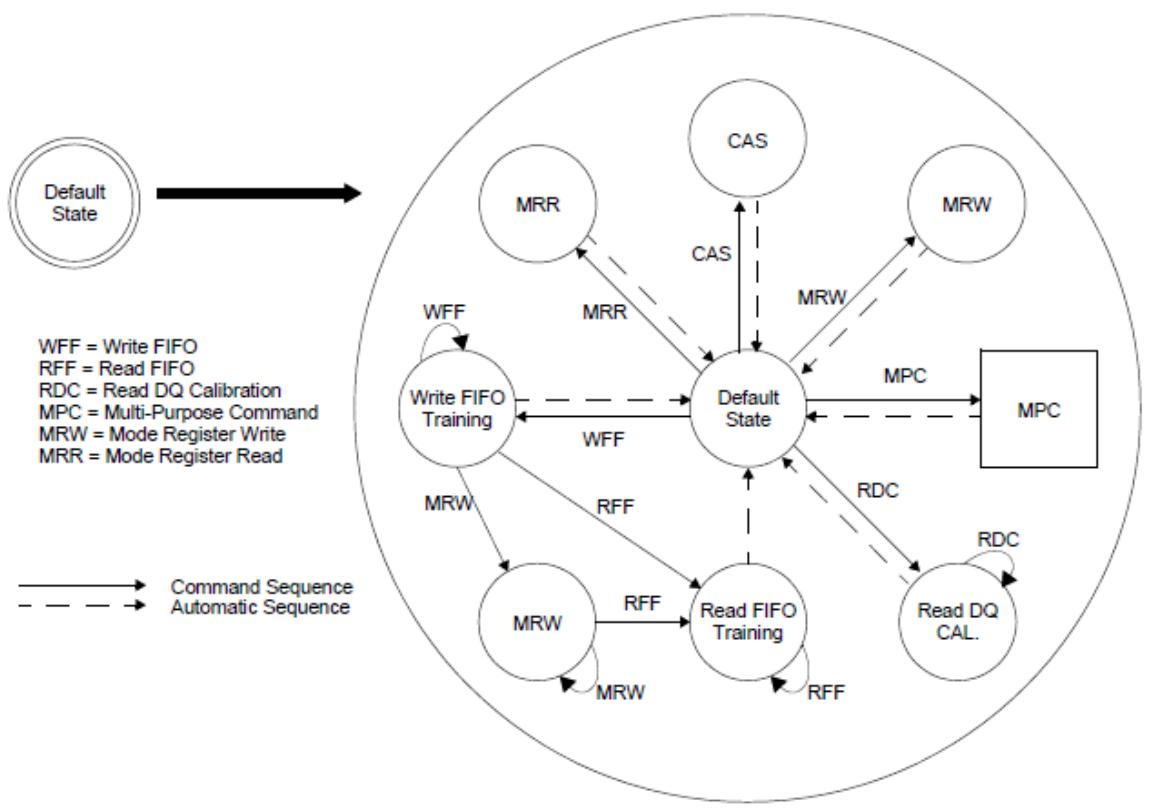

图47—与MRR、MRW、CAS、WFF、RFF、RDC及MPC命令相关的子状态图1

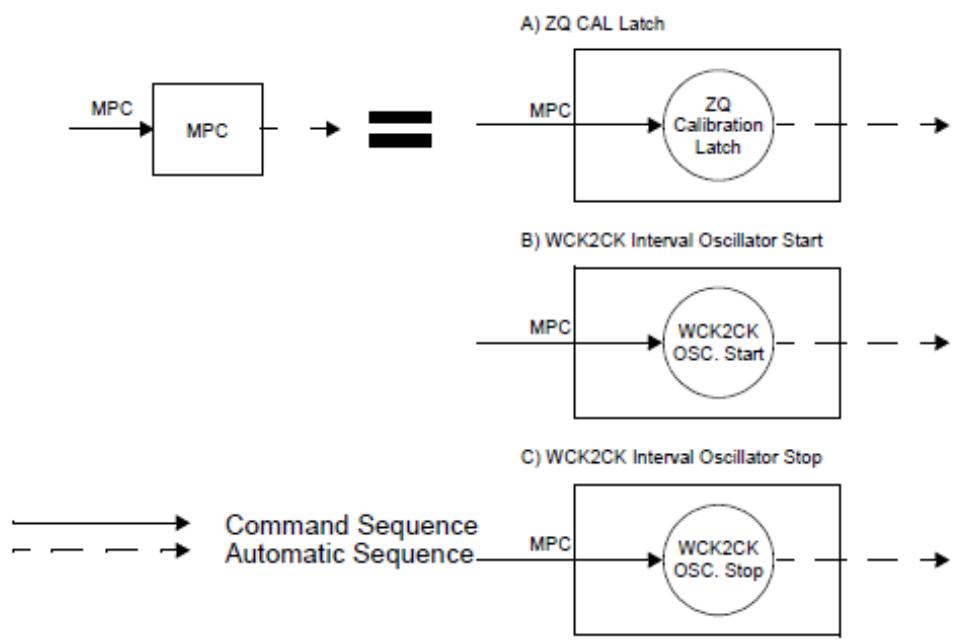

图48—子状态图2:与MPC状态相关

注1:从自刷新状态,设备可进入Power-Down、MRR、MRW和MPC状态。详见Self-Refresh的TBD获取更多信息。

注2:在IDLE状态下,所有banks均处于预充电状态。

注3:对于进入训练模式的MRW命令,状态机在训练结束时不会自动返回IDLE状态。更多信息请参阅关于ModeRegisterWrite(MRW)的TBD。

注4:对于进入训练模式的MPC命令,状态机在训练结束时可能不会自动返回IDLE状态。更多信息请参阅关于Multi-Purpose Command (MPC)的TBD。

注5:本简化状态图旨在概述可能的状态转换及控制命令。特别说明,涉及多bank的场景、片上端接使能/禁用状态以及其他某些事件未在此完整呈现。

注6:具有"automatic return"功能且可从多个先前状态(例如从Idle状态或Active状态发起MRW)进入的状态,将返回到其发起时的状态(例如从Idle状态发起的MRW将返回Idle状态)。

注7: RESET_n 引脚可从任何状态置为有效, 并将导致 SDRAM 进入复位状态。该图以上电时进入 RESET 状态为例, 但不应将该图理解为对 RESET_n 的限制。

注8:Bank Active 状态可根据需要进入 “CAS 和 WCK2CK Sync” 状态,以实现 WCK-to-CK 同步、非目标 ODT 设置或突发长度设置。

注9:"Bank Active"到"Per-2-Bank Refresh"的转换仅指不同 banks(而非同一 bank)。

注10:从WRITE FIFO命令到READ FIFO命令期间,仅允许执行针对MR13 OP[5:4]:FSP-WR、OP[7:6]:FSP-OP、OP[3]:VRCG以及MR14 OP[6:0]: VREF\mathrm{V}_{\mathrm{REF}}VREF (DQ[11:0])的MRW命令。

注11:LPDDR6支持专用CAS命令及WS=1的Read/Write操作以实现WCK2CK同步。从"Bank Active"状态进入"Read"/"Write"状态时需确保WCK2CK同步状态就绪。