GCC与Makefile常用基础知识

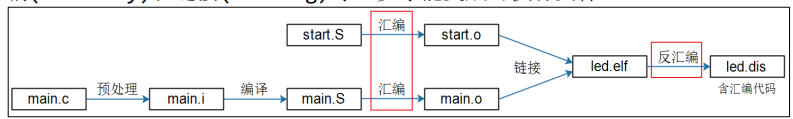

1.GCC编译过程

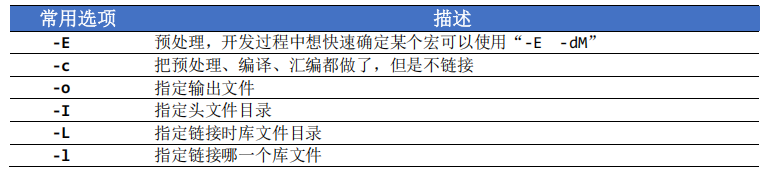

1.GCC常用编译选项

2.编译静态库选项参数

-fPIC

Makefile的使用

make 命令根据文件更新的时间戳来决定哪些文件需要重新编译,这使得可以避免编译已经编译过的、没有变化的程序,可以大大提高编译效率。

make规则

目标:依赖命令

Makefile常用函数

$(foreach var,list,text)

对 list 中的每一个元素,取出来赋给 var,然后把 var 改为 text 所描述

的形式。

例子:

objs := a.o b.o

dep_files := $(foreach f, $(objs), .$(f).d) // 最终 dep_files := .a.o.d .b.o.d

$(wildcard pattern)

pattern 所列出的文件是否存在,把存在的文件都列出来。

例子:

src_files := $( wildcard *.c) // 最终 src_files 中列出了当前目录下的所有.c 文件