多字节串口收发IP设计(一)概述

概述

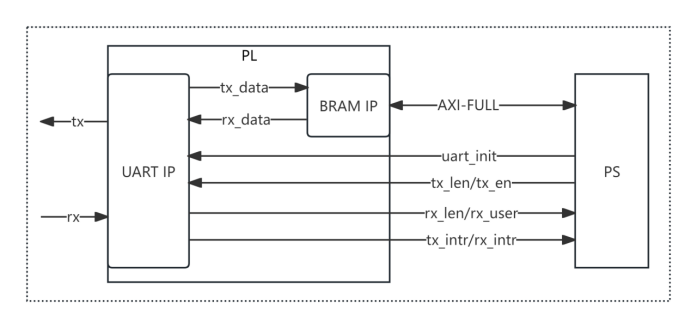

本项目实现了一个具有多字节收发功能的uart模块,并封装成一个具有AXI接口协议的IP模块,既可以用于ZYNQ平台实现PS控制PL端uart通信,也可以用于FPGA平台的uart通信。

项目来源于公司的一个大规模项目的uart收发模块,支持通过AXI协议配置uart的波特率、奇偶校验。

整个流程实现了高效、稳定的UART通信控制,确保了数据的完整性和实时性,适用于多种嵌入式应用场景。

收发工作流

Uart接收工作流

- PS进行IP初始化,通过AXI-Lite接口配置波特率、奇偶校验,并使能uart收发功能;

- IP接收到数据后缓存到FIFO1中,在接收完一帧数据后,将帧长度信息和校验错误信息缓存到FIFO2中;

- 判断FIFO2非空,读取FIFO1中数据写入到BRAM中,写入完成后产生中断信号到PS;

- PS接收到中断信号,通过AXI-Lite接口获取当前帧长度信息,并通过AXI-FULL接口将BRAM中数据读出并缓存/打印;

- PS清除中断标志并重新使能接收功能,等待下一次数据接收。

Uart发送工作流

- PS进行IP初始化,通过AXI-Lite接口配置波特率、奇偶校验,并使能uart收发功能;

- PS通过AXI-FULL接口将待发送数据写入到BRAM中,通过AXI-Lite接口将帧长度信息写入到IP中,并通知IP将BRAM中数据读出并发送;

- 发送完成后,产生中断信号到PS;

- PS接收到中断信号后,清除中断标志,准备下一次数据发送。

工作流框图