数字设计 综合工具 yosys 源码安装与应用简介

1. 下载源码

下载:

这样不能切版本:

$ git clone --recurse-submodules https://github.com/YosysHQ/yosys.git或者先切到 0.57版本,在clone 对应版本的 submodule:

$ git clone https://github.com/YosysHQ/yosys.git

$ cd yosys

$ git checkout v0.57

$ git submodule update --init --recursive2. 编译安装

make config-gcc

mkdir build

cd build/

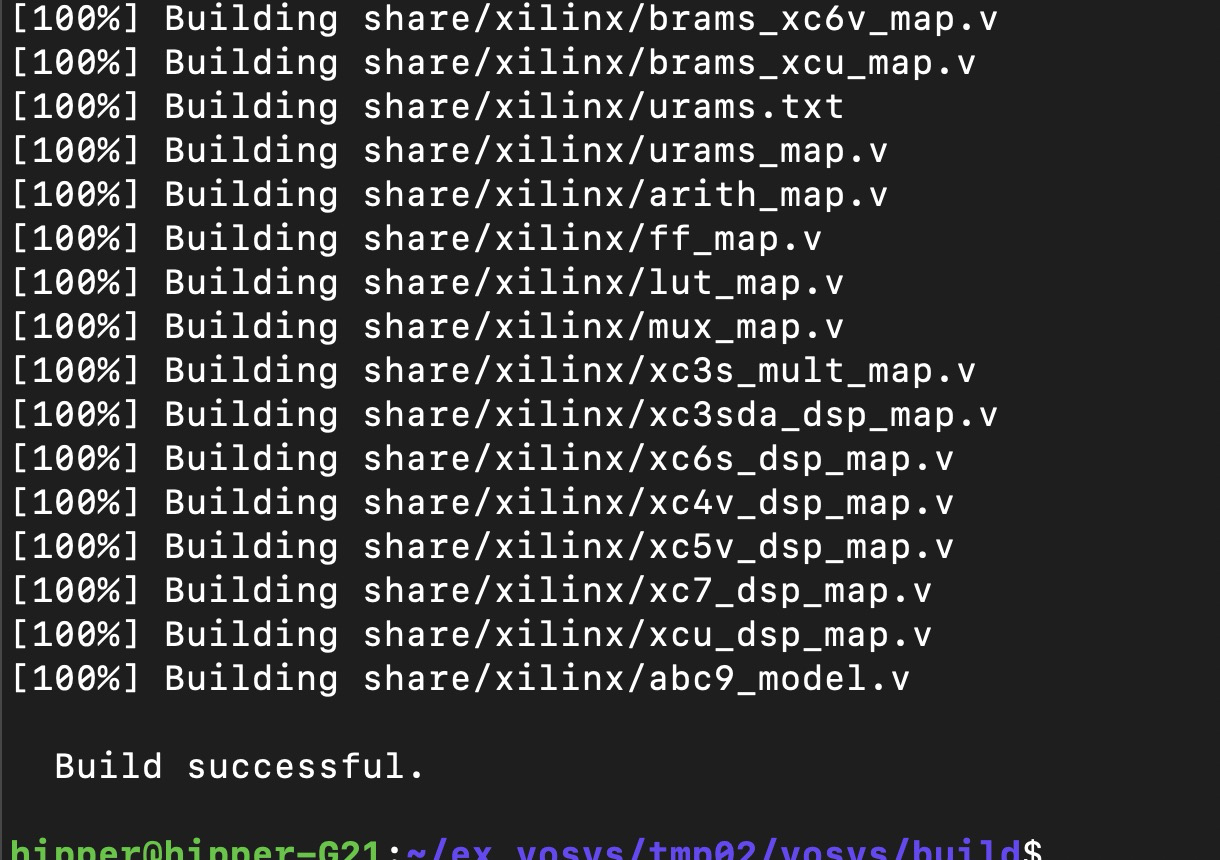

make -f ../Makefile

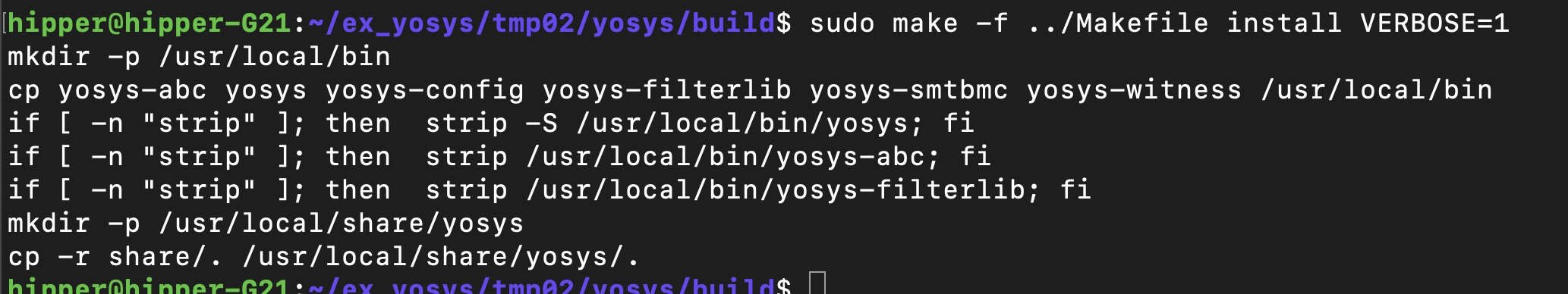

安装:

sudo make -f ../Makefile VERBOSE=1

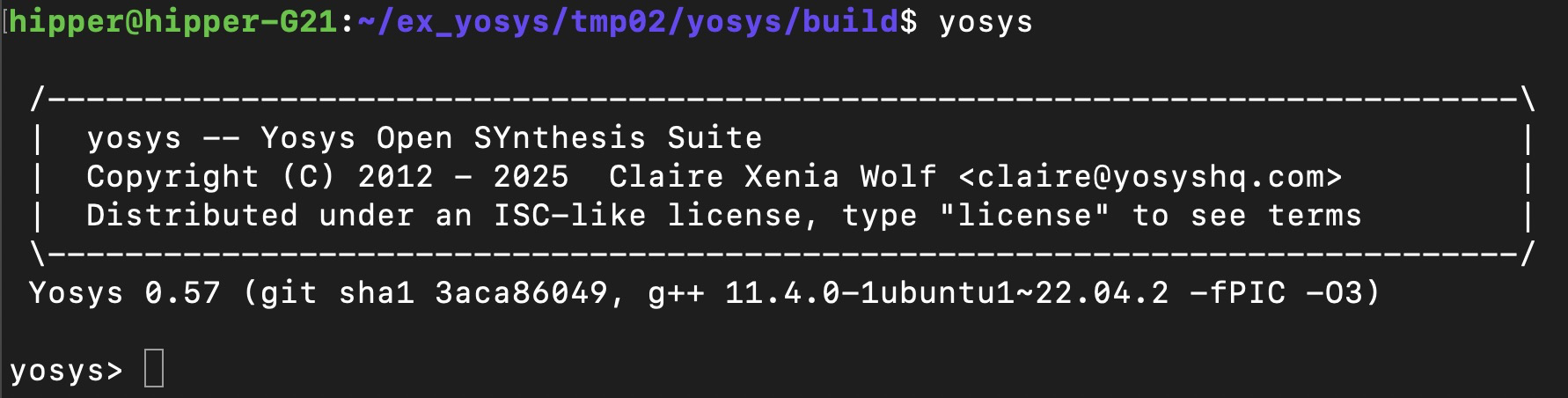

运行:

3. 综合一个module

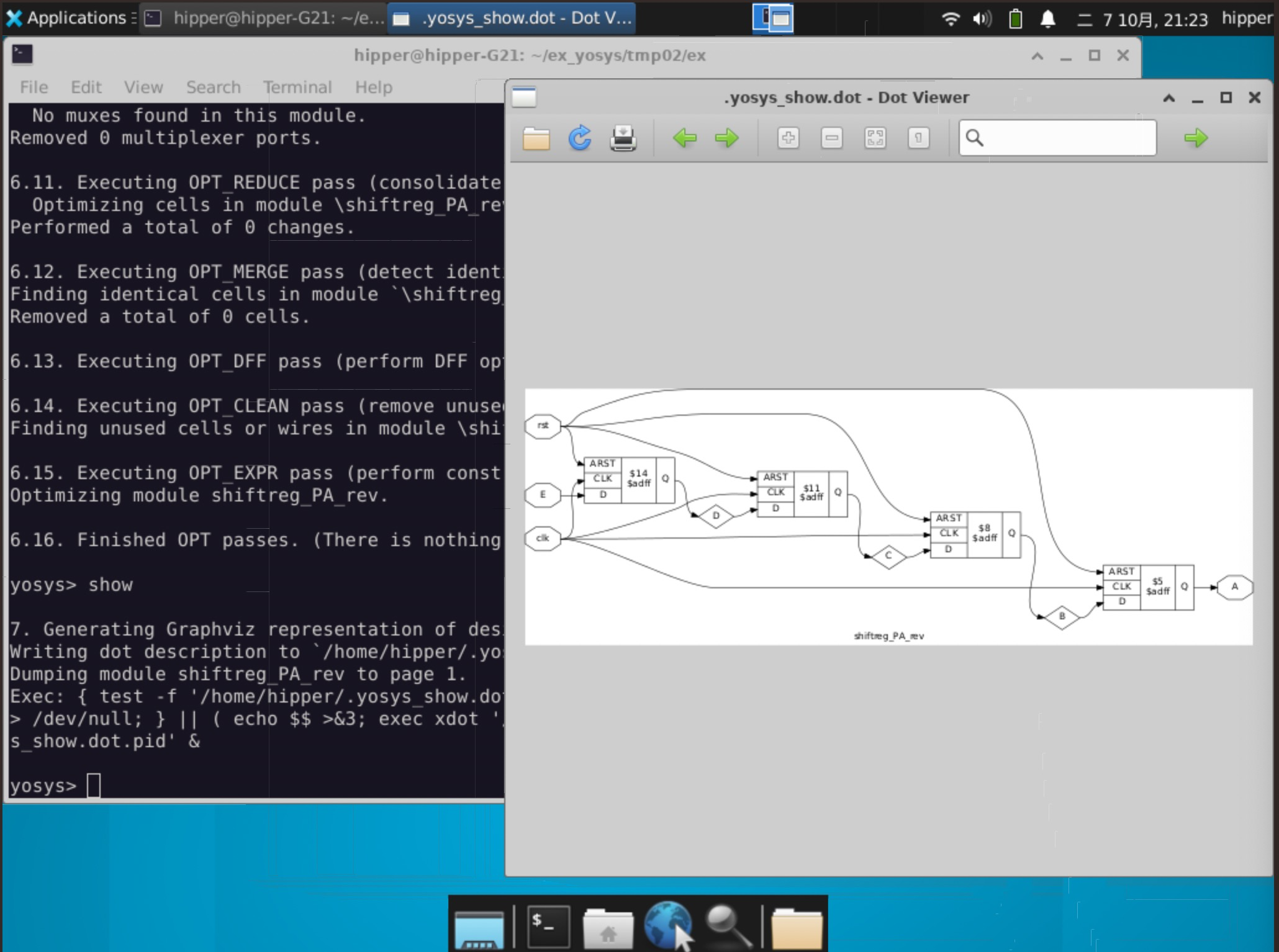

3.1. 一个4bit 的移位寄存器 module综合

shiftreg.v

module shiftreg_PA_rev(output reg A, input E, clk, rst);reg B, C, D;always @ (posedge clk, posedge rst) beginif(rst==1'b1)begin A=0; B=0; C=0; D=0; endelse beginA=B;B=C;C = D;D = E;endendendmodule综合:

yosys> help help

yosys> read -sv shiftreg.v

yosys> hierarchy -top shiftreg_PA_rev

yosys> write_rtlil

yosys> proc; opt

yosys> show显示如图:

3.2 官方示例

源文件:fiedler-cooley.v

// borrowed with some modifications from

// http://www.ee.ed.ac.uk/~gerard/Teach/Verilog/manual/Example/lrgeEx2/cooley.html

module up3down5(clock, data_in, up, down, carry_out, borrow_out, count_out, parity_out);input [8:0] data_in;

input clock, up, down;output reg [8:0] count_out;

output reg carry_out, borrow_out, parity_out;reg [9:0] cnt_up, cnt_dn;

reg [8:0] count_nxt;always @(posedge clock)

begincnt_dn = count_out - 3'b 101;cnt_up = count_out + 2'b 11;case ({up,down})2'b 00 : count_nxt = data_in;2'b 01 : count_nxt = cnt_dn;2'b 10 : count_nxt = cnt_up;2'b 11 : count_nxt = count_out;default : count_nxt = 9'bX;endcaseparity_out <= ^count_nxt;carry_out <= up & cnt_up[9];borrow_out <= down & cnt_dn[9];count_out <= count_nxt;

endendmodule需要在图形桌面上的 terminal 中完成:

yosys> help help

yosys> read -sv tests/simple/fiedler-cooley.v

yosys> hierarchy -top up3down5

yosys> write_rtlil

yosys> proc; opt

yosys> show

yosys> show -format ps -viewer gv

yosys> techmap; opt

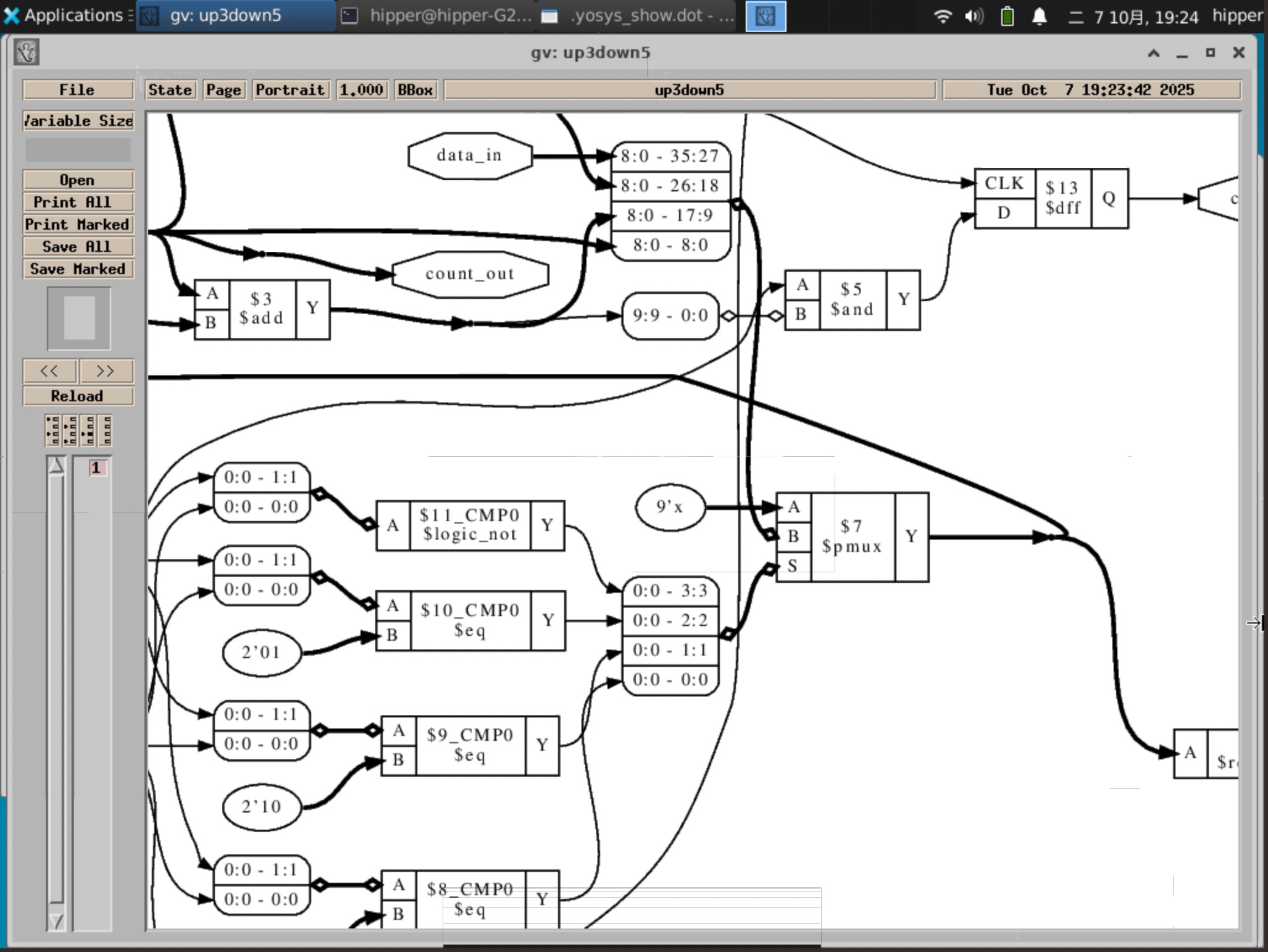

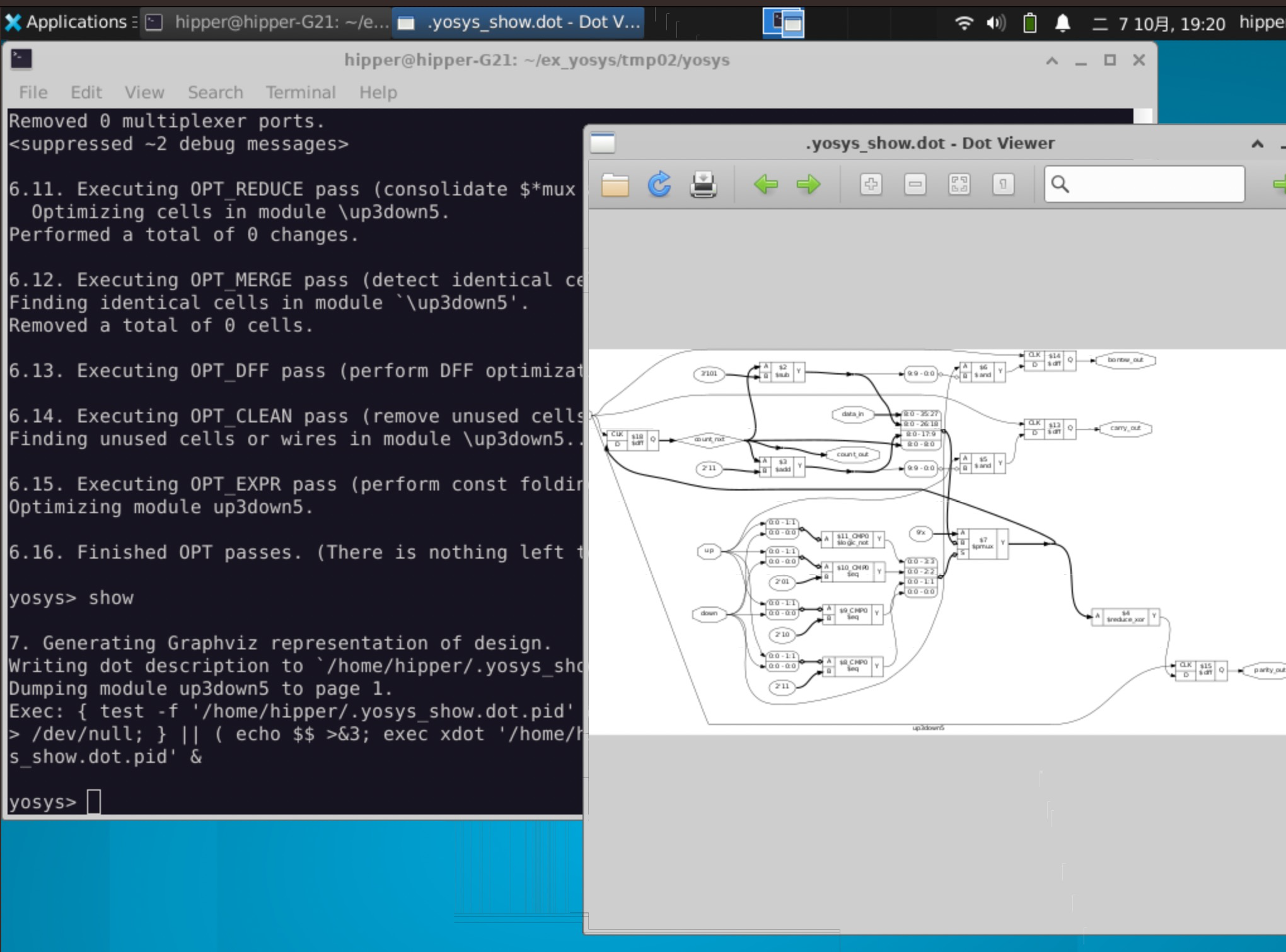

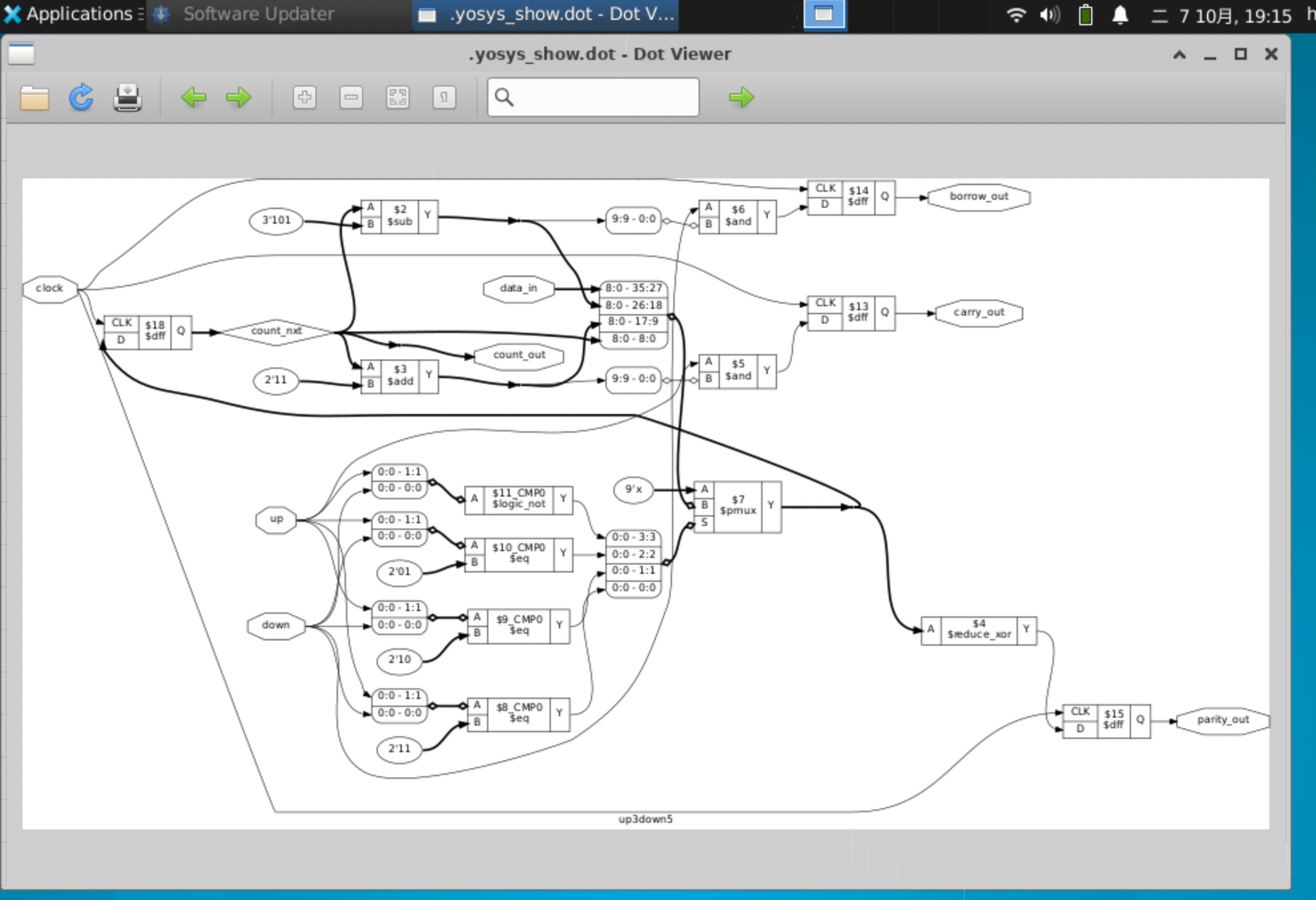

yosys> write_verilog synth.v运行到:yosys> show 显示如下:

运行到 yosys> show -format ps -viewer gv 显示如下,屏幕有点小: