Giants Shoulder - Samsung: LPDDR6 Key Architecture Share

带你看巨人视角下的LPDDR!

本期文档是来自三星的: LPDDR6 Key Architecture Share

这篇文章基于三星的这篇文稿对LPDDR6进行简要介绍,可以和上一篇Quick Look相互参考,更多的细节会在之后的LPDDR6 SPEC相关文章里分享。

前面对于LPDDR6的AI展望就不叙述了,从第六页开始,介绍了Low Power, High Performance, Additional Features三个方面的更新:

Low Power

增加了Ultra Low Supply Voltage和Dynamic Efficiency Mode

High Performance

信号从NRZ改为Wide-NRZ传输,还没有到PAM

提出了Sub-Channel的架构

Additional Features

PRAC安全防御功能,System Meta Bit

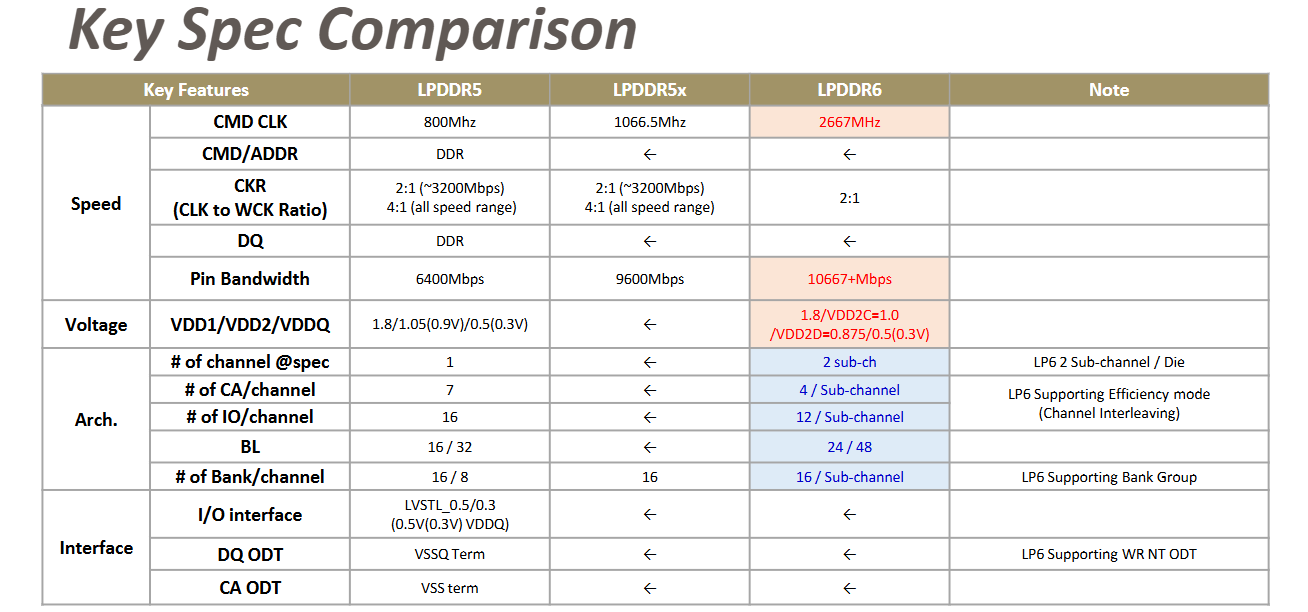

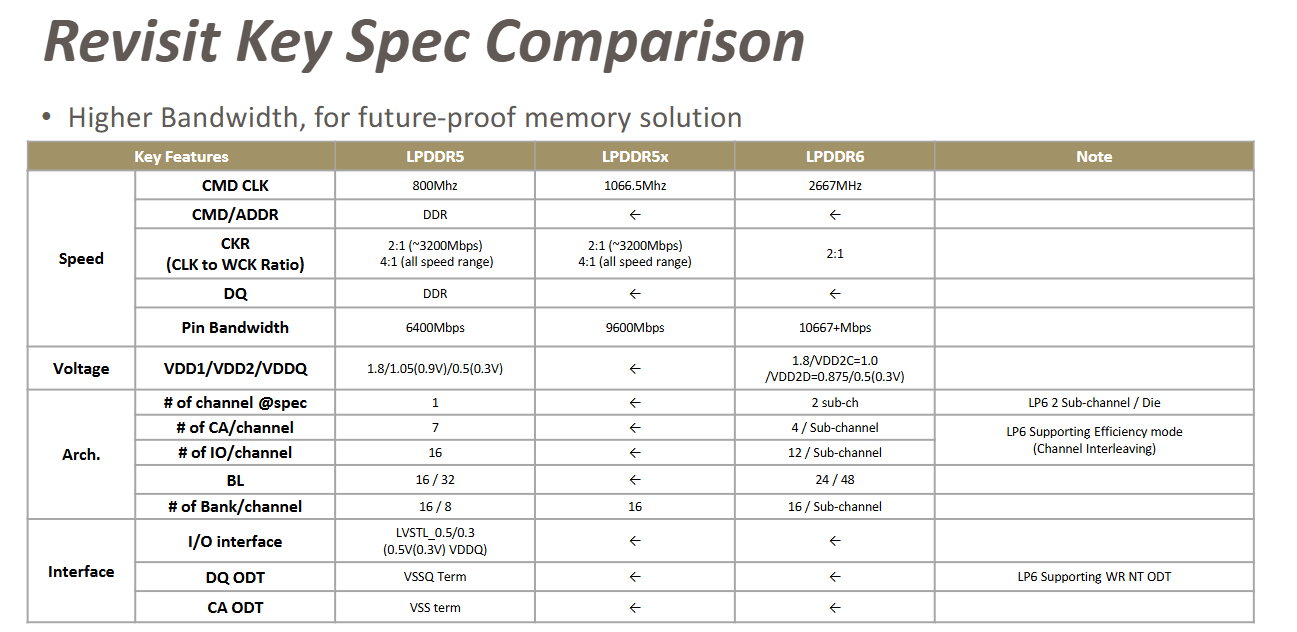

第七页提供了一个较为清晰的LP6和LP5在Speed/Voltage/Arch/Interface上的区别信息参考表格:

可以看到时钟频率几乎是2.5倍的提升,数据带宽也超过了10GMbps。

供电也是和之前文章中提到的一样,更低的供电,修改为VDD2C/VDD2D。

架构上主要就是Sub Channel的多样化选择,提供了Efficiency Mode。

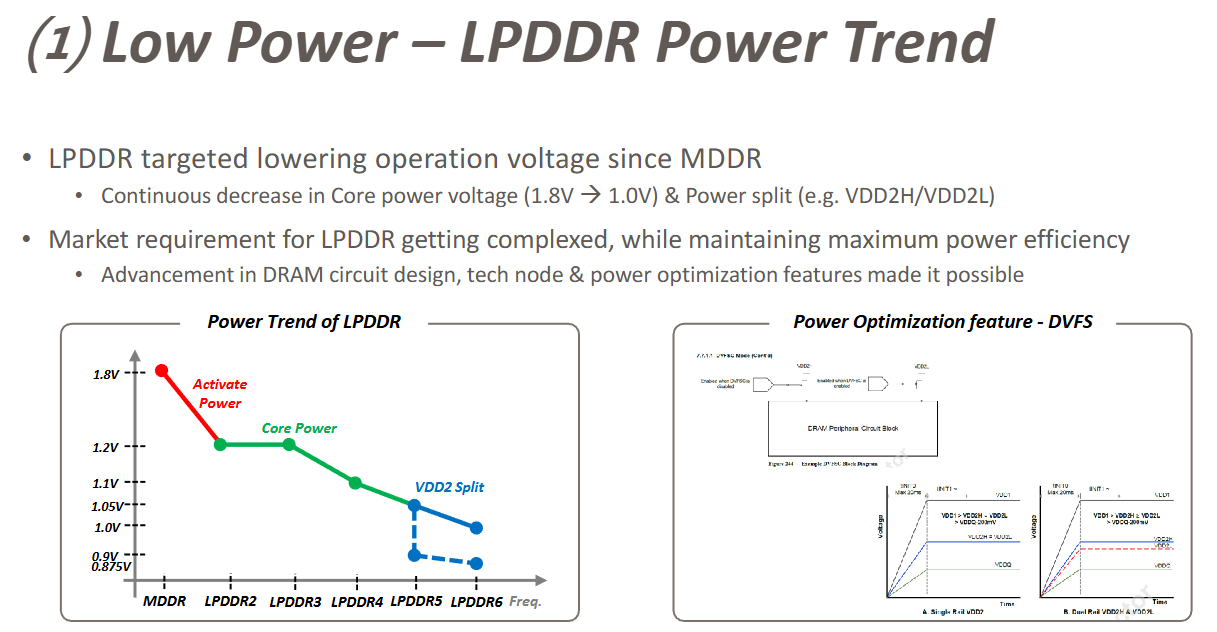

第八页开始Low Power部分的技术趋势介绍:

除了明显的Core Power Voltage功耗下降,比较突出的就是LPDDR5开始的VDD2拆分为2个Power Rail供电。

并且基于多Power Rail提出的DVFS给不同工作频率实现动态供电,达到比较高的供电效率。

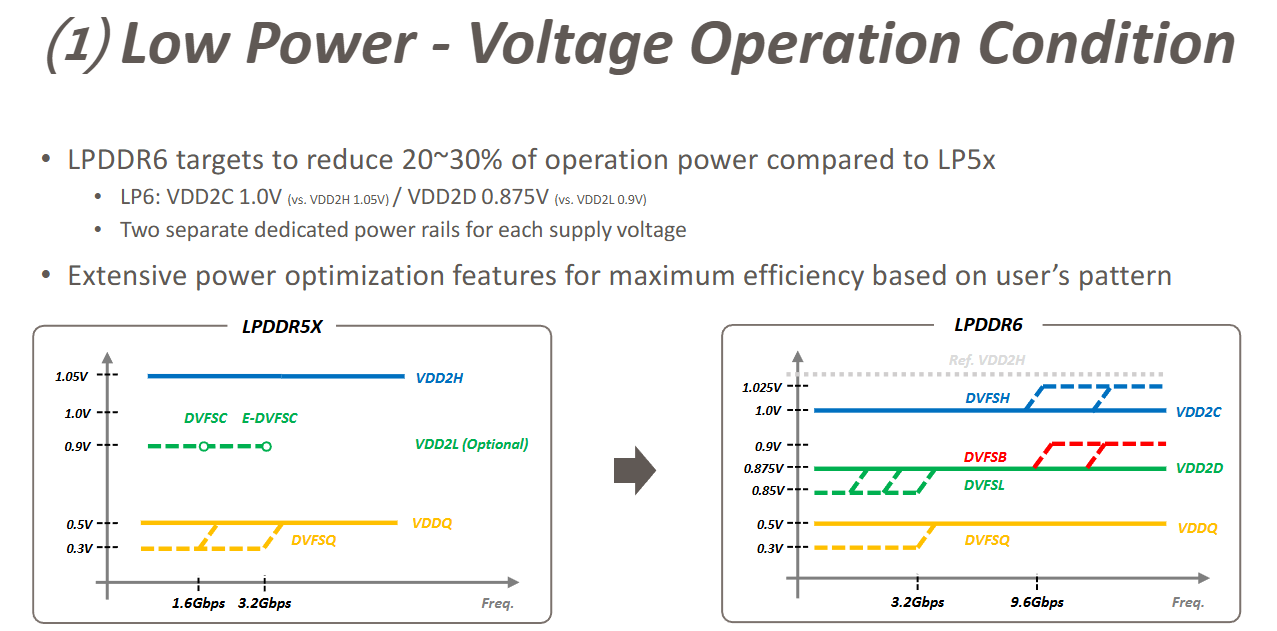

第九页还是围绕Low Power介绍,和上一代最强的LP5x比拼了下工作供电优劣:

从结果看,LP6的VDD2C/D电压低于LP5x的VDD2H/L,VDDQ还是保持了原有的供电设计。

DVFS也从VDD2L的DVFSC, E-DVFSC升级为VDD2C的DVFSH和VDD2D的DVFSB/L。

第十页不做过多介绍,大概就是提了一下Sub Channel架构能实现动态的高效供电。

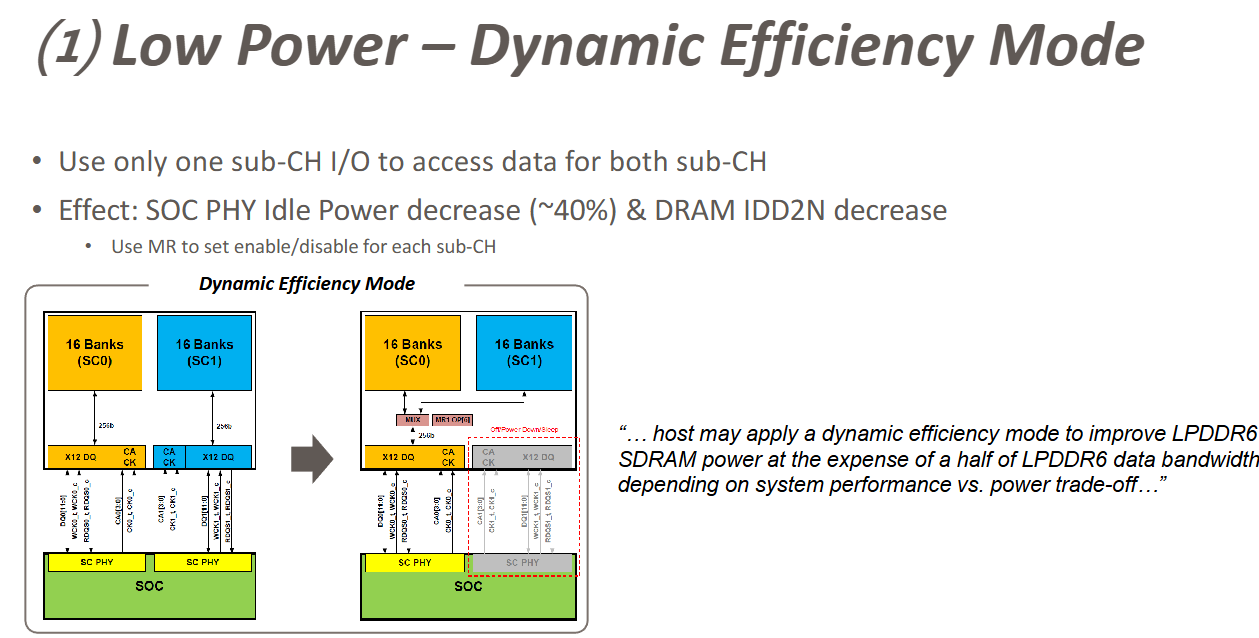

第十一页基于上一页的简单内容进行了更为详细的Sub-Channel架构介绍:

可以看到这种架构下SoC可以只通过一个Sub Channel的I/O去访问所有的Bank数据。

Host端只消耗一个PHY的硬件资源,节省了功耗,适合非高频数据访问的低功耗场景。

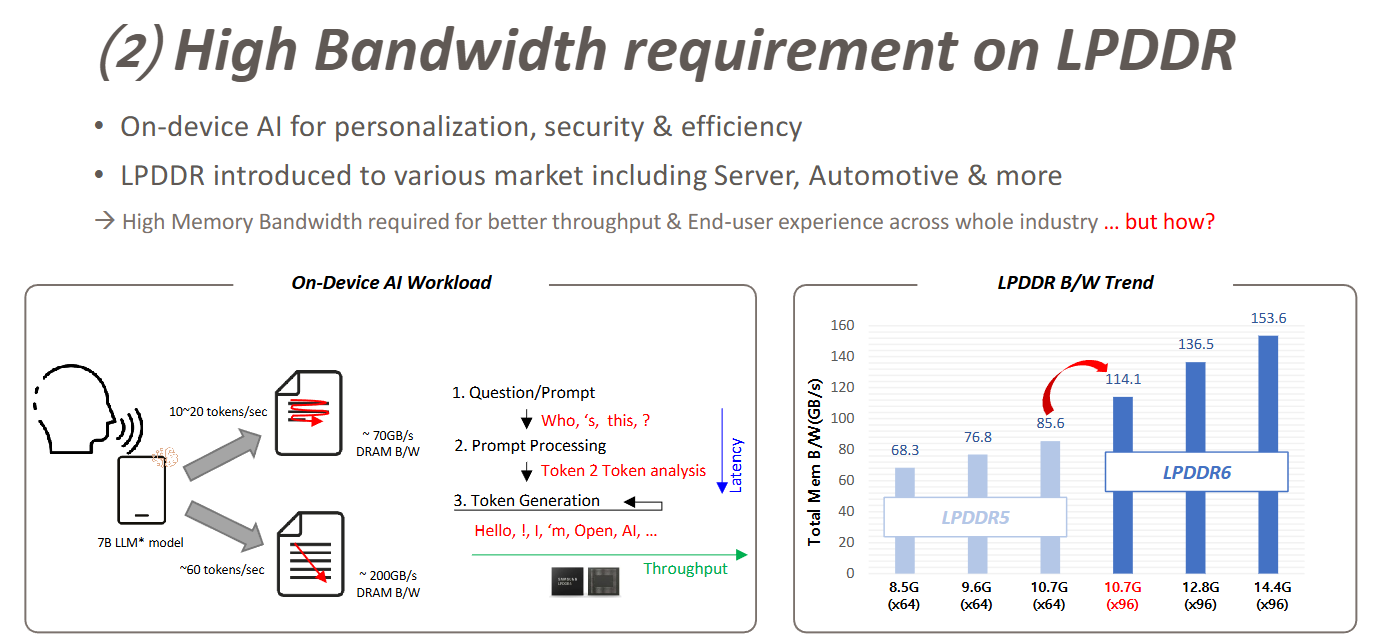

第十二页先从市场的角度介绍了LP6在带宽提升上的意义:

因为AI的技术发展,DRAM更高的带宽和速率能明显降低模型数据交互的延时。

服务器/汽车/边缘设备等应用市场也都需要LPDDR能够提供更高的带宽和速率。

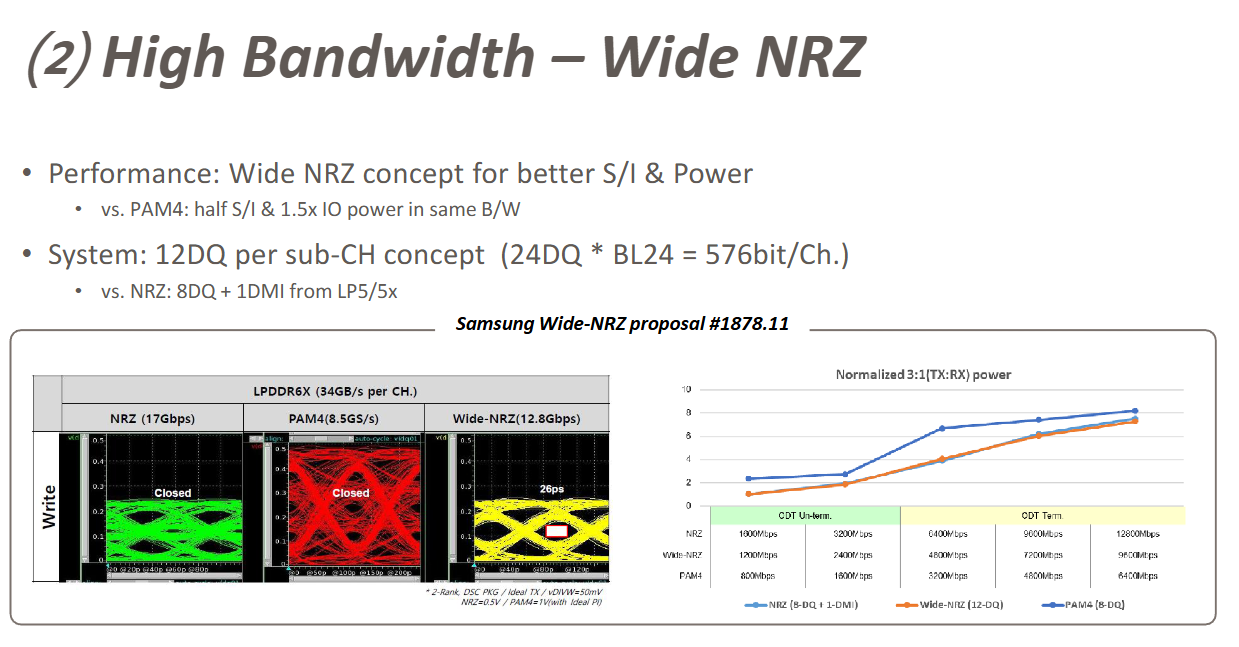

第十三页简单介绍了Wide NRZ技术:

34GB/s的高频速率下,对比NRZ (8DQ+1DMI)和PAM4 (8DQ), Wide-NRZ (12DQ)在Write Eye上的眼睛更宽阔一些,信号健壮性更好。

并且不论ODT开启还是关闭,Wide-NRZ信号传输功耗低于PAM4,与NRZ差不多,但传输速率略逊于NRZ。

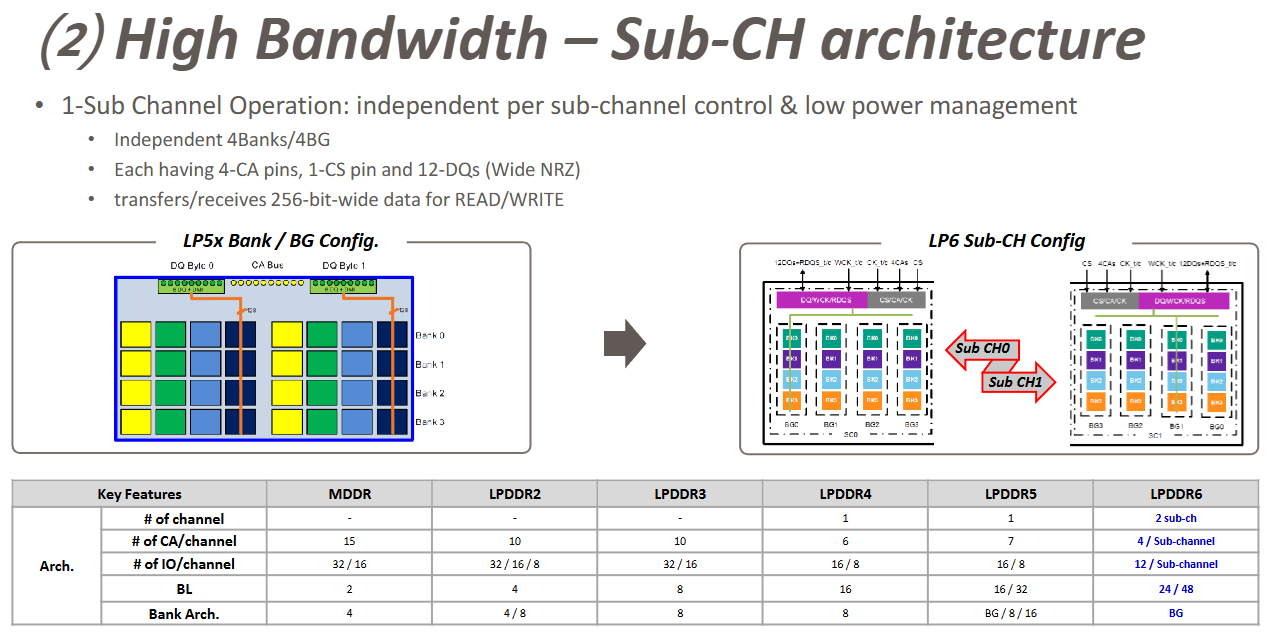

第十四页对比了和LP5x之间的Channel架构差异:

LP6上每个Sub-Channel都配备独立的控制单元和低功耗管理。

每个Sub-Channel都会由4个CA pin,1个CS pin和12个DQ。

第十五页提及了一下LPDDR各行各业的需求。

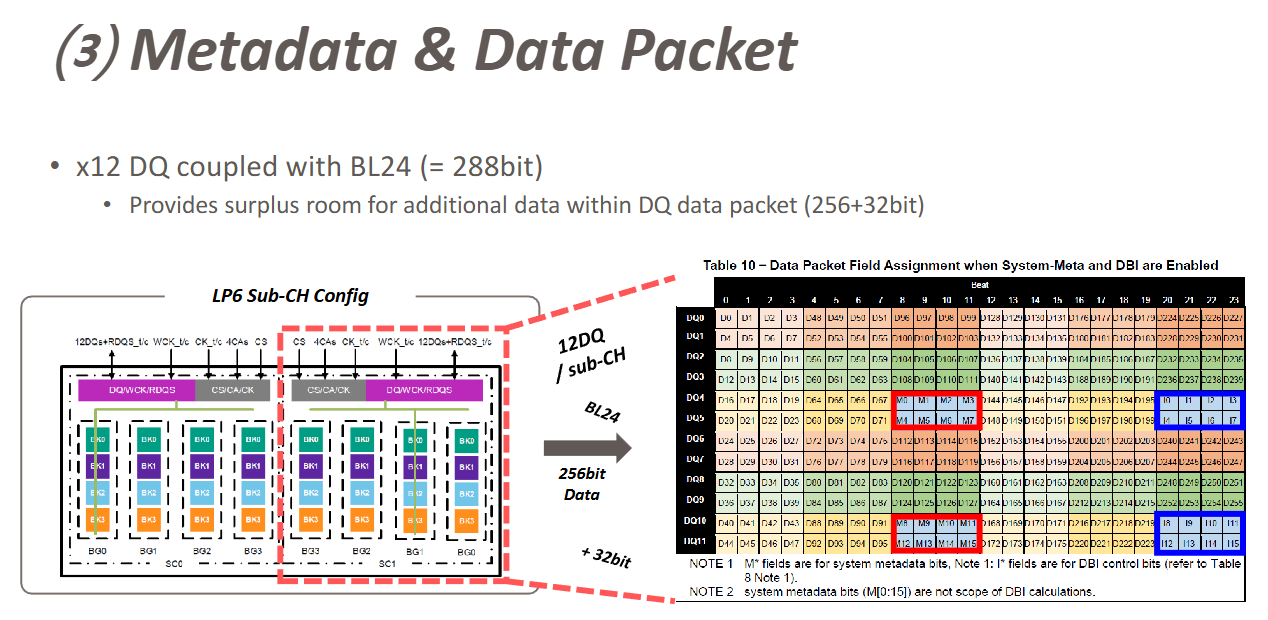

第十六页介绍了Metadata和单个数据包的结构“

从Per Sub-Channel的传输角度,看到每个Sub-Channel都配备专属的CA/CS/CK/DQ/WCK/RDQS。

一次BL24传输256 Data Bits + 32 Meta Bits = 24 Beats * 12 DQ Pins = 288 Bits.

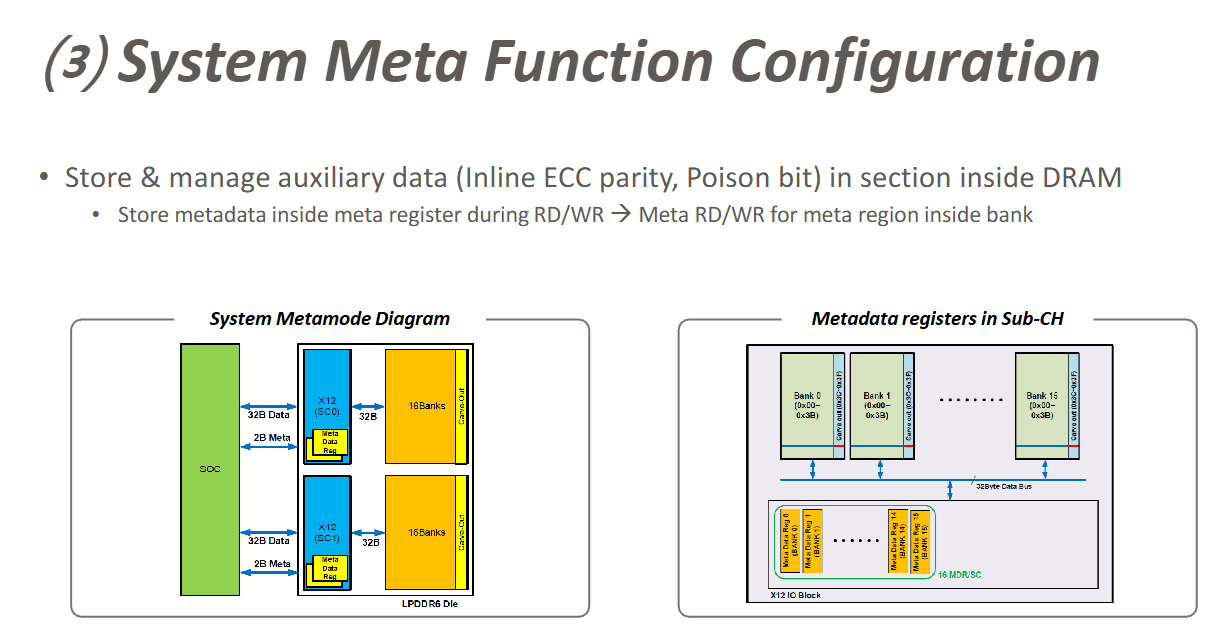

十七页介绍了下Meta相关的功能和配置:

Meta Bits相关功能主要是用于存储和管理一些DRAM内部辅助的数据,类似于校验和报警的信息。

DRAM内部也有专门存储Meta信息的区域,通过RD/WR Meta寄存器实现。

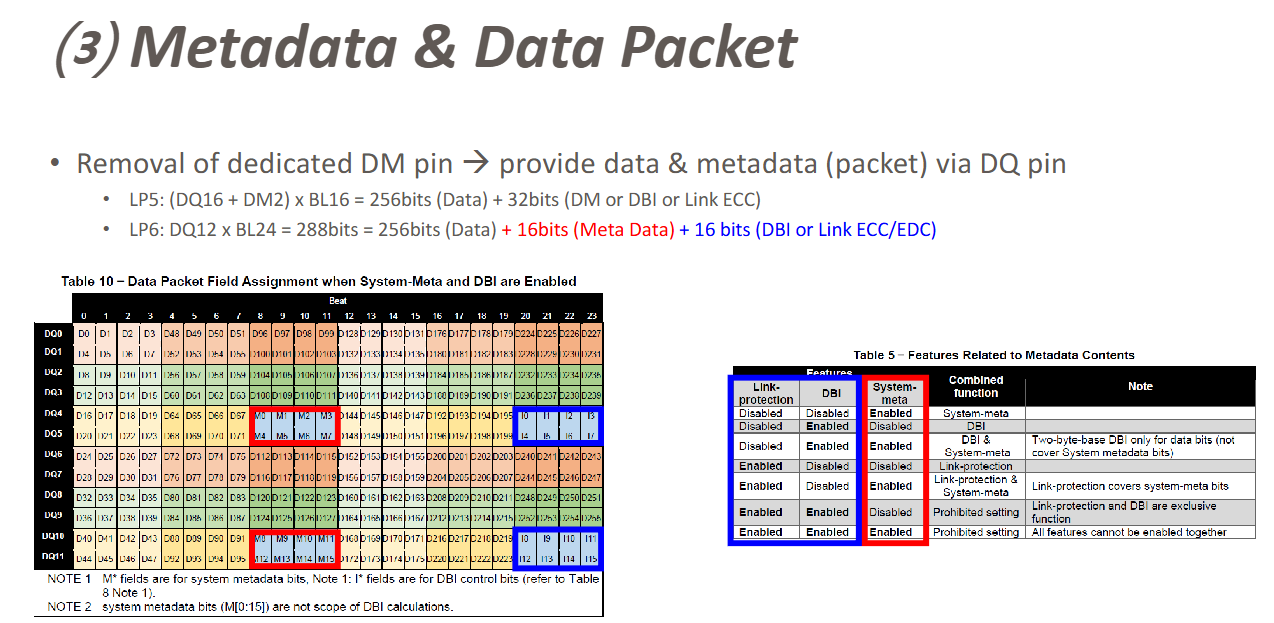

十八页依旧围绕Meta和Data Packet展开,对比了LP5的Data Pins:

可以看到32Bits Meta信息里,有16Bits用于DBI或者Link保护,剩下的16Bits携带System Meta数据,并且这些功能也存在某种互斥关系。

System Meta到底是什么类型的信息内容,会在之后的JEDEC标准中讨论。

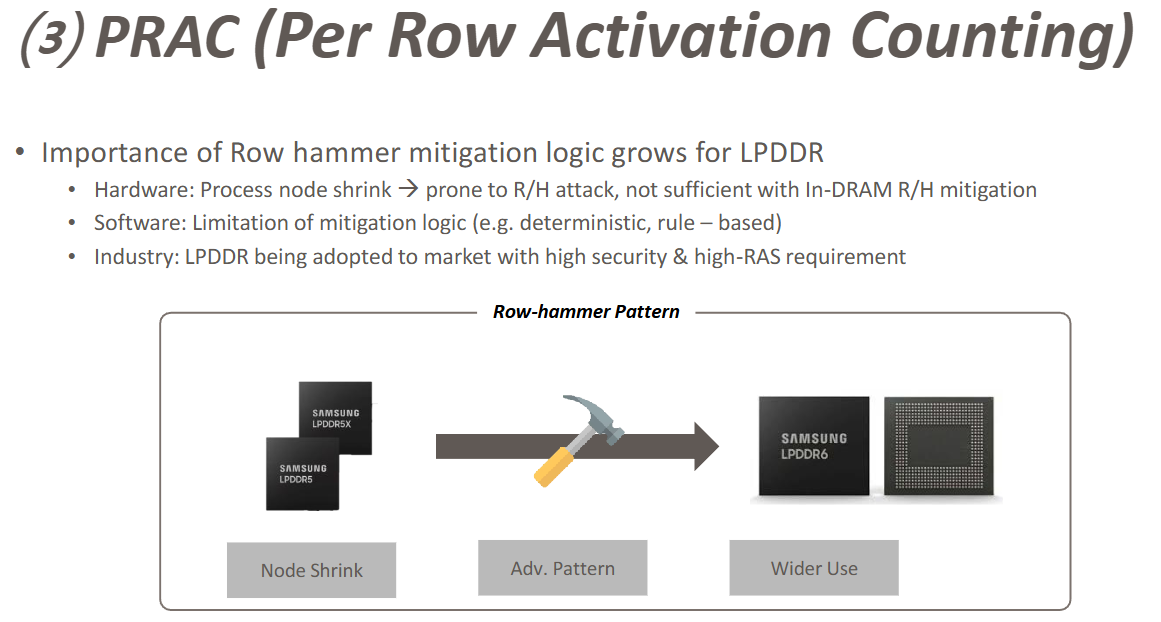

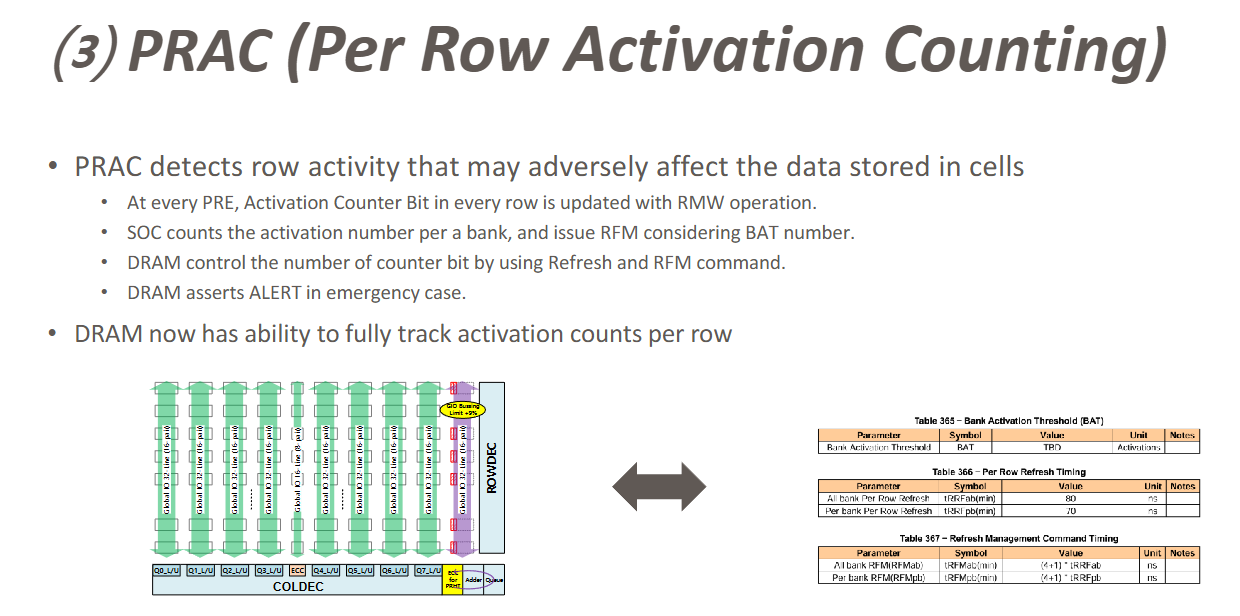

十九页提到了LPDDR首次引入的PRAC技术:

可以参考之前提到的DRAM Security的文章中的介绍,PRAC是为了防御RowHammer这类的攻击提出的防御措施。

应该是DDR5上已经使用过并且市场反馈还不错才引入LPDDR6的。

第二十页还是PRAC的内容:

简单讲就是从SOC对Per Bank的Count到发送RFM进化为监测Per Row的激活状态。更高的监测精度,更强的安全防御。

代价就是更多的硬件资源需要消耗,不过看起来LP6的工艺已经能满足此类消耗面积的硬件资源需求了。

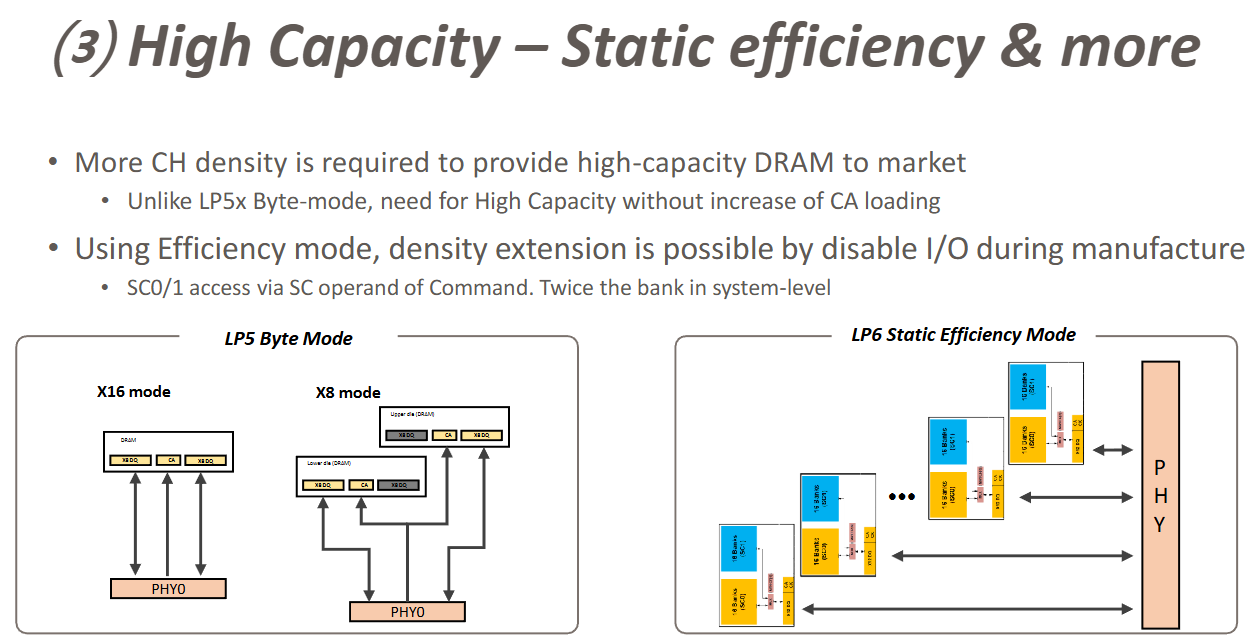

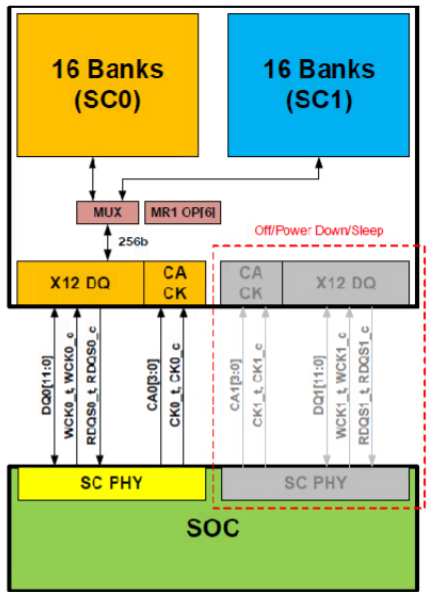

第二十一页提到了Static Efficiency的内容,LP6如何做到的高容量高效率:

首先PK了LP5的Byte Mode,不再需要增加CA的负载,就能访问更多的Bank。

不同于第十一页的动态Efficiency,这里是静态Efficiency,无法像Dynamic Efficiency Mode一样进行动态使用一个Sub-Channel或者两个Sub-Channel。

从图中看可以理解为SC0和SC1分别控制16 Banks,然后在静态Efficiency模式下,SC0和SC1共享一个Sub-Channel的I/O。

SoC通过SC Operand配合可以控制当前访问哪个Bank Region,在不增加物理资源的情况下扩展了访问的容量,有点像“虚拟通道”或“逻辑分区”的概念。

相比LP5确实减少了硬件资源消耗,不再需要区分Upper/Lower Die作CA共享。

但是增加了控制的复杂度,配合DRAM内部SC控制逻辑,共享一个Channel I/O。

最后的二十二页又重新回顾了LP6在对比LP5/LP5x上速率/功耗/架构的优势:

以上就是三星此篇关于LPDDR6文档的全部内容,算是简单快速了解了LP6的一些重要变化。和之前那一篇镁光的文章有很多相似之处。

更多LP6信息请继续关注后续的文章分享,谢谢!