时钟树的理解

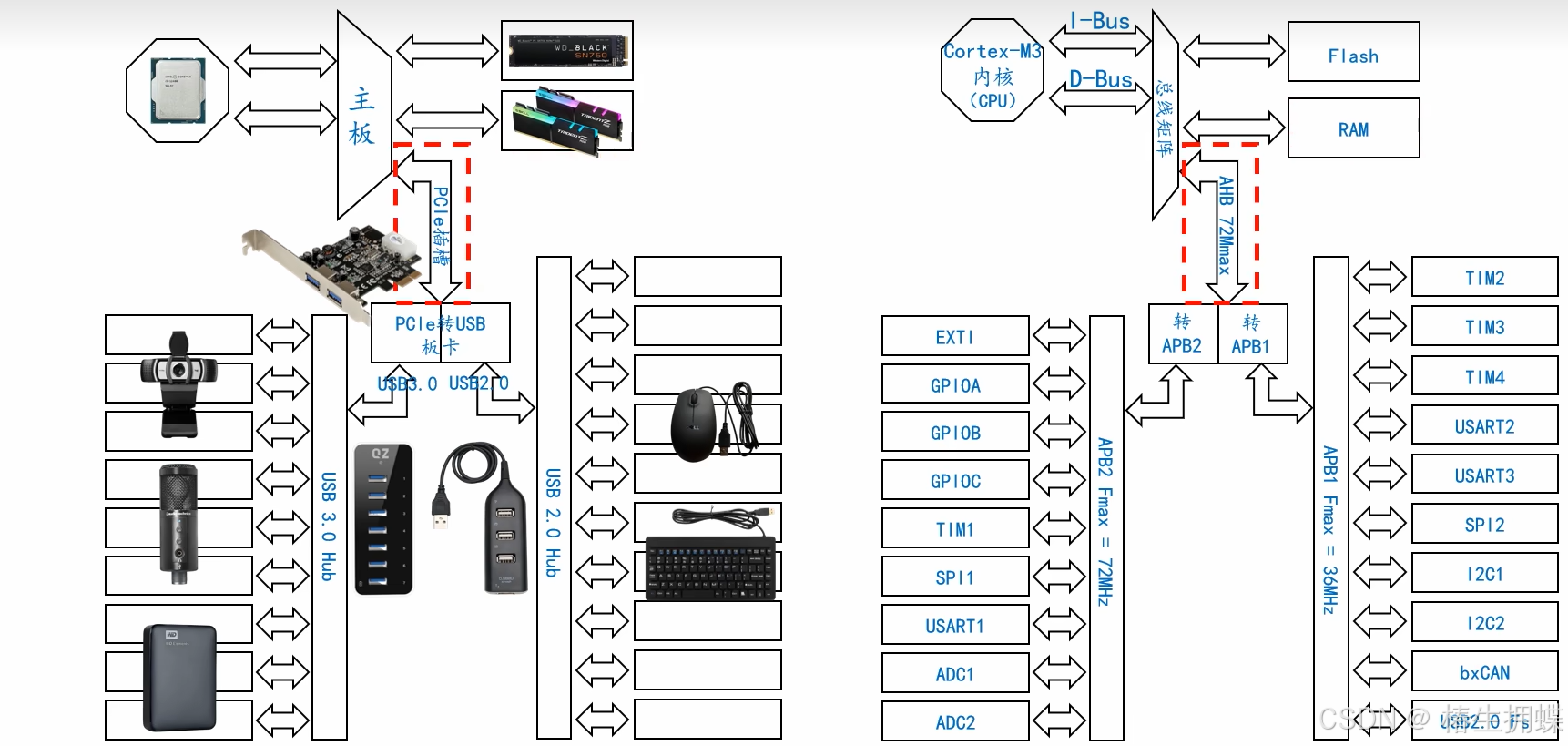

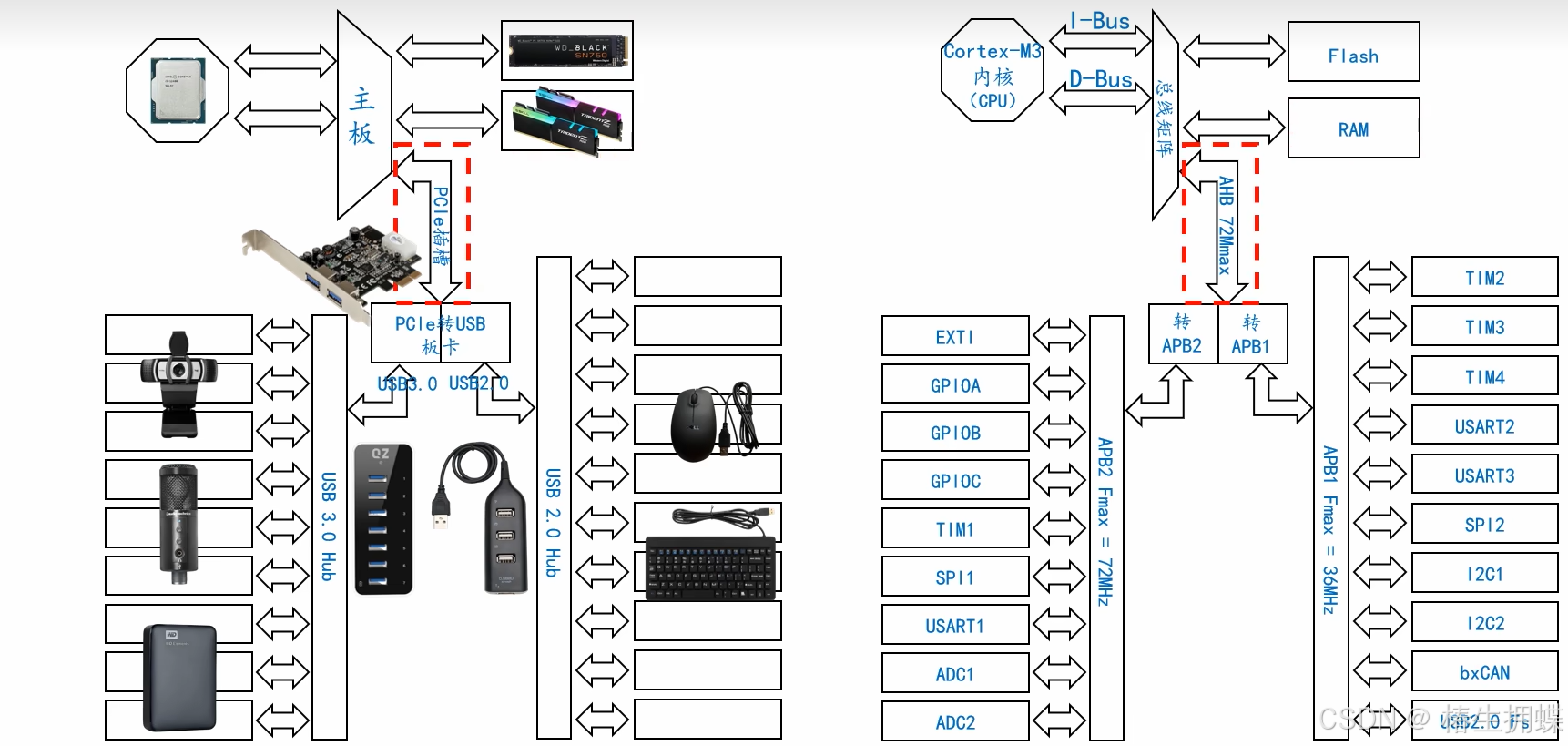

对应电脑的主板,CPU,硬盘,内存条,外设进行学习

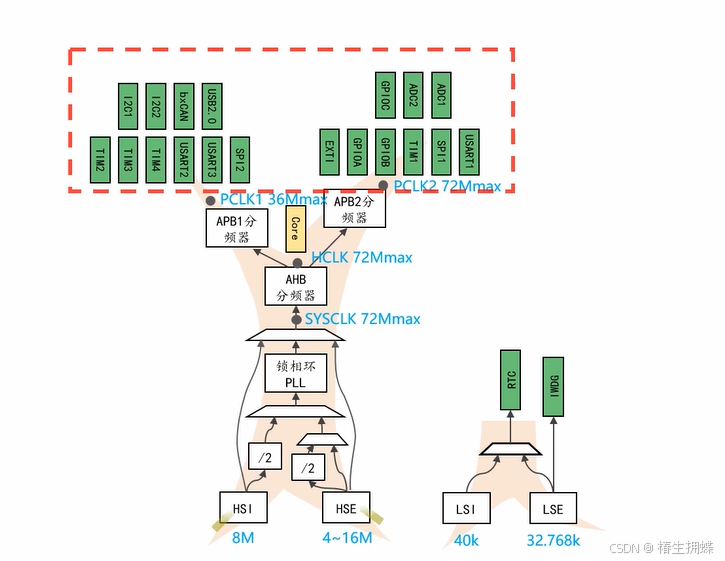

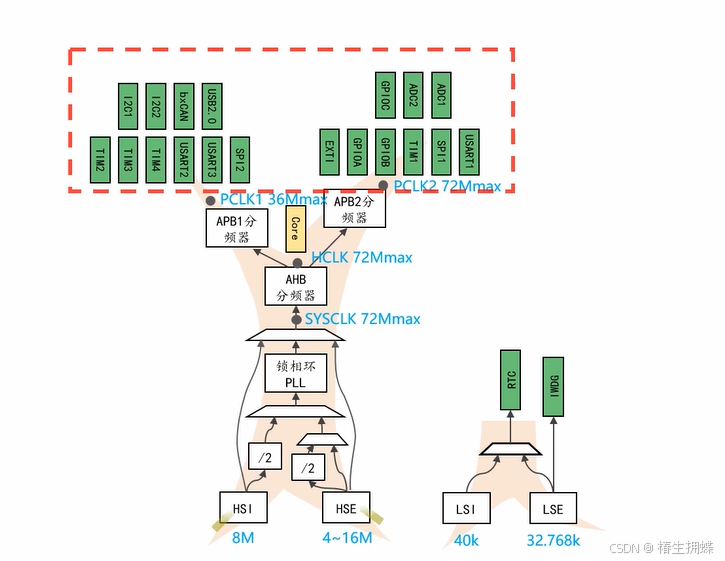

AHB总线 -72MHZ max APB1总线 -36MHZ max APB2-72MHZ max

时序逻辑电路需要时钟线控制 ,含有记忆性的原件的存在。(只有时钟信号才能工作)

由于APB1,和APB2挂载的外设,每个外设所需要的时钟频率不同,所以需要外部时钟,和内部时钟调节

LSI和HSI是芯片内部的RC振荡器。PLL是锁相环,通过锁相环可以对时钟频率进行倍频。

对应电脑的主板,CPU,硬盘,内存条,外设进行学习

AHB总线 -72MHZ max APB1总线 -36MHZ max APB2-72MHZ max

时序逻辑电路需要时钟线控制 ,含有记忆性的原件的存在。(只有时钟信号才能工作)

由于APB1,和APB2挂载的外设,每个外设所需要的时钟频率不同,所以需要外部时钟,和内部时钟调节

LSI和HSI是芯片内部的RC振荡器。PLL是锁相环,通过锁相环可以对时钟频率进行倍频。