PCIe协议之低功耗篇之 L1状态

一 背景介绍

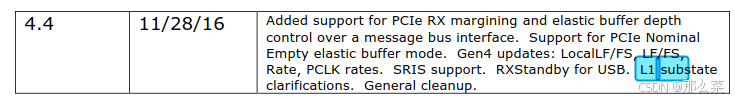

1.1 pipe spec v4.4 中 interface 说明

在本spec 版本的最后release 版本,协议组织增补了如下关于L1低功耗章节内容描述。

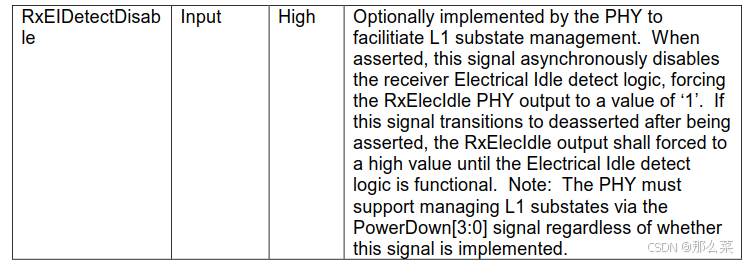

1.1.1 RxEIDetectDisable 接口信号

(该功能)可由物理层(PHY)选择性地实现,以更灵活方便地支持L1子状态管理。

当该信号有效时,它会异步禁用接收端电气空闲检测逻辑,强制将RxElecIdle物理层输出值置为‘1’。

若该信号在有效后转为无效状态,RxElecIdle输出必须保持高电平,直至电气空闲检测逻辑恢复功能。

注意:无论是否实现此信号,物理层都必须支持通过PowerDown[3:0]信号来管理L1子状态。

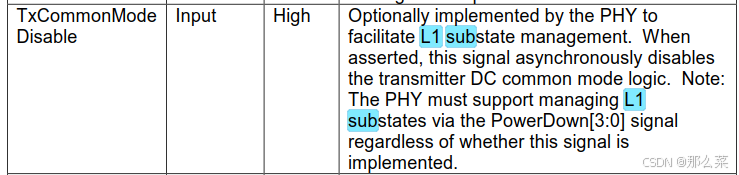

1.1.2 TxCommonModeDisable 接口信号

疑问1: PHY 发送端的 the transmitter DC common mode logic 是什么用途?

解答1: 发送端直流共模逻辑的核心用途是:在链路进入低功耗状态(如电气空闲)时,精确控制发送器的输出电平,并将其保持在一个稳定、确定的直流共模电压上。

1. 正常工作模式下的共模电压

在正常工作状态(L0)下,PCIe发送器通过交流耦合电容驱动差分信号。此时的“直流共模电压”是由发送器内部的电路(通常是一个精制的偏置电路)产生和维持的。这个电压必须被严格控制在一个特定的范围内(对于不同的PCIe代际,如Gen3/4/5,通常是~0V),以确保:信号摆幅正确;接收端的输入电路能工作在最佳线性区。

2. 低功耗状态下的关键作用

当链路需要进入低功耗状态(如电气空闲 Electrical Idle)时,情况就变了。此时的目标是停止发送数据,并将链路功耗降至最低。

“发送端直流共模逻辑”正是在此时被激活,它的主要职责是:

取代正常工作的电路:在电气空闲期间,关闭正常高速数据传输所需的大部分复杂电路(如串行器、驱动器的主电流源等),以节省功耗。

提供一个简单、稳定的直流电平:该逻辑会接管控制,并强制发送器的差分输出端(TX+和TX-)输出相同的直流电压。由于两端电压相同,差分电压为0,这意味着没有信号在传输,从而实现了“电气空闲”。

确保接收端能可靠检测:这个被强制输出的直流共模电压必须在一个接收器可以明确识别的范围内。接收器有“电气空闲检测电路”,它会监测差分电压和共模电压。当它检测到差分电压持续为0,并且共模电压处于预期的“空闲”电平,就会确认链路已进入电气空闲状态。

维持通道终端:即使在空闲状态,它也需要维持一个基本的输出阻抗,以匹配传输线的特性阻抗,防止信号反射。

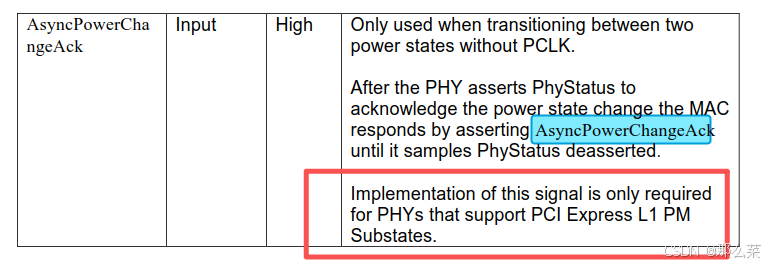

1.1.3 AsyncPowerChangeAck 接口信号

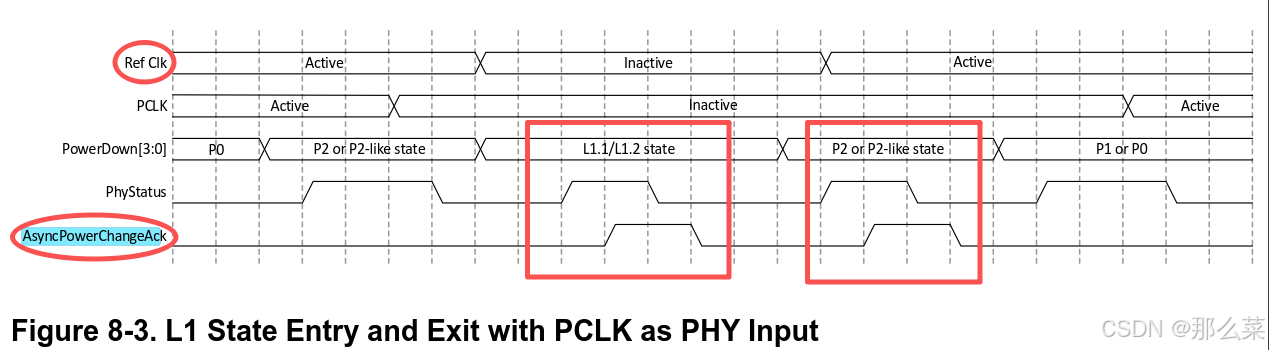

该信号用于支持 L1 substate 状态的场景。

When transitioning out of a state that does not provide PCLK to another state that does not

provide PCLK, the PHY asserts PhyStatus as soon as the PHY state transition is complete and

and leaves it asserted until the MAC asserts AsyncPowerChangeAck. Once the MAC asserts

AsyncPowerChangeAck the PHY deasserts PhyStatus.

当从不提供PCLK的Power 状态转换到另一个也不提供PCLK的Power 状态时,物理层在完成状态转换后立即置位PhyStatus,并保持该信号有效,直至MAC置位AsyncPowerChangeAck。一旦MAC置位AsyncPowerChangeAck,物理层便取消置位PhyStatus。

1.2 pipe spec v4.4 中 pcie power management 说明

P0状态:物理层(PHY)中的所有内部时钟均处于运行状态。P0是物理层唯一能够发送和接收PCI Express信令的状态。对于链路训练和状态状态机(LTSSM)中的大多数状态。

P0s状态:PCLK必须保持运行。MAC仅可在发送通道空闲时将物理层移至此状态。当发送器处于Tx_L0s.Idle状态时,可使用P0s状态。当物理层处于P0或P0s电源状态时,若接收器检测到电气空闲,则物理层的接收部分可采取适当的节能措施。注意:在接收通道恢复信令传输时,物理层必须能够在物理层规定的时限内(N_FTS,无论是否采用公共时钟)实现位锁定与符号锁定。此要求仅当接收器先前在P0或P0s状态下已实现位锁定与符号锁定时适用。

P1状态:物理层中的选定内部时钟可被关闭。PCLK必须保持运行。MAC仅当发送与接收通道均空闲时,才会将物理层移至此状态。物理层在PCLK稳定且运行直流共模电压稳定并符合规范要求(依据基础规范)之前,不得指示成功进入P1状态(通过置位PhyStatus)。P1状态可用于LTSSM的Disabled状态、所有Detect状态以及L1.Idle状态(仅在不支持L1子状态时使用)。

P2状态:物理层中的选定内部时钟可被关闭。并行接口处于异步模式且PCLK被关闭。P2状态可用于LTSSM的L1.Idle、L2.Idle及L2.TransmitWake状态。

1.3 pipe spec v4.4 中 L1 substate进入或退出说明

为实现L1子状态进入,物理层必须支持一种可禁用PCLK、可移除REFCLK,且保持接收端电气空闲与发送端共模电压有效的状态;该状态可以是P2或类P2状态。

图8-3展示了进入和退出L1子状态的可能转换过程。P2或类P2状态对应LTSSM中的L1.Idle状态;

PhyStatus和AsyncPowerChangeAck信号的使用方式遵循本章节前述规范。

2.1 pipe spec v4.4.1 中 interface 说明

作为对本节前述内容的替代方案,物理层可采用单一的PowerDown[3:0]编码,并辅以RxEIDetectDisable和TxCommonModeDisable信号来实现L1子状态管理。使用不同的PowerDown[3:0]编码来定义L1子状态,可灵活指定不同的退出延迟;而使用RxEIDetectDisable和TxCommonModeDisable信号则...

二 L1 状态管理机制

L1子状态管理机制:物理层需报告其支持以下哪种L1子状态管理机制:

完全通过PowerDown[3:0]信号进行管理(结合asyncpowerchangeack握手)

通过RxEIDetectDisable和TxCommonModeDisable信号进行管理

同时支持上述两种机制