ARM--时钟管理单元与定时器

一、时钟管理单元

1、概述

时钟管理单元

是嵌入式系统(如ARM架构芯片)中负责生成、分配和调控时钟信号的核心模块

主要功能

倍频/分频:通过锁相环、分频器组合生成不同频率的信号

时钟分配:为CPU、总线、外设等提供独立时钟

2、组成模块

- 时钟源:晶体振荡器,产生稳定的震荡,作为系统运行时的频率(主频)

- PLL:锁相环电路,用于实现倍频功能的特殊电路

- PFD:相位分数分频器,可实现非整数分频,输出精确灵活的时钟信号,也可用于多路适中的生成

- 分频器:分频(降低输入频率)

3、时钟配置

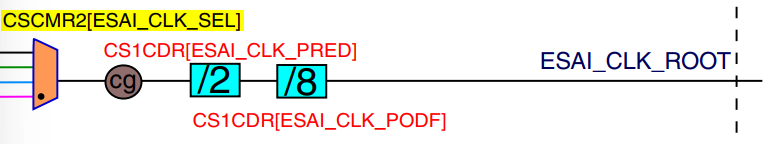

以下图为例,时钟源配置过程如下

- 通过配置 CSCMR2 寄存器选择时钟源

- 通过配置 CS1CDR 寄存器蛇者分频系数,从而得到目的频率的时钟信号

二、定时器

1、EPIT

1.概述:

EPIT是专为周期性中断定时设计的32位向下计数定时器

EPIO 定时器通常支持三种时钟源选择

EPIO仅支持定时中断功能,不具备输入捕获、PWM输出等特性,适用于精准时间控制

2.结构组成

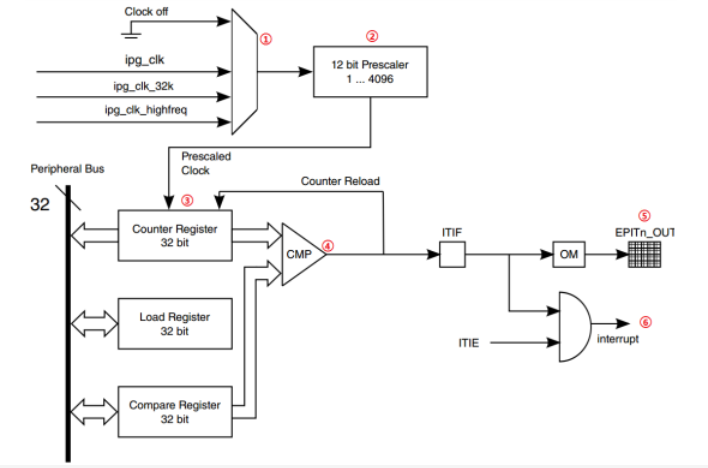

EPIO 定时器结构如下图,图中各个部分为:

①:多路选择器,用来选择 EPIT 的时钟源

②:十二位分频器,负责对时钟源信号进行分频

③:Counter Register:计数寄存器,保存当前计数值,在使能计时器工作后,计数寄存器从预设值开始自减,当预设值减少到0或者比较值,触发中断

Load Register:加载寄存器,在set-and-forget工作模式下,当计数寄存器中数据减到零时,会加载加载寄存器中的数据从新开始自减

Compare Register:比较寄存器,存放比较值

④:比较Compare Register与Counter Register的值,如果相等的话产生比较事件

⑤:可以指定引脚输出信号

⑥:用于产生比较中断

3.工作模式

set-and-forget:

在此模式下 EPIT 的计数器从加载寄存器 中获取初始值,不能直接向计数器寄存器写入数据。不管什么时候,只要计数器计数到 0,那么就会从加载寄存器中重新加载数据到计数器中

free-running :

此模式下,当计数器计数到 0 以后会重新从0XFFFFFFFF 开始计数,并不是从加载寄存器 中获取数据

2、GPT

1.特点

- GPT 是周期性中断 32 位向上计数定时器,通常有多种时钟源可供选择

- 支持中断、输入捕获以及 PWM 输出等功能

2.结构组成

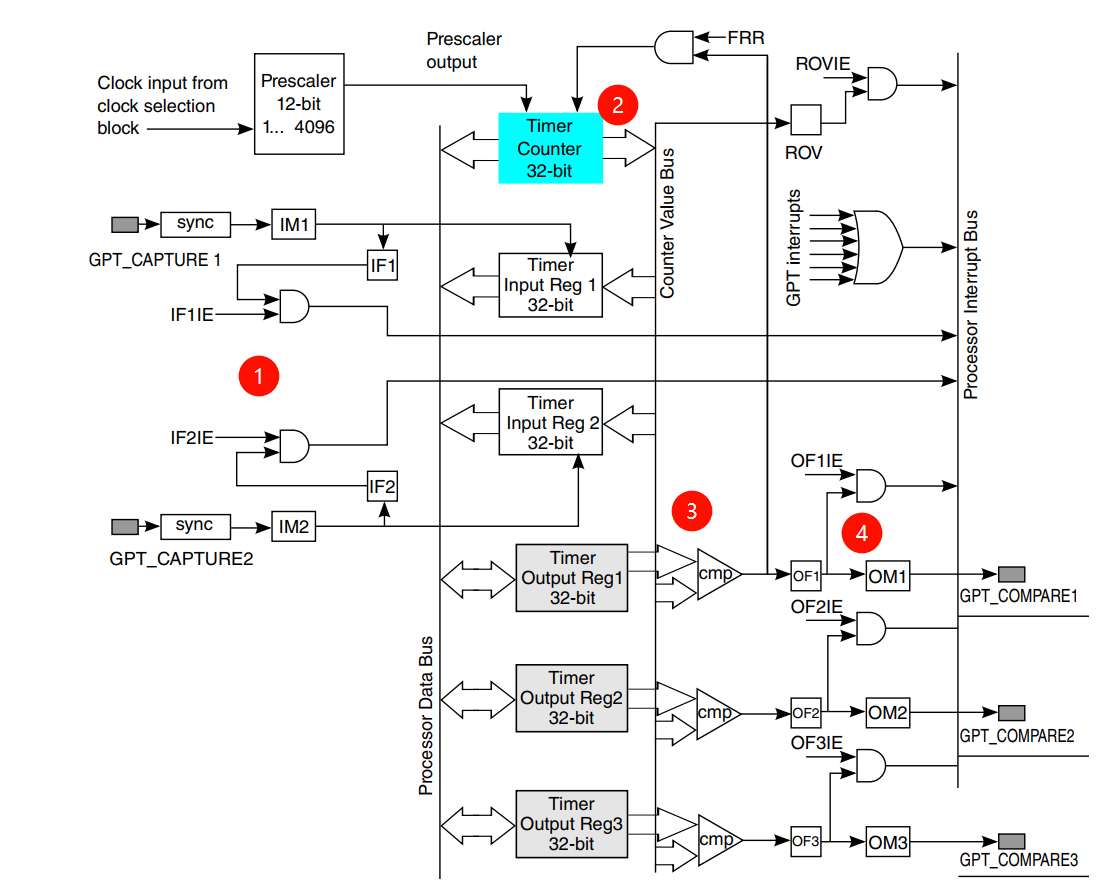

GPT 定时器结构如下图,图中各个部分为:

①:两路输入捕获通道,可检测外部信号边沿,记录触发时刻的计数值,用于测量脉冲宽度或频率

②:时钟源输入

③:三路输出比较通道,在 Timer Output Reg 中设置比较值,通过 cmp 触发比较事件

④:OFx,用于触发比较中断,OMx用于实现电平翻转,GPT_COMPAREx比较事件输出,可通 过OMx与GPT_COMPAREx结合实现PWM生成的功能

3.GPT实现精确延时

//延时 us 微秒

void delay_us(unsigned int us)

{unsigned int counter = 0;unsigned int old_counter, new_counter;old_counter = GPT1->CNT; //读取计数器计数值while(1){new_counter = GPT1->CNT;if (old_counter != new_counter){if (new_counter < old_counter) //超过计数最大值{counter += 0XFFFFFFFF - old_counter + new_counter;}else{ //没超过计数最大值counter += new_counter - old_counter;}if (counter >= us){return;}old_counter = new_counter;}}

}//延时 ms 毫秒

void delay_ms(unsigned int ms)

{while (ms--){delay_us(1000);}

}