【Proteus仿真】AT89C51单片机并行数据转换为串行仿真

目录

0案例视频效果展示

1基础知识补充

1.1并串转换芯片(74LS165)

一、芯片功能概述

二、主要引脚功能

三、工作原理简述

四、典型应用

五、特点

2 AT89C51单片机并行数据转换为串行仿真

2.1电路原理图

2.1.1电路组成及接线

2.2控制程序

2.2.1控制程序步骤

2.2.3源代码

3硬件工程师笔试面试相关文章链接(部分链接)

摘要:本文介绍了基于AT89C51单片机的并行数据转串行实现方案。系统采用74LS165并串转换芯片,详细说明了该芯片的引脚功能和工作原理:通过SH/LD控制端实现并行数据加载,在时钟脉冲下逐位串行输出。硬件连接上,单片机通过RXD接收串行数据,TXD提供移位脉冲,P0口LED显示转换结果。配套程序展示了如何利用SCON寄存器配置串口模式0,通过SPL控制信号完成并串转换,并将结果实时显示。文中还提供了硬件工程师笔试面试的相关资源链接。该系统适用于输入扩展、开关状态读取等应用场景。

0案例视频效果展示

例子36:基于AT89C51的并行数据转换为串行

1基础知识补充

1.1并串转换芯片(74LS165)

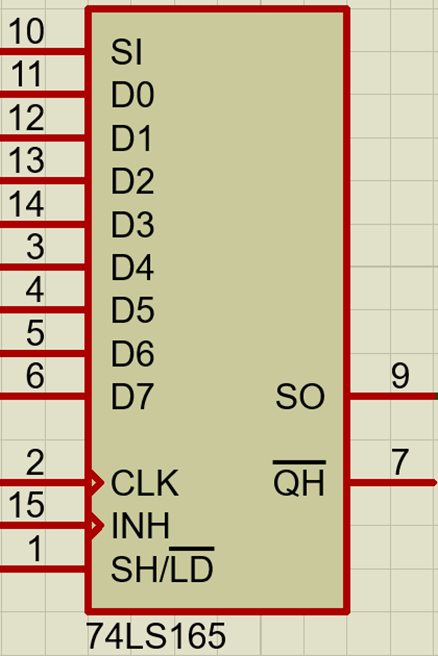

74LS165 是一种常用的并行输入、串行输出(PISO)移位寄存器,属于 TTL 逻辑系列芯片,广泛应用于单片机系统中扩展输入接口。

一、芯片功能概述

74LS165 可以将 8 位并行数据 转换为 串行数据输出,通过移位操作逐位输出数据,适用于输入引脚资源有限的系统中,实现多个开关或传感器状态的读取。

二、主要引脚功能

| 引脚名称 | 功能说明 |

| D0-D7 | 8 位并行数据输入端 |

| SO | 串行数据输出端 |

| SI(串行输入) | 级联多个 74LS165 时的串行输入端 |

| SH/LD | 移位/加载控制端,低电平时加载并行数据,高电平时开始移位 |

| CLK | 时钟输入端,控制数据移位 |