Zynq开发实践(SDK之自定义IP2)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

既然准备好了verilog代码,也在iverilog工具上面仿真过了,下面是不是就可以直接做成ip了。答案肯定是否定的,因为仿真ok的内容,直接fpga部署的时候,有可能会出现各种问题。至于会出哪些问题,这里简单总结下。

1、使用了不能综合的语法

在verilog里面,很多的语法是没有办法进行fpga部署的,所以如果类似于循环这样的语法,只能用在testbench上面,而不能出现在工程代码里面。这一类错误特别容易发生在刚转verilog开发的同学身上,尤其是c转verilog的同学。

2、组合逻辑过长的问题

这是比较头疼的一个问题。因为仿真的时候,所有的计算都是cpu帮助做的,而不是真实的逻辑门算出来的。所以这个时候,即使发生组合逻辑过长的问题,也是没有办法发现的。除非是综合部署的时候,我们才知道最长执行路径是多少。

3、寄存器到io口的距离问题

如果是仿真,外部的激励都是通过testbench直接赋值的。但如果是真实的电子器件,上面的信号是有抖动的。这种情况下要么加上功能开关,要么要两级延迟处理。如果没有这一步,很有可能我们采样得到的数据就是不对的。一旦采样数据不对,后面的功能和状态机都是无从谈起了。

4、寄存器宽度设置不对

比如我们仿真的时候,一般状态机的flag,或者是counter计数不需要那么多。但是fpga不一样,起步输入时钟就是50M,如果倍频一下有可能达到100M、200M。这种情况下,计数还是那么小就不合适了。此时,就会想到改计数范围。但是很多时候,我们发现修改了之后没有作用,这样查找了半天才发现是宽度范围的问题。

所以,比如8位的范围是255,16位的范围是65000多,24位的范围是1700万左右,32位的范围是40多亿。这些常用的范围一定要熟记于心。

5、使用了magic number

很多人喜欢直接用magic number来触发状态的变更。这种代码一开始写的时候,可能比较好理解,但是时间长了很容易就忘记里面的含义。此外,还有一个很大的潜在危险,那就是我们需要变更代码的时候,如果一部分发生修改,另外一部分没有发生修改,就很容易陷入自我怀疑当中。因此,养成良好的习惯,有助于解决一类的问题。

6、添加了错误的pin脚

pin脚如果忘记添加,这都还好说,但是如果是加错了,这类问题就需要用示波器进行查找了。fpga的eda工具只能保证生成的bitfile是对的,已经route到对的pin上面。但是如果pin本身就是错误码的,那确实就比较难查了。很多同学会误以为这种问题很简单,殊不知电路图上,上下对齐看走眼pin脚,其实是经常发生的事情。

7、修正后的verilog代码

最后我们给出修正后的呼吸灯verilog代码,代码如下,

module breathe_led(input rst, input clk, output led); //in fact it is wire// about local paramlocalparam FREQ_COUNT = 24'd500000;

localparam CATCH_COUNT = 24'd400000;

localparam STEP = 10'd1000; // inner wire & regreg[23:0] freq;

reg[23:0] catch;

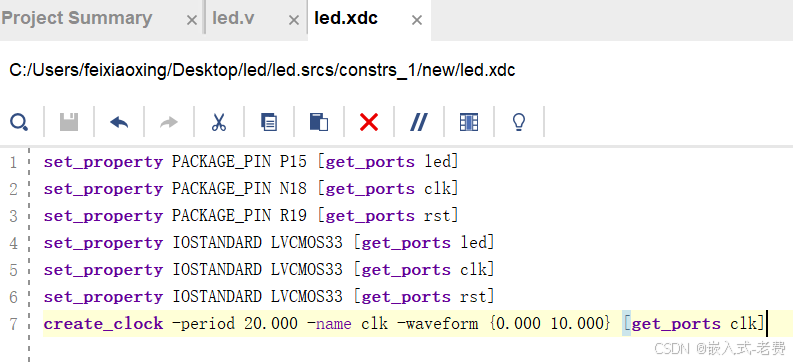

reg state;

reg next_state;// about state machinealways@(posedge clk or negedge rst)if(!rst)state <= 0;elsestate <= next_state;always@(*)if(state == 0 && catch > CATCH_COUNT)next_state <= 1;else if(state == 1 && catch == STEP)next_state <= 0;elsenext_state <= state;// basic frequencyalways @(posedge clk or negedge rst)if (!rst) freq <= 24'h00;else if (freq == FREQ_COUNT)freq <= 24'h00;elsefreq <= freq + 1;// part ratio in each partalways @(posedge clk or negedge rst)if(!rst)catch <= 24'h00;else if(freq == FREQ_COUNT)begincase (state)0: catch <= catch + STEP;1: catch <= catch - STEP;default: catch <= catch;endcaseend// output signal defined hereassign led = (freq >= catch) ? 0:1;endmodule对应的约束文件如下,有兴趣的同学可以实际跑一下。