vivado中DDR4 仿真模型的获取

在使用vivado进行DDR4 IP 核的生成后,为了验证自身逻辑。

本文中使用的软件为vivado2023.1

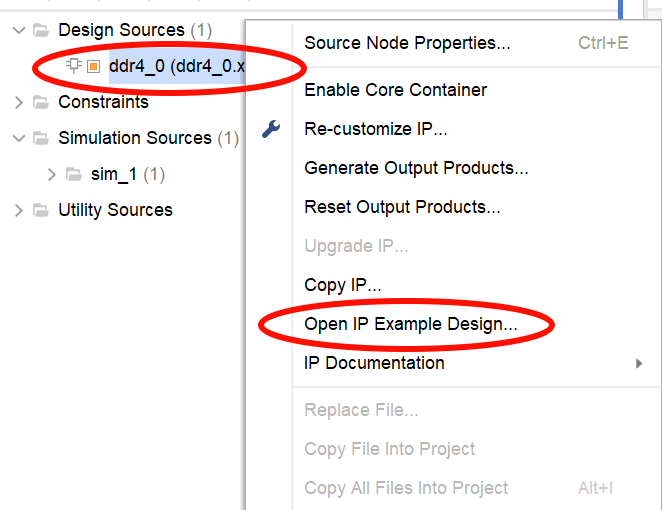

一、IP核创建并打开示例工程

右击IP核后,点击"open IP Example Design"。

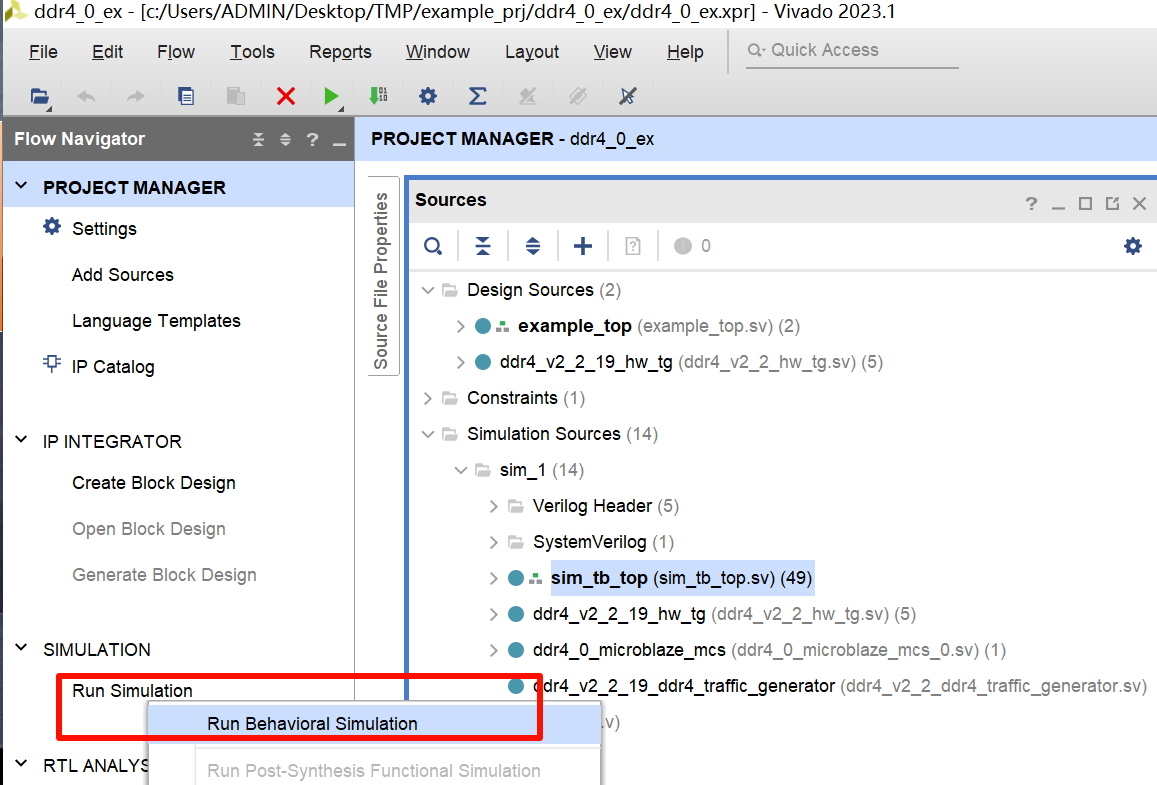

二,等待示例工程生成完毕

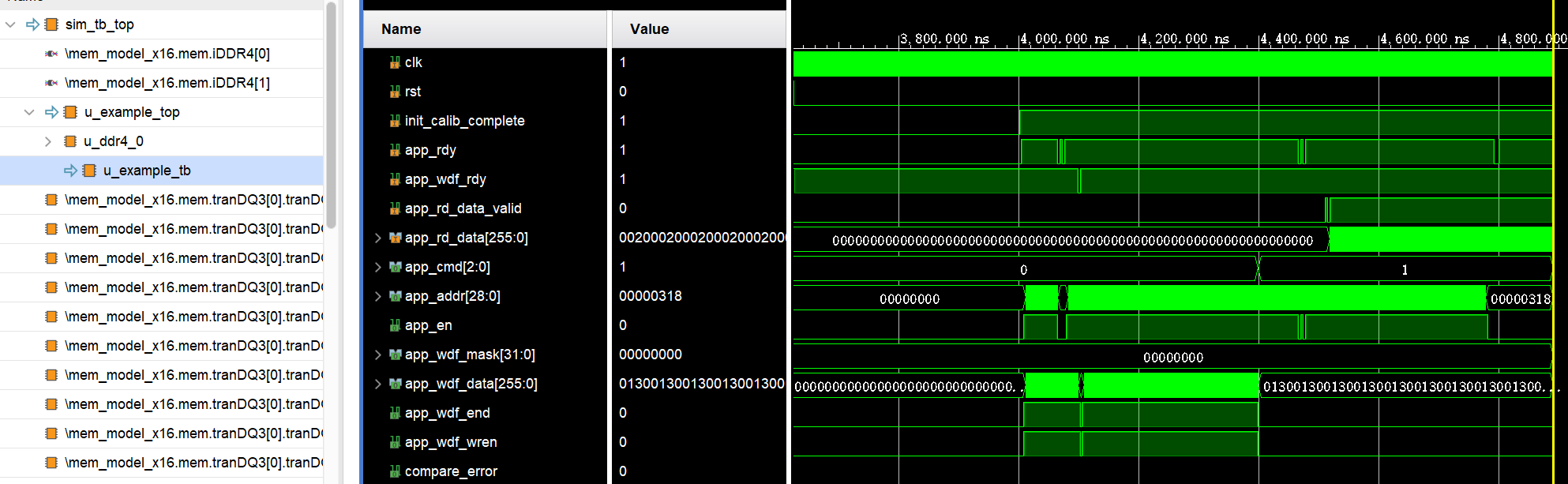

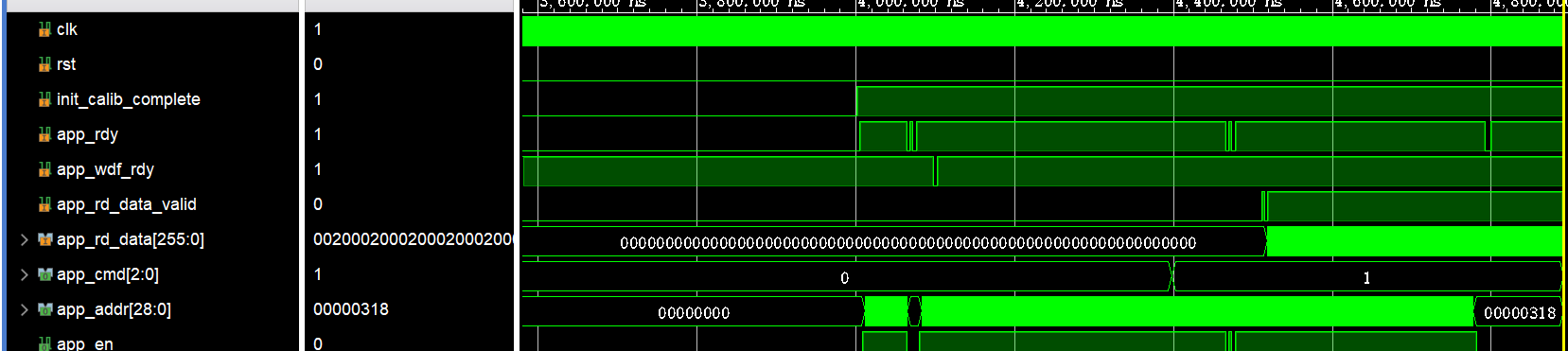

此时直接在示例工程中进行仿真,即可观察到DDR的读写波形,可以看到读写数据符合预期。

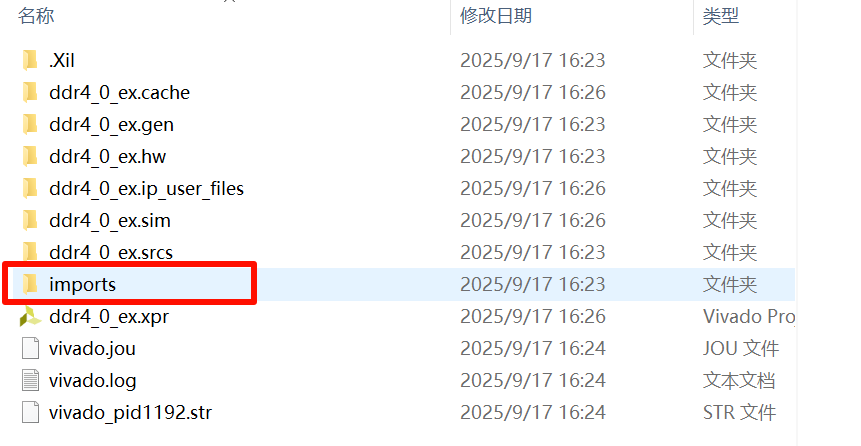

三、从示例工程中获取DDR仿真文件

在示例工程路径下,找到imports文件夹,文件夹内部即为所需要的所有DDR4的仿真模型文件。

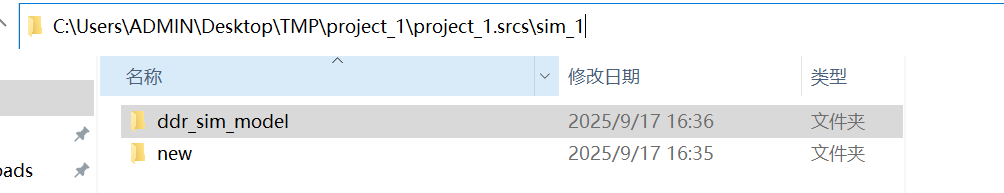

我们可以将此文件重命名为ddr_sim_model,拷贝到原工程中的路径下。

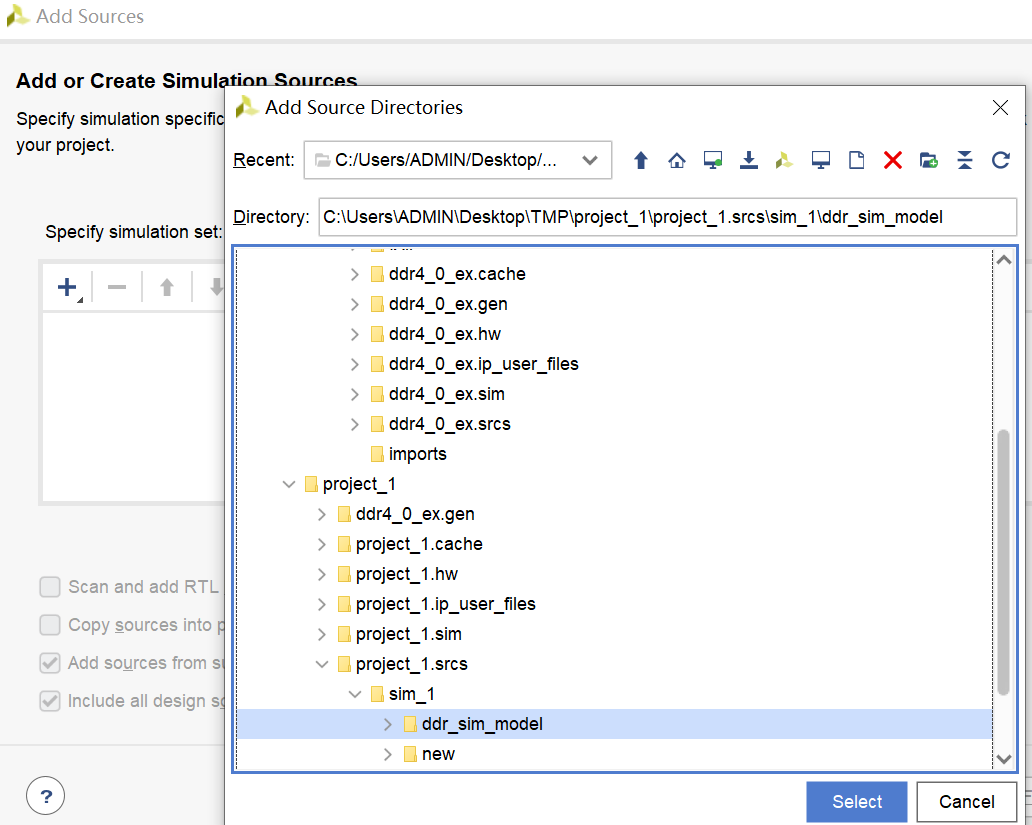

四,将文件导入到原工程中

五、文件类型修正

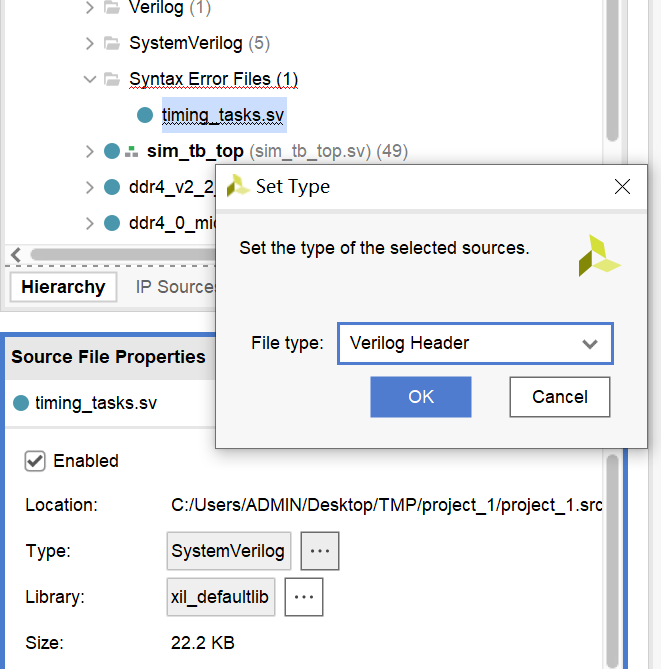

直接添加文件后,会显示timing_tasks文件错误,参考示例工程,右击此文件的“source File property”,将文件类型修改为“verilog Header”即可修正此错误。

六、原工程中的仿真

点击“run simulation”,运行仿真,此时可以观察到仿真结果正常。

此时我们只需要按照自己的工程代码,修改sim_tb_top文件、example_top和example_tb文件即可,此三个文件不是DDR4的仿真模型,仅是IP核的控制逻辑。