DMA 控制器核心组件作用与使用解读

目录

1 DMA 控制器核心组件详解

1.1 接口分类

Slave 接口

Master 接口(共 2 个)

Stream(数据流)相关

1.2 FIFO(先进先出存储器缓冲区)

1. 存在意义

2. 作用

1.3 通道选择

1.4 仲裁器

1.5 FIFO 和 Burst(突发传输)

Burst 的相关应用

DMA硬件架构解析:总线矩阵与核心组件:

https://blog.csdn.net/2402_83411382/article/details/151654212?spm=1001.2014.3001.5501

1 DMA 控制器核心组件详解

1.1 接口分类

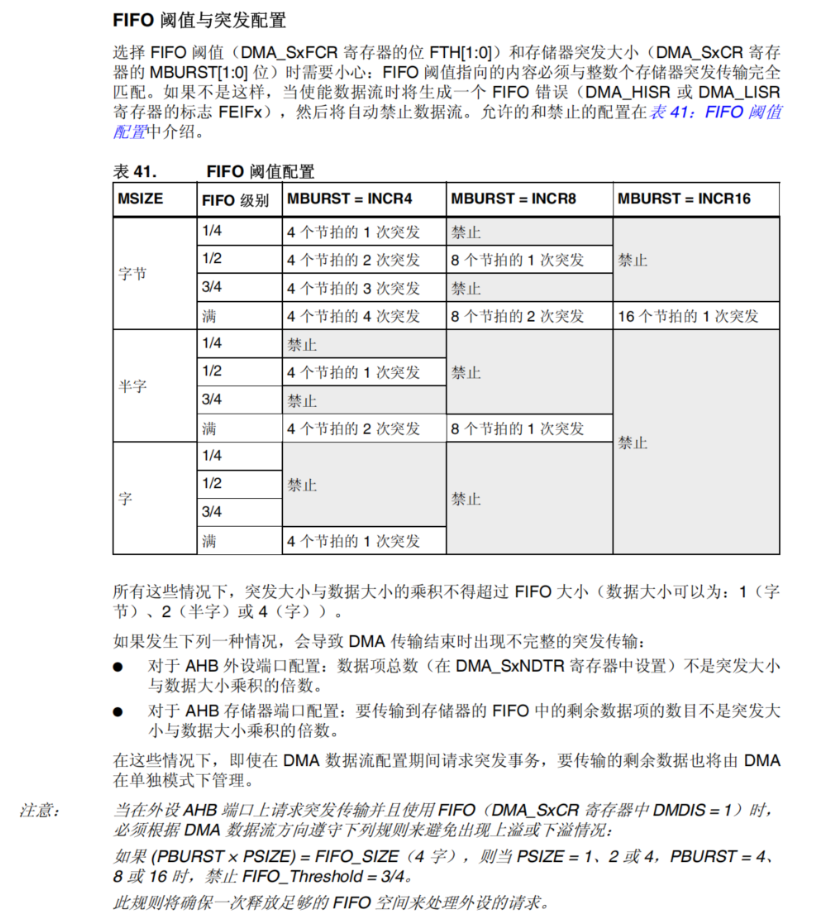

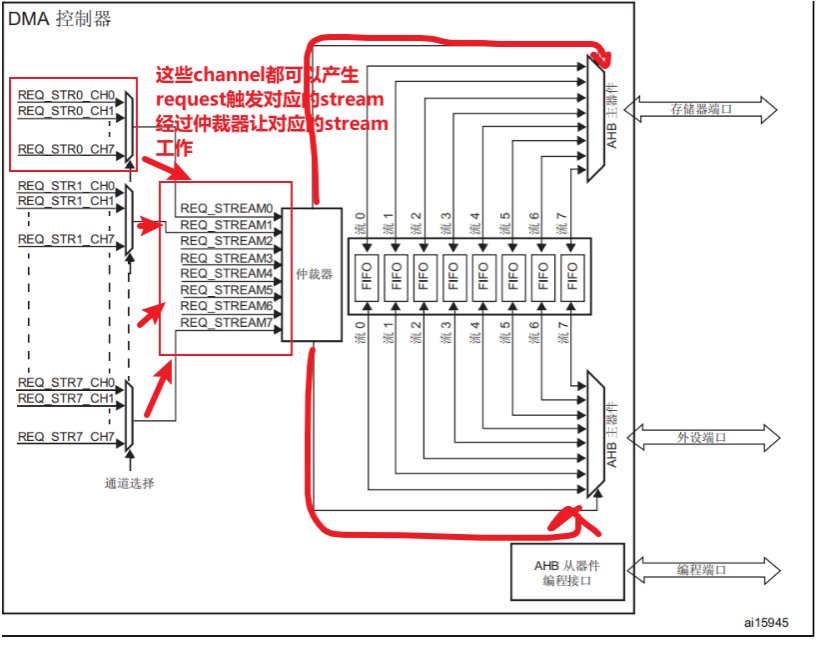

DMA 控制器与 AHB 总线存在三类关键接口,各有明确功能:

Slave 接口

作用是供 CPU 对 DMA 进行编程配置。CPU 通过该接口向 DMA 的相关寄存器写入配置参数,比如设置数据传输的源地址、目标地址、传输长度、数据宽度等,从而控制 DMA 的工作模式和传输行为。

Master 接口(共 2 个)

支持 DMA 开启两个 AHB 总线上两个从设备之间的信号通信。借助这两个接口,DMA 能够在不同的从设备(如外设与内存、内存与内存)之间自主地传输数据,无需 CPU 直接参与数据搬运过程。

Stream(数据流)相关

每个 DMA 都配备 8 个 Stream,且每个 Stream 仅支持单向传输(不过可配置为不同的传输方向,如从外设到内存、从内存到外设、从内存到内存)。

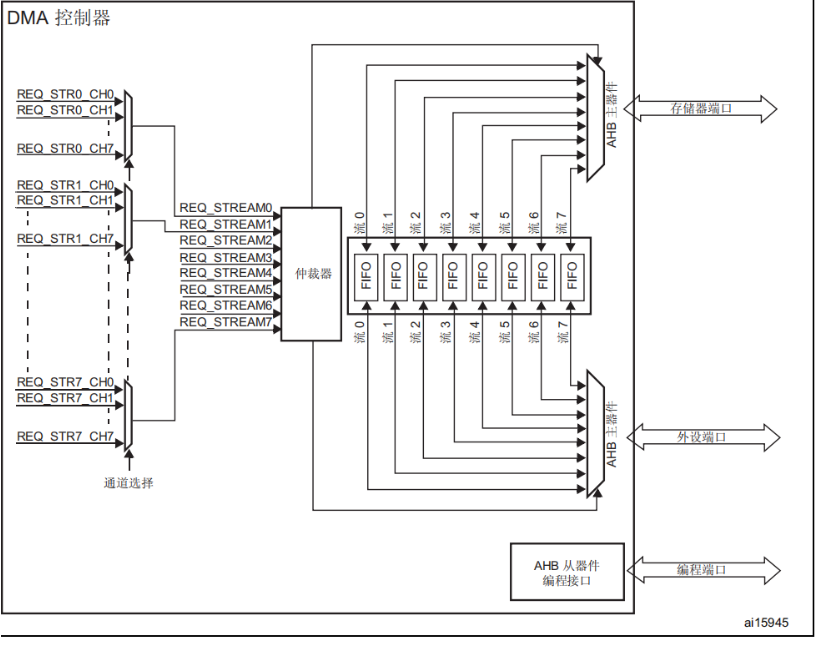

1.2 FIFO(先进先出存储器缓冲区)

1. 存在意义

若没有 FIFO,数据一进入就立即通过 Stream 输出,会频繁占用 AHB 总线,导致 CPU 难以获取总线使用权。而且总线带宽通常为 32 位,若每次仅传输 1 个字节就引发一次总线操作,效率极低。有了 FIFO 后,可先缓存足够多的字节,再一次性发送出去,显著提升了总线资源的利用率。

2. 作用

-

减少 AHB 带宽占用与仲裁次数:能减少 DMA 对 AHB 总线的频繁占用,降低 AHB 总线的仲裁频率,让 CPU 在 AHB 总线上获得更大的带宽,减少与 DMA 竞争总线的情况(DMA 接收数据时可旁路 AHB 总线)。

-

防止溢出:在需要动态扩展内存时,DMA 可将数据暂存到 FIFO 中,为 CPU 执行动态扩展内存操作争取时间,避免数据溢出。

-

提升并发性:当多路 Stream(如串口和 ADC 同时传输数据)进行仲裁时,FIFO 可对多路 Stream 的数据进行缓冲,极大避免数据出错,提高系统的并发性。

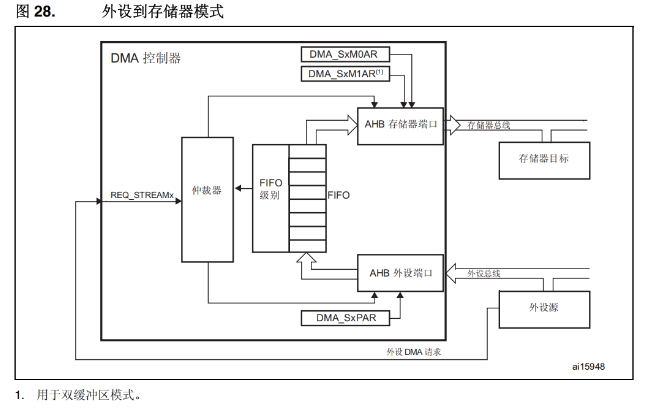

假设 UART 的数据通过 stream5 发送到内存,ADC 的数据通过 stream3 发送到内存

假如没有 FIFO,数据进来一次就立刻通过流输出,DMA 占用了总线 CPU 就不能占用总线了,而总线的带宽一般是 32 位,一个字节进来就打断一次,效率太低了。

但是有了 FIFO,可以先存够相应字节再一起发出去,提高了资源的利用率;FIFO 缓存的大小可以看手册

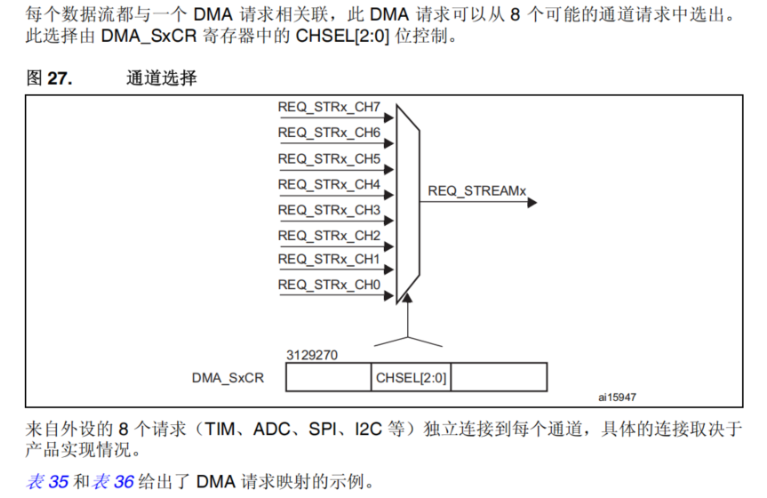

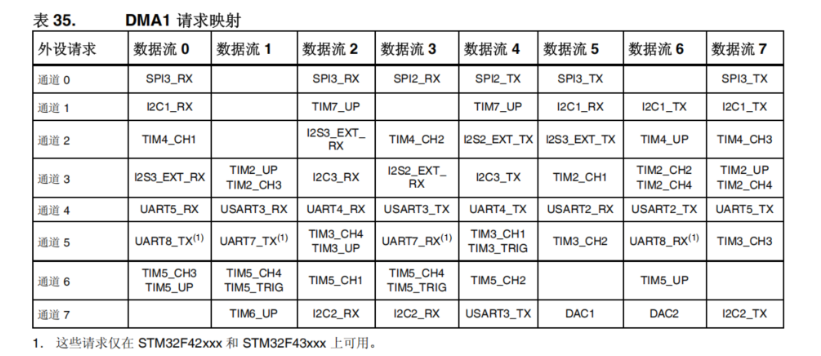

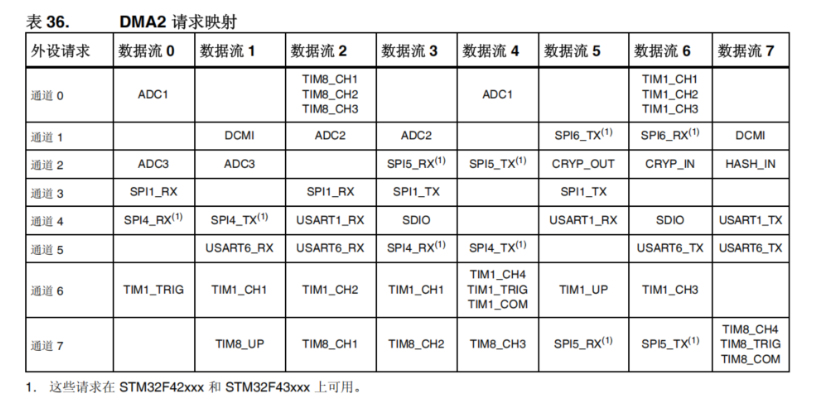

1.3 通道选择

STM32 的 DMA 控制器(如 DMA2)通常包含多个 Streams(流),每个 Stream 是一个独立的 “传输通道”,可独立处理一个外设的数据传输请求。

每个数据流(Stream)都与一个 DMA 请求相关联,该 DMA 请求可从 8 个可能的通道请求中选出,此选择由 DMA_SxCR 寄存器中的 CHSEL[2:0] 位控制。来自外设(如 TIM、ADC、SPI、I2C 等)的 8 个请求独立连接到每个通道,具体的连接方式取决于产品的实现情况。需要注意的是,一次只能触发一个通道进行数据传输。

1.Stream 的核心功能

每个 Stream 相当于一个 “专用传输通道”,负责:

-

绑定一个或多个外设的 DMA 请求(通过 “通道选择” 实现);

-

独立配置传输参数(源地址、目标地址、数据长度、传输方向、数据宽度等);

-

在仲裁器的调度下获取总线权限,完成数据传输。

2.Stream 与 Channel(通道)的区别

-

Stream 是物理传输通道:每个 DMA 控制器有多个 Stream(如 DMA2 有 8 个 Stream),硬件上独立存在,可并行工作;

-

Channel 是逻辑请求源:每个 Stream 内部包含多个 Channel(通常 8 个),用于选择该 Stream 绑定哪个外设的 DMA 请求(如 USART1_TX、SPI2_RX 等)。

3.Stream 的优势

多 Stream 设计允许多个外设同时进行 DMA 传输(如 UART 接收、SPI 发送、ADC 采样同时通过不同 Stream 传输),大幅提升系统数据吞吐量,避免单通道瓶颈。

1.4 仲裁器

同一时刻只能有一路 stream 搬运数据

如果 stream1 和 stream2 同时被选通,谁先运行呢?

当多个 Stream(如 stream1 和 stream2)同时被选通时,仲裁器通过软件优先级和硬件优先级两个条件来决定哪个 Stream 先运行。

1. 软件优先级

每个数据流的优先级可在 DMA_SxCR 寄存器中配置,共分为四个级别:非常高优先级、高优先级、中优先级、低优先级。

2. 硬件优先级

若两个请求的软件优先级相同,则编号低的数据流优先于编号高的数据流。例如,数据流 2 的优先级高于数据流 4。仲裁器为两个 AHB 主端口(存储器端口和外设端口)提供基于请求优先级的 8 个 DMA 数据流请求管理,并启动外设 / 存储器的访问序列。

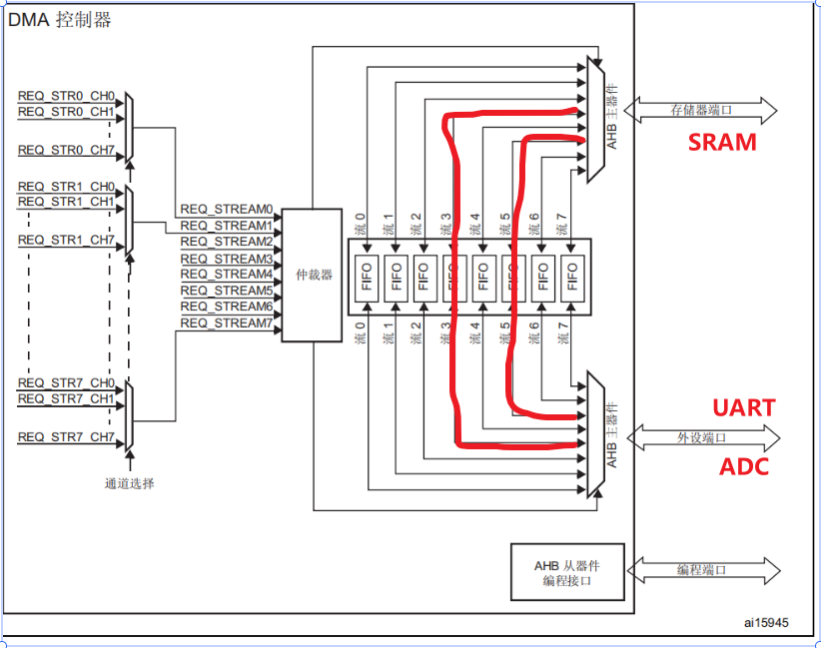

1.5 FIFO 和 Burst(突发传输)

Burst 的相关应用

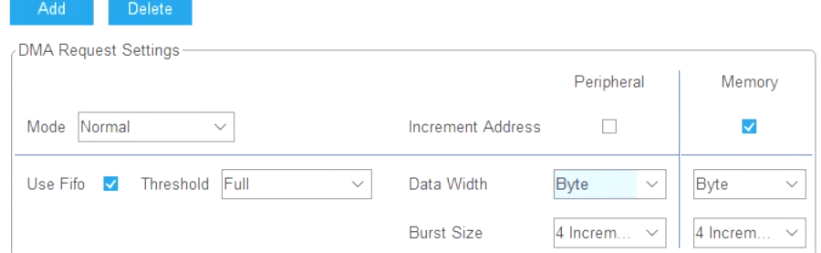

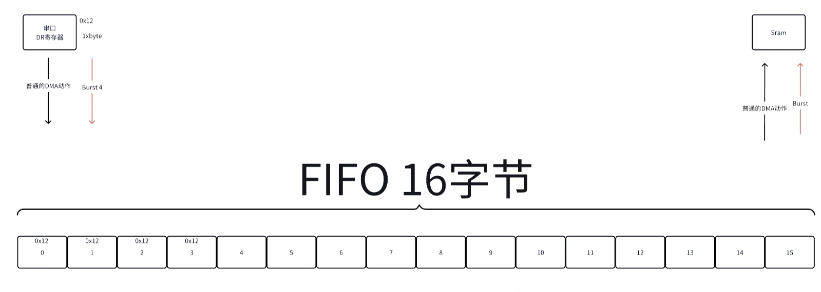

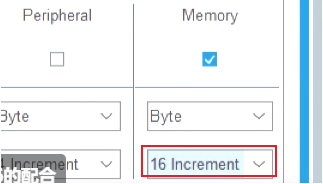

在 DMA 配置界面中,peripheral(外设)和Memory(内存)的Burst size(突发传输大小) 用于分别控制从外设读取数据或向内存写入数据时,一次突发传输的数据量 。

Burst 传输允许在一次总线事务中传输多个连续的数据。

通过 Burst 传输,可以在一次总线占用期间传输多个数据,使总线在单位时间内传输更多的数据量,充分利用总线带宽,提高总线利用率。

(注:stmf4 的 FIFO 大小是 16 字节,不同的芯片 FIFO 容量可能不一样)

这里 Data Width 是一个字节,Peripheral 的 Burst Size 是 4increment,假设接收到 0x12,burst 会倍增成四个 0x12 填入到 FIFO,只要我们发四次 0x12 就可以填满 FIFO;

如果 Memory 的使用 burst,这里是一次传输 16 个字节,而且 burst 会占用总线直到数据发完为止,此期间 CPU 打断不了,但是不连续的节拍之间 CPU 依然可以打断

Burst 介绍:

DMA 控制器可以生成单次传输或增量突发传输,传输的节拍数为 4、8 或 16。

为了确保数据一致性,构成突发传输的每组传输都是不可分割的:AHB 传输被锁定,AHB 总线矩阵的仲裁器在突发传输序列期间不会撤销 DMA 主设备的授权。

作用:

可以通过 Burst 进行多个寄存器的同时修改,在 M2P 时同时配置多个定时器

https://shequ.stmicroelectronics.cn/thread-638925-1-1.html