ARM-寄存器与异常处理全解析

1.计算机的指令集

- CPU的指令集其实就是用指令对计算机实现控制 和计算的指令集合。

- 分复杂指令集和精简指令集 。

- RISC:Reduced Instruction Set Computer

- CISC:Complex Instruction Set Computer

2.Cortex-A7 内核中的寄存器体系

(1)通用寄存器 (General-Purpose Registers, GPRs)

R0–R12

一共 13 个通用寄存器,用来存储数据、中间结果、函数参数等。

在 ARM 的 过程调用标准 (AAPCS) 里,

R0–R3 常用作函数参数和返回值寄存器

R4–R11 常用作被调用者保存寄存器(callee-saved)

R12 (IP) 常作为临时寄存器或内部过程调用寄存器

(2)栈指针 (Stack Pointer, SP)

R13

指向当前栈顶,用于存放局部变量、保存现场(函数调用时寄存器的备份)等。

在不同的 CPU 模式下可能有不同的 SP 副本(例如 Supervisor 模式、IRQ 模式有自己独立的 SP)。

(3)链接寄存器 (Link Register, LR)

R14

在执行 BL(Branch with Link) 指令时,CPU 会把返回地址保存到 LR 里。

函数调用结束时,通常通过

MOV PC, LR或BX LR返回调用点。

(4)程序计数器 (Program Counter, PC)

R15

保存 当前指令的地址,ARM 采用 流水线,因此读取 PC 的值时通常比实际执行位置超前几条指令(32bit +4)。

(5)程序状态寄存器 (Program Status Registers)

Cortex-A7 属于 ARMv7-A,支持以下状态寄存器:

CPSR(Current Program Status Register)当前程序状态寄存器

保存标志位(条件标志 N/Z/C/V)、中断屏蔽位、处理器模式(如 User、FIQ、IRQ、Supervisor 等)。

SPSR(Saved Program Status Register)保存的程序状态寄存器

在异常发生时,CPSR 会被保存到相应模式下的 SPSR,便于异常处理完毕后恢复。

(6)浮点与 SIMD 寄存器

Cortex-A7 支持 VFPv4 + NEON:

32 个 64 位 NEON/VFP 寄存器(D0–D31)

可被当作 64 位寄存器 D0–D31 使用

或者拆分为 32 位寄存器 S0–S31 使用

支持单精度和双精度浮点计算,加速多媒体、信号处理、矩阵运算等。

(7)MMU (Memory Management Unit, 内存管理单元)

MMU 的主要功能是:

①虚拟地址 → 物理地址转换

- Cortex-A7 采用 虚拟内存 机制,应用程序看到的是虚拟地址(VA),MMU 负责将其映射到实际物理内存地址(PA)。

这样多个应用可以运行在各自的独立虚拟空间里,互不干扰。

②页表机制 (Page Table)

- ARMv7-A 的 MMU 使用多级页表(一级、二级),支持 4KB/64KB/1MB/16MB 等不同大小的页/段映射。

页表中不仅保存地址映射,还包括访问权限、缓存策略等。

③内存保护

防止用户程序访问内核空间

防止越界访问或恶意代码覆盖关键内存

④内存区域属性配置

是否可缓存(Cacheable / Non-Cacheable)

是否可缓冲(Bufferable)

内存访问顺序(Strongly-Ordered, Device, Normal memory)

总结:MMU = 地址转换器 + 安全保护器 + 内存属性控制器。

(8)Cache (高速缓存)

Cortex-A7 通常配置:

L1 Cache

指令 Cache (I-Cache):8KB–32KB

数据 Cache (D-Cache):8KB–32KB

可选 L2 Cache(最多 1MB,外接 L2 控制器)

Cache 的作用:

①减少访存延迟

CPU 速度远快于 DRAM,Cache 作为中间层存储热点数据。

②Cache 一致性

Cortex-A7 支持 多核一致性(SMP,Symmetric Multi-Processing),各核 Cache 通过 snoop 协议 保持数据同步。

③Cache 策略

写直达 (Write-through)

写回 (Write-back)

根据页表配置,某些内存区域可设为不可缓存(如 I/O 映射寄存器)。

总结:Cache = 提速器,把常用数据放在离 CPU 最近的地方。

(9)内存访问权限 (Memory Access Permissions)

Cortex-A7 的内存访问权限由 MMU + 状态寄存器 (CPSR) 一起控制:

①特权级 (Privilege Levels)

用户模式 (User):只能访问用户空间

系统/管理模式 (Supervisor/System):可以访问所有空间

还有 IRQ、FIQ、Abort、Undefined 等异常模式,各自有独立栈

②访问权限位 (AP bits, Access Permission bits)

在页表项中设置,决定了谁能访问该内存:

仅特权模式可读写

用户模式可读、不可写

全部可读写

不可访问

域 (Domain)(在早期 ARM 架构里较常用)

将内存划分为 16 个域,每个域有不同的访问控制策略。

执行权限 (XN bit, eXecute-Never)

可以禁止某些内存区域执行代码(防止堆栈溢出攻击、缓冲区注入攻击)。

总结:访问权限保证了 系统安全性。

(10)ALU(算术逻辑单元, Arithmetic Logic Unit)

①ALU 的定义

ALU 是 CPU 内部最基础的运算部件,负责执行 算术运算 和 逻辑运算。可以理解为:寄存器里拿到数据 → ALU 做计算 → 把结果写回寄存器。

②ALU 的主要功能

算术运算:加、减、乘、除

逻辑运算:与(AND)、或(OR)、异或(XOR)、非(NOT)

移位/旋转:把二进制数左移、右移

比较:判断两个数是否相等、大于、小于

③ALU 与状态寄存器 (CPSR)

运算完成后,ALU 会更新一些标志位:

Z(Zero):结果是不是 0

N(Negative):结果是否为负

C(Carry):是否有进位/借位

V(Overflow):是否溢出

这些标志位会被条件跳转等指令使用。

总结:ALU 就是 CPU 的 运算器,负责所有加减逻辑和比较操作,是程序运行的核心计算部件。

总结:

Cortex-A7 内核的寄存器体系由 16 个核心寄存器 (R0–R15) + 程序状态寄存(CPSR/SPSR) + NEON/VFP 寄存器 + 系统控制寄存器 组成。

其中 R0–R12 是通用寄存器,R13 (SP)、R14 (LR)、R15 (PC) 有特殊用途,CPSR/SPSR 控制 CPU 状态。

3.工作模式

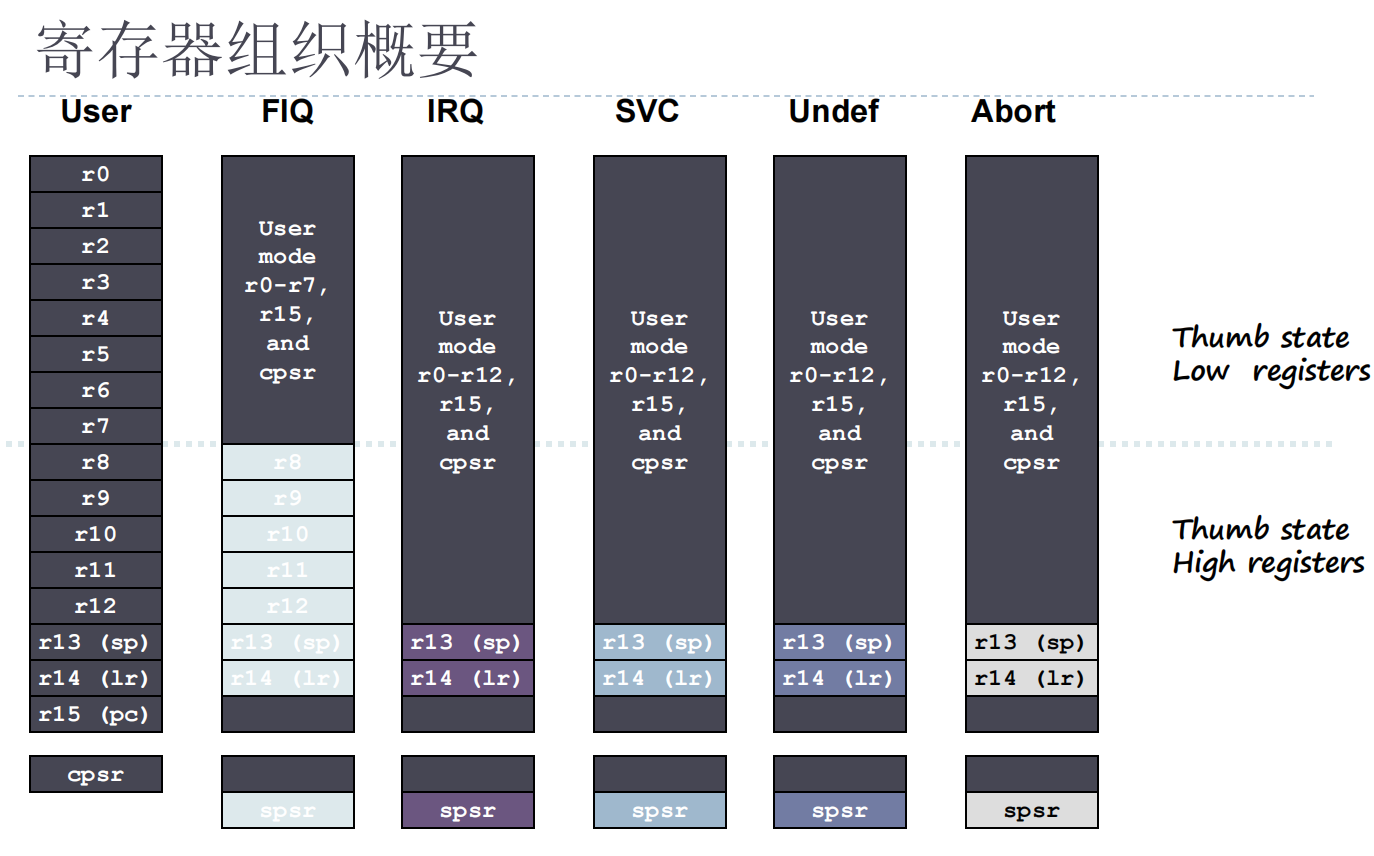

(1)ARM9 的工作模式

ARM9 属于 ARMv4T / ARMv5TE 架构,支持 7 种工作模式(ARM 传统模式)。

模式列表:

User (usr)

普通用户模式,运行应用程序,权限最低。

FIQ (fiq)

快速中断模式,用于处理高速数据传输或通道处理,提供额外的寄存器以加速处理。

IRQ (irq)

普通中断模式,用于处理中断请求。

Supervisor (svc)

管理模式,操作系统内核常用,响应软件中断 (SWI)。

Abort (abt)

存储器异常模式,处理预取或数据访问异常。

Undefined (und)

未定义指令模式,处理非法或未实现的指令。

System (sys) (ARMv4T 之后新增)

特权模式,和 User 模式的寄存器相同,但拥有特权,常用于 OS 运行内核代码。

ARM9 工作模式总结:

用户态:User

特权态:FIQ, IRQ, SVC, ABT, UND, SYS

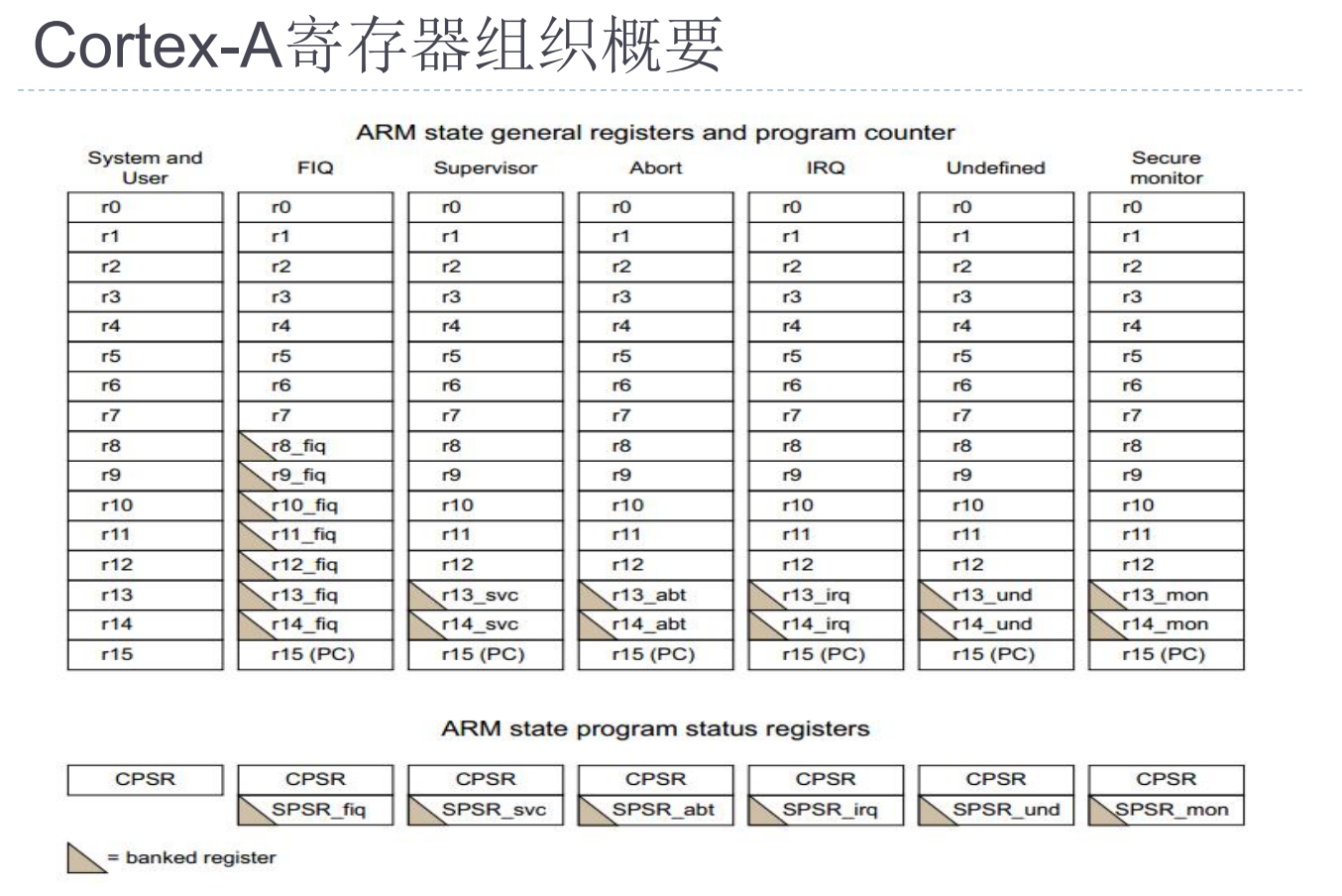

(2)ARM Cortex-A (ARMv7-A/ARMv8-A) 的工作模式

ARMv7-A

延续 ARM9 的模式,支持9 种模式:

User (usr)

FIQ (fiq)

IRQ (irq)

Supervisor (svc)

Abort (abt)

Undefined (und)

System (sys)

Cortex-A特有模式(新增)

Monitor (mon) (新增)

用于 TrustZone 安全扩展,在 Normal World 与 Secure World 之间切换。

(3)对比

| 架构/处理器 | 模式数量 | 模式名称 | 主要作用 |

|---|---|---|---|

| ARM9 (ARMv4/5) | 7 种 | usr (用户) | 普通应用程序,非特权 |

| sys (系统) | 与 usr 相同寄存器,但具特权,OS 内核常用 | ||

| svc (管理) | 处理软件中断 (SWI),OS 内核入口 | ||

| irq (中断) | 普通中断服务 | ||

| fiq (快速中断) | 高速中断,寄存器独立,加快响应 | ||

| abt (异常) | 处理存储器访问异常 | ||

| und (未定义) | 处理非法/未实现的指令 | ||

| Cortex-A (ARMv7-A) | 8 种 | ARM9 的 7 种 + mon (监控) | TrustZone 安全模式,切换 Secure/Normal World |

| Cortex-A (ARMv8-A, AArch32) | 9 种 | ARMv7 的 8 种 + hyp (虚拟化) | 支持虚拟化,运行 Hypervisor |

| Cortex-A (ARMv8-A, AArch64) | 4 个异常等级 (EL) | EL0 | 用户应用层 |

| EL1 | 操作系统内核层 | ||

| EL2 | Hypervisor 层 (虚拟化) | ||

| EL3 | Secure Monitor 层 (安全/TrustZone) |

4.ARM 与 Cortex-A 寄存器对比表

| 架构 | 总数 | 寄存器构成 | 说明 |

|---|---|---|---|

| ARM (ARM9 等) | 37 个 (32-bit) | - 1 × PC (程序计数器) - 1 × CPSR (当前程序状态寄存器) - 5 × SPSR (保存的程序状态寄存器,特权模式专用) - 30 × 通用寄存器 (R0–R15, 含 SP=R13, LR=R14) | 不同模式下部分寄存器“银行化”,用于快速切换上下文 |

| Cortex-A | 40 个 (32-bit) | - 37 个与 ARM9 相同 - 额外 3 个:R13_mon, R14_mon, SPSR_mon (用于 Monitor 模式) | Monitor 模式是 TrustZone 安全扩展新增的模式 |

5.ARM 内核在异常(Exception)产生时的处理流程。

(1)ARM 异常的基本概念

异常 (Exception):指令执行过程中发生的特殊事件,比如 中断、系统调用、内存访问错误、未定义指令 等。

当异常发生时,CPU 会 自动切换模式、保存现场、跳转到异常向量入口,从而交给异常处理程序。

(2) ARM 发生异常时内核自动完成的工作

当异常产生时,ARM 内核硬件会执行以下步骤(以 AArch32/ARMv7-A 为例):

模式切换 (Mode Switch)

处理器从当前模式切换到相应的异常模式(如 IRQ → irq 模式,FIQ → fiq 模式,SVC → svc 模式等)。

保存返回地址 (LR = Link Register)

把当前的 下一条指令地址(PC + 偏移)保存到该模式下的 LR(R14)中,作为异常返回时的依据。

偏移量与异常类型相关:

IRQ/FIQ:

LR = PC + 4SWI/未定义指令:

LR = PC + 4Prefetch Abort:

LR = PC + 4Data Abort:

LR = PC + 8保存程序状态寄存器 (SPSR)

将 CPSR (Current Program Status Register) 的内容保存到当前模式的 SPSR (Saved Program Status Register)。

包含条件码、中断使能标志、处理器模式等。

设置新的 CPSR

处理器模式切换到对应的异常模式。

中断屏蔽位可能被设置(如进入 IRQ/FIQ 时自动屏蔽后续同类中断)。

跳转到异常向量地址 (Vector Table)

根据异常类型,从 异常向量表中取出入口地址并跳转执行:

0x00:Reset

0x04:Undefined Instruction

0x08:Software Interrupt (SWI/SVC)

0x0C:Prefetch Abort

0x10:Data Abort

0x14:Reserved

0x18:IRQ

0x1C:FIQ

(3)异常处理程序的工作

硬件只做最小化的工作,剩下由 异常处理程序 (Exception Handler) 完成:

保存现场(将通用寄存器 R0–R12 压栈)

根据异常类型执行相应的处理逻辑

恢复现场(出栈恢复寄存器)

从 LR/SPSR 中恢复程序执行(通过

SUBS PC, LR, #偏移或MOVS PC, LR返回)

总结(ARM 内核在异常产生时自动完成的工作)

切换到对应的异常模式

保存返回地址到 LR_异常模式

将 CPSR 保存到 SPSR_异常模式

修改 CPSR(切换模式、屏蔽中断等)

跳转到异常向量表对应入口地址

6.异常向量表 (Exception Vector Table)

(1)定义

异常向量表是一张位于 固定内存地址 的小型跳转表(通常占用几十字节),它保存了各类 异常处理程序入口的地址。

当 ARM 处理器发生异常时,硬件会自动跳转到对应的向量表入口地址,从而执行异常处理流程。

(2)表项内容

每个表项对应一种异常,存放的不是“完整的处理代码”,而是一条跳转指令(通常是

LDR PC, [PC, #offset]或B handler),用来跳到真正的异常处理程序入口。典型 ARMv7-A (AArch32) 异常向量表布局:

偏移地址 异常类型 描述 0x00 Reset 上电或复位 0x04 Undefined Instruction 未定义指令 0x08 SWI (SVC) 软件中断(系统调用) 0x0C Prefetch Abort 取指异常 0x10 Data Abort 数据访问异常 0x14 Reserved 保留 0x18 IRQ 普通中断 0x1C FIQ 快速中断 每个表项通常只有 4 字节(一条 ARM 指令),所以整个表大小一般是 32 字节。

(3)作用

将不同类型的异常映射到对应的处理程序

实现异常处理的快速入口,减少硬件开销

保证异常响应的统一性(固定入口 → 软件分发)

总结

异常向量表 = 异常类型 → 异常处理入口 的映射表

包含 Reset、IRQ、FIQ、SVC、Abort 等入口

大小一般是 8 个表项 × 4 字节 = 32 字节

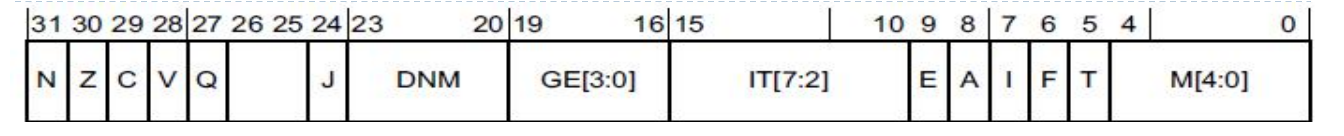

7.程序状态寄存器 (CPSR, Current Program Status Register)

(1)程序状态寄存器 CPSR 位域说明

位号 名称 含义 31 N 算术运算结果为负 (Negative) 30 Z 算术运算结果为零 (Zero) 29 C 算术运算产生进位/借位 (Carry) 28 V 算术运算结果溢出 (oVerflow) 27 Q 饱和 (Saturation) 标志,仅 ARMv5TE-J 及以上支持 26 J Jazelle 状态位 (支持 Java 字节码执行) 25 DNM Do Not Modify,保留位 24–21 GE[3:0] SIMD 指令“大于等于”比较结果标志 20–16 IT[7:2] Thumb 指令的条件执行状态 (IF-THEN 块) 15 E Endianness 位:0=小端,1=大端 14 A 禁止 imprecise data abort (精度不确定的数据异常) 13 I IRQ 禁止位,1=禁止 IRQ 12 F FIQ 禁止位,1=禁止 FIQ 11 T Thumb 状态位:0=ARM 状态,1=Thumb/ThumbEE 状态 10–0 M[4:0] 处理器模式位:决定当前工作模式

(2)处理器模式位 (M[4:0]) 编码

M[4:0] 模式名称 10000 User 模式 10001 FIQ 模式 10010 IRQ 模式 10011 SVC (Supervisor) 模式 10110 Monitor 模式 (TrustZone) 10111 Abort 模式 11011 Undefined 模式 11111 System 模式