Error ratio tests for 200 Gb/s per lane ISLs using PMAmeasurements

本文是IEEE802.3dj的章节翻译,跟着推算了一遍,有些地方还是比较模糊。按惯例先翻译一遍,后面实际用起来就会常读常新。

ISL:Internal Signal Link

BLER:Block Error Ratio

174A.8 采用 PMA 测量方法对单lane 200Gb/s的 ISL 进行误差比率测试 Error ratio tests for 200 Gb/s per lane ISLs using PMA

measurements

包含两端的PMD(Physical Medium Dependent,物理介质相关)和中间传输介质;

包含两端的内层FEC(Forward Error Correction,前向纠错)和PMD,以及中间介质;

包含一个xAUI-n接口(用于连接MAC/PHY与PMA之间的接口)

测试目的

验证ISL(Internal Signal Link)在整个路径上的误码率(Error Ratio)是否在其分配的容限范围内。这个“路径”可以是:

PHY到PHY(物理层到物理层),PHY= PCS + PMA + PMD;

或 XS到XS(XGMII Extender Sublayer,扩展子层之间)。

关键参数定义

测试使用两个核心参数来评估ISL性能:

a. BERtotal(总误码率预算)

表示整个PHY-to-PHY或XS-to-XS路径所允许的总误码率(Bit Error Ratio)。

它是根据该路径上分配的码字错误率(Codeword Error Ratio) 推导出来的,假设错误是随机分布的。

这是一个系统级的性能目标。

BERtotal分配汇总:

frame loss ratio FEC codeword error ratio CRC32 块的 CRC 错误率 pre-correction BER (BERtotal) xMII Extender <1E–12 <2.4E-13 <2.21E-4 PCS-to-PCS path <1.45E-11 <2.29E-4 FEC-to-FEC path <5.8E-11 <5.71E-11 <2E-2 174A.4 xMII Extender

frame loss ratio(64 字节的帧,且各帧之间有最小的间隔时间) 预计小于1E–12.这相当于FEC codeword error ratio低于 2.4E-13。如果 RS-FEC 输入端的错误是不相关的,这相当于pre-correction BER (BERtotal) =2.21E-4 .

174A.5 PCS-to-PCS path

对于不包含 FEC 到 FEC 路径的 200GBASE-R、400GBASE-R、800GBASE-R 或 1.6TBASE-R PHY,预期的帧丢失率相当于在 PCS 测量到的FEC codeword error ratio,即小于 1.45E-11。如果 RS-FEC 输入端的错误是不相关的,则这相当于pre-correction BER (BERtotal) =2.92E-4。

174A.6 FEC-to-FEC path

对于具有最小帧间间隔的 64 字节 MAC 帧,其帧丢失率预计低于5.8E-11。对于使用 800GBASE-ER1 FEC 的物理层而言,预期的帧丢失率相当于 CRC32 块的 CRC 错误率,即小于 5.706E-11。如果 FEC 输入端的错误是不相关的,这相当于pre-correction BER (BERtotal) =2E-2。

b. BERadded(附加误码率预算)

表示在同一路径中其他未被当前测试包含的ISL所引入的误码率贡献。

换句话说,当前ISL只能“占用”一部分BER预算,其余部分要留给路径上的其他链路。

BERadded分配汇总:

PMD receiver PHY receiver 适用模块类型 章节 BERadded 6.4E-05 3.2E-05 200GBASE-DR1 180 400GBASE-DR2 800GBASE-DR4 1.6TBASE-DR8 BLER

(block error ratio)

1.45E–11 1.45E–11 800GBASE-FR4-500 181 200GBASE-DR1-2 182 400GBASE-DR2-2 800GBASE-DR4-2 测试方法 174A.8 174A.10 1.6TBASE-DR8-2 800GBASE-FR4 183 800GBASE-LR4 800GBASE-LR1 185

4. 测试方法概述

方法一:基于误码掩码(Error Masks) 的PMA测量(见 174A.8.5)

使用PMA层的错误检测机制(如内置误码检测器)和计数器。

通过分析错误发生的模式(即“错误掩码”),判断ISL的误码表现是否符合要求。

方法二:基于块错误率(Block Error Ratio, BLER) 的PMA测量(见 174A.8.6)

BLER是对码字错误率的一种估计。

它会调整那些未包含在本次测试中的其他ISL所带来的误码影响。

这样可以更准确地评估当前ISL对整体性能的贡献。

方法三:基于PCS(Physical Coding Sublayer)测量的BLER方法(见 174A.10)

与PMA不同,PCS层也提供错误统计信息。

此方法利用PCS层的测量来评估ISL的块错误率。

5. 测量基础:PMA计数器与直方图

所有基于PMA的测量都依赖于174A.8.2中定义的错误检测器和计数器。

测试过程中会采集一组直方图(histogram bins)数据,这些数据由PMA的计数器生成(定义在174A.8.3)。

直方图可用于分析错误发生的频率和分布,进而推导出BER或BLER。

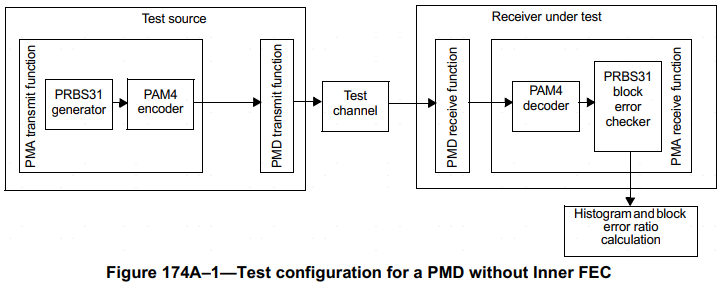

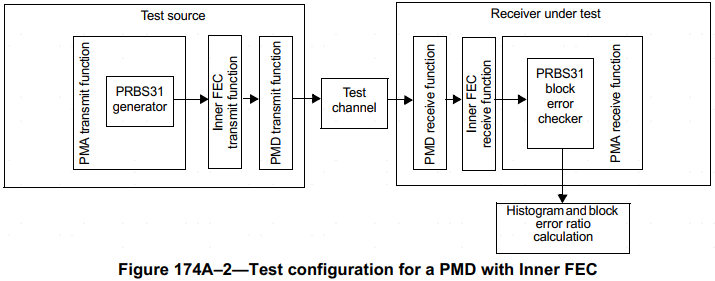

174A.8.1 PMA block error ratio test configurations

PMA block error ratio test configurations:

174A.8.2 PMA block error counters

这段内容定义了在 200 Gb/s 每通道 的高速以太网链路中,如何使用 PMA层的块错误计数器 来进行误码性能测试。这些计数器是进行 BER(误码率)或 BLER(块错误率)测试 的基础。

🔹 1. Test Symbol(测试符号)的定义

一个 Test Symbol(测试符号) 是由 5 个连续的 PAM4 符号 组成的非重叠组。

因为每个 PAM4 符号携带 2 比特信息,所以 5 个 PAM4 符号 = 5 × 2 = 10 比特。

这些“测试符号”是用于误码检测的基本单位。将 5 个 PAM4 符号组合成一个“测试符号”,是为了便于对齐和统计错误。

🔹 2. Test Block(测试块)的定义

设有

p条物理通道(lanes),例如:如果是 4x50G = 200G 链路,则

p = 4如果是单通道 200G,则

p = 1

总共取

4 × 544 / p个连续的 test symbols。然后从中每4 个 取一个,组成一个 test block。

最终的 test block 包含:

544 / p个 test symbols。

🎯 这种“每隔4个取1个”的方式是一种 降采样(decimation)策略,用于:

减少数据处理量;

避免测试序列相关性;

实现跨通道的并行测试同步;

保证即使在多通道系统中,也能构造出合适大小的测试块用于统计。

📌 举例说明: 假设 p = 4(4 条通道):

每个 test block 包含

544 / 4 = 136个 test symbols原始序列取

4 × 136 = 544个连续 test symbols然后取其中第 1、5、9、... 个(即每第 4 个),共 136 个 → 构成一个 test block

🔹 3. Block Error Counters(块错误计数器)

对每条通道 i(i 从 0 到 p-1),定义 17 个错误统计计数器(bin counters),用于记录每个 test block 中发生错误的 test symbol 数量。

具体如下:

✅ test_block_error_count_i_k,其中 k = 0 到 15

这些计数器分别统计:在第 i 条通道上,有多少个 test block 包含恰好 k 个 test symbol 错误。

k=0:无错的块(完全正确)k=1:有 1 个 test symbol 出错的块...

k=15:有 15 个 test symbol 出错的块

✅ test_block_error_count_i_16p(这里的p是plus,也就是下图的Bin16+)

这个计数器统计:在第 i 条通道上,有多少个 test block 包含 16 个或更多 test symbol 错误。

它是一个“溢出桶”(overflow bin),用于收集高错误数量的块,避免计数器过多。

注:在多数实例中,只定义 17 个 bin:0~15 和 ≥16。

🔍 为什么这样设计?

这种计数器结构的设计目的包括:

目的 | 说明 |

|---|---|

精细错误分布统计 | 不只是统计总误码数,还能看到错误是集中在少数严重块中,还是均匀分布,有助于分析噪声类型(随机 vs 突发) |

支持 BLER 计算 | 块错误率(Block Error Ratio)通常定义为“至少有一个错误的块”的比例,可通过 |

兼容 FEC 分析 | 内层 FEC 能纠正一定数量的 symbol errors,因此知道有多少块超过纠错能力(如 >16 错误)非常重要 |

多通道独立监控 | 每个 lane 有自己的计数器,便于定位哪条通道性能较差 |

174A.8.3 PMA Error Histogram Measurement

该子条款描述了如何基于PMA层在测试过程中积累的计数数据,计算一组block错误直方图。这些直方图用于评估每条物理通道(lane)上的误码分布情况。

🔹 测量方法对于每条通道 i,按照以下步骤测量直方图![]() :

:

第

i条通道上,一个 test block 中恰好有k个 test symbol 出错的概率。

test_block_error_count_i_k:第i条通道上,包含 恰好 k 个 错误的 test block 数量。

test_block_total_count_i:第i条通道上总共分析的 test block 数量。

a) 生成测试码型

在发送端设备的PMA层生成 PRBS31 或 PRBS31Q 测试序列(前期猜测是对的,小开心)。

b) 识别错误位

在接收端的PMA层,使用 PRBS31 或 PRBS31Q 块错误检测器 从物理链路上识别出错误的比特。

c) 划分测试符号和测试块

将接收到的数据流划分为一系列的 test symbols 和 test blocks

d) 统计错误并更新计数器

对每个 test block,统计其中含有一个或多个比特错误的 test symbols 数量。

根据该 test block 中总的 test symbol 错误数量,递增相应的 bin 计数器。

e) 确定分析的test block总数

总共需要分析的 test block 数量由下方公式 (174A–1) 确定。

test_block_total_count_i:第i条通道上总共分析的 test block 数量。应足够大,以可靠地验证预期的BLER是否满足要求。

test_block_error_bin_i_16p:第i条通道上,包含 16个或更多 错误的 test block 数量。

test_block_error_count_i_k:第i条通道上,包含 恰好 k 个 错误的 test block 数量

可通过直接测量或统计投影来确定。

投影应能准确预测长期测试中会观察到的

值,或者至少提供一个上限。

值,或者至少提供一个上限。

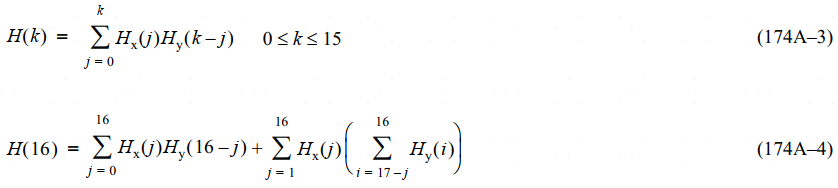

174A.8.4 Error Histogram Convolution

将两个错误直方图Hx(k)和Hy(k)合并成一个新的直方图 H(k)。

为什么需要卷积?

在高速以太网系统中,数据通常经过多级处理,每级都可能引入误码。例如:

数据先经过一个FEC编码器,然后通过物理链路传输,再经过另一个FEC解码器。

每个环节都有自己的误码特性,可以用一个直方图来描述。

为了评估整个系统的误码性能,需要将这些直方图合并起来,这就是卷积的作用。

计算举例:

下表中当2≤k≤16+时Hx(k)和Hy(k)都为0;

- H(1)=0.26

- H(2)=0.02H(2)=0.02

- 两个独立错误源卷积后,一个 test block 中恰好出现 1 个 symbol 错误的联合概率是 26%

- 恰好出现 2 个 symbol 错误的概率是 2%

| k | Hx(k) | Hy(k) |

|---|---|---|

| 0 | 0.9 | 0.8 |

| 1 | 0.1 | 0.2 |

| ... | ... | ... |

| 16 | 0 | 0 |

定义了一种通过卷积操作将两个17-bin错误直方图

Hx(k)和Hy(k)合并成新直方图H(k)的方法,包括:

卷积公式:对于

0 ≤ k ≤ 15使用公式 (174A–3),对于k = 16使用公式 (174A–4);应用场景:适用于多级FEC、多通道系统等复杂误码场景的分析;

数学意义:卷积操作反映了两个随机过程的联合概率分布。

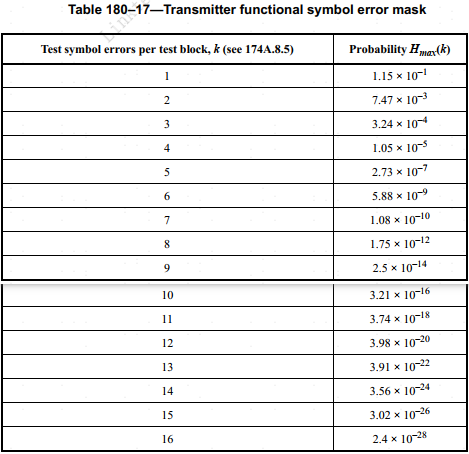

174A.8.5 基于PMA测量的误码分布模板测试方法

Error Mask Test Method Using PMA Measurements

该子条款描述了一种使用PMA层测量数据进行Error Mask Test的方法,用于独立评估每个物理lane的性能。通过比较测量得到的错误直方图与计算出的模板上限,可以确定是否满足预期BLER要求。

🔹 测试方法

a) 测量每条通道的错误直方图

对于每条通道

i,测量其错误直方图

这个直方图表示在该通道上,一个test block中出现

k个或更多test symbol错误的概率。

b) 计算上限直方图 H_max(k)

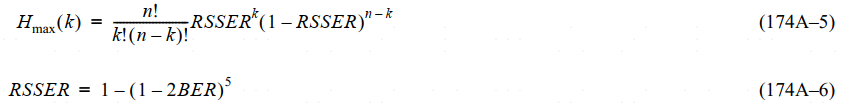

使用公式 (174A–5) 计算上限直方图

H_max(k),其中:n = 544 / p,p条物理通道(lanes);BER=BER_total-BER_added。

c) 比较直方图

如果对于每条通道

i,其 在所有

在所有 k > 0的情况下都小于Hmax(k),则认为该PHY或xMII Extender满足预期的块错误率要求。如果测试失败,可以通过174A.8.6子条款中的方法进一步验证性能。

示例计算

假设 BER_total = 1E-5,BER_added = 0,p = 1,则:

BER=BER_total-BER_added=1E-5RSSER=1-(1-2x(1E-5))^5≈1E-5n=544/1=544计算

Hmax(k),k = 1时:Hmax(1)≈0.0272

单lane 200G新增Transmitter functional symbol error histogram测试,后续展开解读

174A.8.6 基于 PMA 测量的所有lane BLER方法

Block Error Ratio Method for All Lanes Using PMA Measurements

该子条款描述了一种使用PMA层测量数据进行块错误率(Block Error Ratio, BLER)测试的方法,用于评估所有物理通道作为一个整体的性能。通过测量每个通道的错误直方图、计算BERadded的影响,并将这些直方图组合起来,最终确定整个通道组的块错误率。

🔹 测试方法

a) 测量每条通道的错误直方图

对于每条通道

i,测量其错误直方图

这个直方图表示在该通道上,一个test block中出现

k个或更多test symbol错误的概率。

b) 计算BERadded的错误直方图 Ha(k)

使用公式 (174A–5) 计算得到的 Ha(k) 作为初始值赋给 He(k)。

此处BER = BERadded

d) 迭代卷积复合错误直方图

对于每条通道

i,使用卷积函数hconv[He(k), ],将当前的复合错误直方图

],将当前的复合错误直方图 He(k)与该通道的测量直方图 进行卷积,并将结果重新赋给

进行卷积,并将结果重新赋给 He(k)。

e) 确定BLER

测量的BLER等于最终复合错误直方图

He(k)中k=16的值,即He(16)。

🔍 总结

174A.8.6的核心内容是:

定义了一种使用PMA层测量数据进行块错误率测试的方法,包括:

测量每条通道的错误直方图

,;

计算添加误码率的错误直方图

Ha(k);初始化复合错误直方图

He(k)为Ha(k);迭代卷积所有lane的复合错误直方图

He(k);确定块错误率BLER,测量值为

He(16)。

174A.8.7 基于 PMA 测量的单lane BLER方法

Block Error Ratio Method for a Single Lane Using PMA Measurements

定义了一种使用PMA层测量数据进行块错误率测试的方法,包括:

测量被测通道的错误直方图

,;

计算添加误码率的错误直方图

Ha(k);初始化复合错误直方图

He(k)为Ha(k);迭代卷积复合错误直方图

He(k)p次,p是lane数量;确定块错误率BLER,测量值为

He(16)。

个人理解:174A.8.7 和174A.8.6的区别是,

74A.8.6 看整体 BLER 是否达标

174A.8.7 假设所有 p 个通道都和 lane 1 一样差,然后看整体 BLER 是否达标