C5.5:VDB及后面的电路讨论

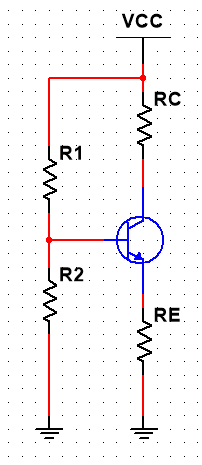

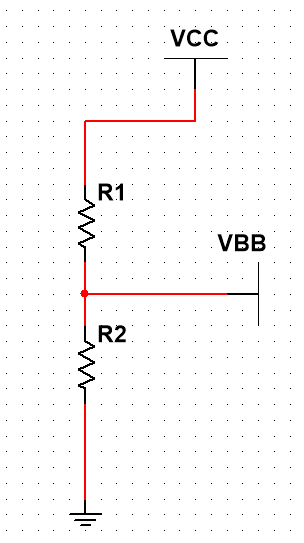

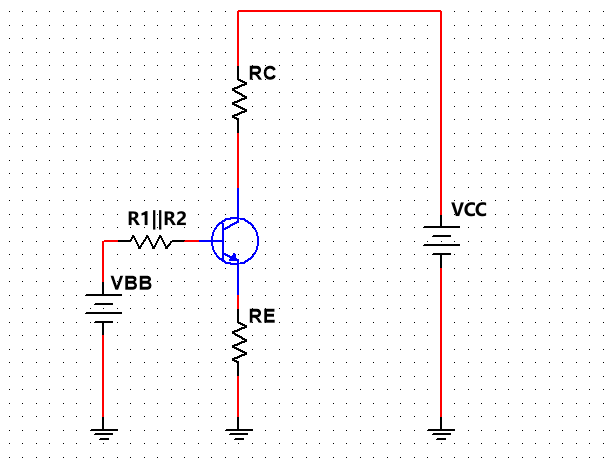

基极偏置电路里带了上拉电阻和下拉电阻来实现分压器的作用,这种分压器偏置的电路叫VDB电路,良好设计的VDB电路,基极电流远小于分压器电路的电流,所以可以忽略基极电流对分压器的影响,认为分压器和基极之间是开路,即得到下图。

则基极电压为VBB = (R2 / (R1+R2))*VCC

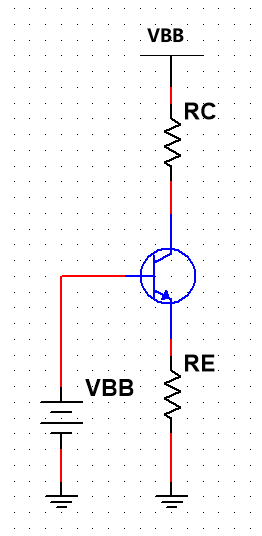

分压器偏置实际上是一种隐性的发射极偏置,可以说第上图第二张图,和最上面第一张图是等效的,因此VDB电路可以固定发射极电流,得到稳定的、与电流增益无关的Q点。

但是上述的简化是有误差的,关键在于如何设计VDB电路让误差很小。

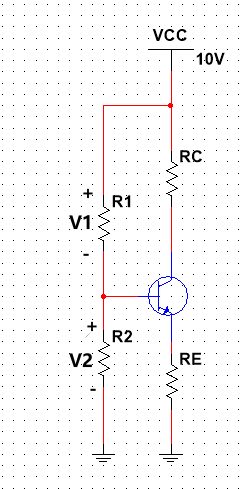

VB = (R2 / (R1+R2))*VCC

VE = VBB - VBE

IE = VE / RE

IC ≈ IE

VC = VCC - IC*RC

VCE = VC - VE

即通过分压器算出基极电压,通过基极电压再减去二极管压降,算出发射极电压,然后通过发射极电阻和电压算出发射极电流,然后通过集电极电流约等于发射极电流算出集电极电阻两端电压,得到了集电极对地的电压,然后通过集电极电压减去发射极电压,得到VCE。

而且由于VE ≈ IC*RE,所以VCE = VCC - IC*RC - IC*RE,即VCE = VCC - IC*(RC + RE)

即VCC减去集电极到地电压,再减去发射极到地电压,就是发射极和集电极之间的电压。

还记得前文提过内阻多大时,呈现准理想的电压源,而设计良好的VDB电路,就是分压器对基极输入电阻呈现准理想特性,所以当准理想电压源内阻RS < 0.01RL(负载电阻),就可以忽略该内阻的影响,所以分压器也是采用这个理论。

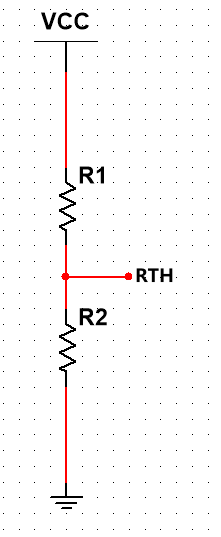

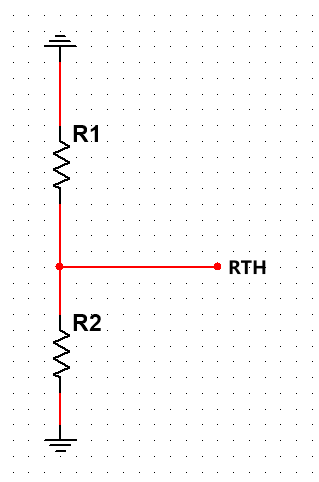

分压器的戴维南电阻如何计算?

答:戴维南定理指出,任何线性含源二端网络可等效为电压源(开路电压 Vth)与电阻(戴维南电阻 Rth)的串联。求 Rth时,需将所有独立电源置零(电压源短路→GND,电流源开路),所以R1上方的VCC变成GND,则为下图:

所以等效出并联的电阻,得出分压器的输出电压并不理想,更准确的分析应该考虑戴维南电阻,所以流过戴维南电阻的电流让实际基极电压低于理想值VBB。

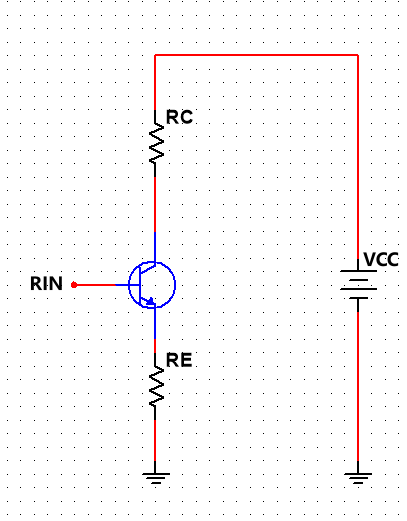

分压器需要为基极提供电流,而分压器负载电阻是RIN,为了让分压器对基极呈准理想性,则需要100:1准则,即RS < 0.01RL,也就是R1||R2 < 0.01RIN

假设电流增益为100,则集电极电流是基极电流的一百倍,而发射极电流也是基极电流的100倍,则基极角度来看,发射极电阻RE被放大了100倍(即,基极电阻比发射极电阻大100倍,电流才相同),所以RIN = βdc * RE,也可以写成R1||R2 < 0.01βdc * RE

但是这种比例会导致R1和R2阻值太小,不符合实际情况,会引发各种问题,所以采用10:1准则,即R1||R2 < 0.1βdc * RE,这种比例的分压器叫稳定分压器,比准理想情况差,但是在大部分应用是可以接受的(因为有合适稳定的Q点)。

而更精确的近似需要发射极电流,即IE = (VBB - VBE) / (RE + ((R1 || R2) / βdc))

这与准理想情况的值不同,因为多出来了(R1 || R2)/ βdc这一项,所以当这一项趋向于0的时候,这个公式则简化为准理想情况的值。

所以VDB电路受R1、R2、VCC、RC的控制,决定了饱和电流和截止电压,所以这四项控制了Q点的位置,且设计电路时,要考虑电路不会让晶体管的功率超过限定值。

根据上述的公式,并且VE = 0.1VCC,则R1 = (V1 / V2) * R2

所以Q点处于晶体管负载线的中点很重要,因为这样可以让放大器获得最大交流输出电压(因为该位置使输出电压在饱和失真和截止失真之间达到了最大对称动态范围,通过对称性规避饱和与截止失真),Q点处于负载线中点的偏置有时候也叫中点偏置。