Spyglass CDC basic concept

1. Waive

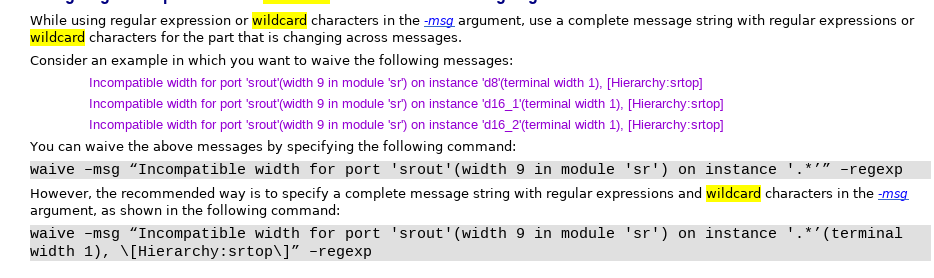

对于一些没有风险的vilation可以通过waive对齐进行屏蔽,除了-rule -excep -severith -file -file_lineblock -comment指定的参数值,对于其他参数它支持正则表达式 以及通配符匹配。它默认是处于通配符模式,如果想要使用正则表达式模式需要增加 “-regexp” 选项。对于waive -msg 中的会变化的message 使用通配和正则表达式是非常建议的。

- 通配符模式

通配符号支持 "?" "*",其中"*"可以匹配任何长度的字符串,"?"只可以匹配任意单一一个字符,如果想使用通配符号的原始意义,需要在其前面增加”\"转移符号。

waive -rule {xxx} -msg {reg* is not found} #这里可以匹配regA regAA regxdw

waive -rule {xxx} -msg {reg\* is not found } #这里是严格匹配reg*- 正则表达式

在正则模式下存在11个基础字符称之元字符,具体含义如下所示。* 只是代表任意多个的数量, . 表示任意一个字符 - 用在中括号中指定一个字符范围 [] 表示一个字符集合([0-9A-Z]代表任何大写字母和数字字符) ? 表示0或1个数量,但是实际使用需要 \?才能正确发挥元字符作用,怀疑spyglass支持仅是正则表达式,不支持扩展正则表达式。 ^ 锚定符,强制从开始匹配字符串 $ 锚定符,轻质匹配到结束 | 和逻辑或的意义类似,它允许在一个表达式中将两个子表达式组合 () 用于将字符串中的匹配部分分组,但是实际使用需要 \(\)才能正确发挥元字符作用。 \ 转移字符,它用于将元字符视为原始字符

- 正则表达式

2. clock传播

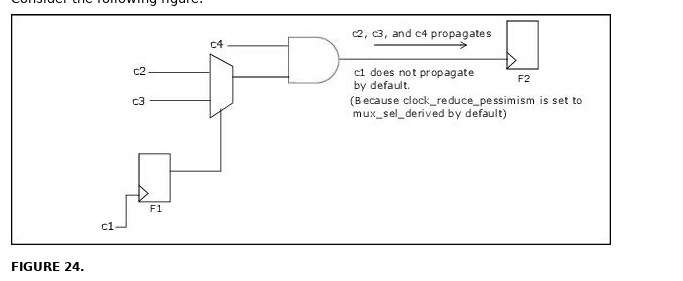

spyglass 提供了clock_reduce_pessimism参数用于控制clock的传播。

- mux_sel

当使能改参数,则时钟复用器选择端口的时钟信息汇聚到输出端

- all_potential_clocks

它可以推断出”use_inferred_clocks“为成功推断的时钟。当spyglass识别到组合逻辑门,且其中一个输入为时钟,则会自动推断另一个输入端口也是时钟。

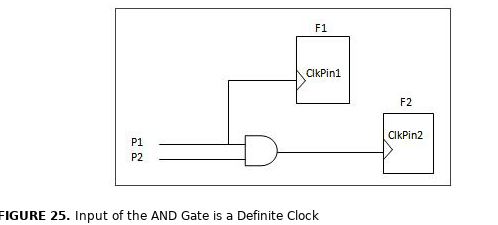

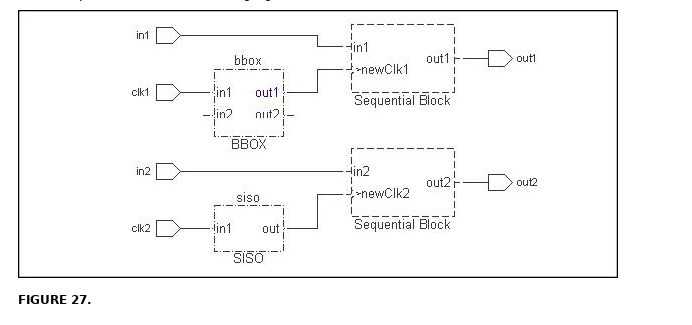

- single_input_output_bbox

默认情况下单输入单输出黑盒的输出端口并不会被识别为时钟,只有多输入黑盒的输出端口才认为是时钟。如下图所示,如果没有使能该参数,clock_info01 规则报告newclk1是备选时钟。如果使能这个参数,clock_info01规则报告newclk2是一个备选时钟。

在这种情况下,倘若use_inferred_clocks设置yes,Propagate_clocks规则报告newclk2已经传递到下一个时钟;如果SISO的输入是一个时钟,clock_check07规则会报告clk2已经传播到了另一个时钟域(newclk2),终止了clk2传播。究其原因是工具自动推断到newclk2是新时钟,并创建了新的domain,因此此时clk2传播到newclk2就停止了。

- stop_derived_at_random_logic

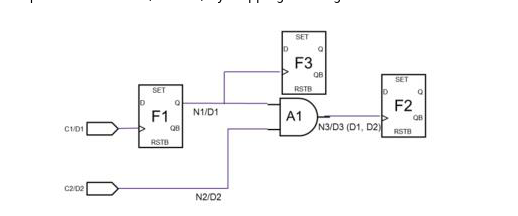

stop_derived_at_random_logic参数会影响时钟的propagation,只有当时序单元输出直接或者通过clock_gate、MUX、BUffer、Inverter连接到DFF的时钟端口。此时该端口才会推断输出口是时钟。

如下图所示,如果时序端口F1输出连接到多个DFF的时钟端口,因此此时时序单元的输 出被工具推断出是clock,并传播到后续的DFF。

如果disable_seq_clock_prop, enable_generated_clocks使能之后,主输入时钟是无法穿越到时序单元的。如果在时序单元的输出口创建了generated_clock约束,则无论stop_derived_at_random_logic是哪个参数,该派生时钟则会继续向后传播。

如果时钟mux没有设置case_analysis,则mux输出端口除了输入口传播的时钟,还有生成一个输入口时钟组合的新时钟。 如果通过spyglass generated_clock在时钟mux输出口创建了新时钟,则mux输出口只会存在新创建的时钟,组织了输入口时钟的传播。