模拟IC设计基础系列8-版图设计基础

1. 模拟电路设计绪论

2. MOS器件物理基础

3. 单级放大器

4. Cascode stage 共源共栅结构分析与计算

5. MOS电路中的电流镜设计

6. 差动放大器 Differential AMP

7. MOS电路的频率响应与米勒效应

8. 版图设计基础

8.1 各层级解释

下图为cadence版图绘制界面截图

下表为图中各层级的定义和作用

| 层级 | 缩写 | 中文名 | 定义与作用 |

|---|---|---|---|

| 有源区与阱层 | AA (Active Area) | 有源区 | 定义:有源区(晶体管源/漏/沟道区域),通常是硅衬底上的掺杂区域,由光刻和浅沟槽隔离(STI)工艺定义。 作用:与GT层(栅极)交叉形成MOS管,未覆盖部分为场氧(隔离区)。 |

| NW (N-Well) | N阱层 | 定义:N型阱,用于PMOS管或隔离NMOS,通常在P型衬底上形成。 作用:为PMOS器件提供N型区域;在双阱工艺中,与P阱共同支持NMOS和PMOS器件。 | |

| PW (P-Well) | P阱层 | 定义:P型阱,用于NMOS管,通常在N型衬底或双阱工艺中形成。 作用:为NMOS器件提供P型区域,与NW层配合实现CMOS结构。 | |

| 栅极与注入层 | GT (Gate Terminal) | 栅极 | 定义:晶体管的栅极层,通常为多晶硅或高K金属栅(HKMG)。 作用:与AA层交叉形成晶体管沟道,栅极宽度决定沟道长度(L)。 |

| SN (N+ Selective Implant) | N选择性注入 | 定义:N型高浓度掺杂层,用于NMOS源/漏区,通常包括轻掺杂漏(LDD)区域。 作用:形成低电阻源/漏区,与AA层对齐以确保接触性能。 grazier | |

| SP (P+ Selective Implant) | P选择性注入 | 定义:P型高浓度掺杂层,用于PMOS源/漏区,通常包括轻掺杂漏(LDD)区域。 作用:形成低电阻源/漏区,与AA层对齐以确保接触性能。 | |

| 接触与金属互连层 | CT (Contact) | 接触层 | 定义:接触孔,连接有源区/栅极与第一层金属(M1),通常使用钨(W)填充并结合硅化物工艺。 作用:实现硅/多晶硅与金属的欧姆接触,降低接触电阻。 |

| M1, M2, M3, M5 (Metal Layers) | 金属互连层 | 定义:金属互连层(M1为第一层金属,M2为第二层,依此类推),通常为铜或铝。 作用:用于信号和电源布线,高层金属(如M5)常用于全局供电或长距离互连。 | |

| V1, V2 (Via Layers) | 通孔层 | 定义:通孔层,连接不同金属层(如V1连接M1-M2),通常为钨或铜填充。 作用:实现金属层间的垂直互连,确保信号和电源传输。 | |

| 特殊器件层 | MIM (Metal-Insulator-Metal Capacitor) | 金属-绝缘体-金属电容器 | 定义:金属-绝缘体-金属电容,用于高精度模拟或RF电路。 作用:提供高密度电容,用于滤波、振荡器等电路。 |

| MIMDMY (MIM Dummy) | MIM虚设结构 | 定义:MIM电容的虚拟结构,用于工艺均匀性。 作用:改善制造过程中电容区域的平坦度和一致性。 | |

| MIMCKT (MIM Circuit Marking) | MIM电路标识层 | 定义:MIM电容的电路标识层,用于布局验证(LVS)。 作用:辅助设计验证,确保MIM电容正确集成。 | |

| MOSCKT (MOS Circuit Marking) | MOS电路标识层 | 定义:MOS器件的电路标识层,用于标注特殊器件(如高压MOS)。 作用:便于电路设计和验证,区分不同类型的MOS器件。 | |

| 测试与辅助层 | TV1 (Test Via 1) | 测试通孔1 | 定义:测试用通孔,用于工艺监控或调试。 作用:验证通孔电阻和连接可靠性。 |

| MTT2 (Metal Test Structure 2) | 金属测试结构2 | 定义:金属测试结构,用于评估工艺可靠性(如电迁移)。 作用:监控金属层的长期稳定性和制造质量。 | |

| VSIA (Virtual Silicon Interface Annotation) | 虚拟硅接口标注 | 定义:虚拟硅片接口标注,用于IP核集成或可制造性设计(DFM)。 作用:优化IP模块与主设计的兼容性,确保制造一致性。 | |

| 总结 | 核心层:AA(有源区)、GT(栅极)、CT(接触孔)、Mx(金属层)构成基本互连结构。 特殊器件层:MIM、MIMDMY等用于模拟/RF电路。 辅助层:SN/SP(掺杂)、TV1/MTT2(测试)、VSIA(接口)等确保工艺和功能可靠性。 |

下图为各层级的结构示意图

8.2 详细流程总体介绍

下图为加工完成后的工艺总视图

8.3 PMOS加工详细流程介绍

正胶光刻后消失,反胶光刻后不消失

- P衬底加工N阱(Nwell),使用正(光刻)胶

- 刻蚀二氧化硅

- N阱注入,注入磷(P,外层5个电子,1个电子自由)

- 生长SiO2及氮化硅,涂光刻胶(反胶)

- 使用有源区掩膜(Mask-Active),进行有源区光刻(反胶)

- 氮化硅刻蚀

- 场氧(Field Oxide,FOX)生长,去掉氮化硅

- 薄栅氧生长

- 多晶硅沉积(Polysilicon)以形成栅氧,涂光刻胶(反胶)

- 栅极掩膜,光刻以剩下栅氧

- polysilicon刻蚀,去掉多余的polysilicon

- 涂光刻胶(正胶)

- 掩膜刻蚀,实现N+光刻

- N+离子注入

- N+加工完成

- 涂光刻胶、P+光刻

- P+注入

- P+注入完成

- 厚氧化层沉积

- 接触层光刻(正胶)

- 厚氧化层刻蚀

- 电极金属钨沉积

- 金属层沉积,涂光刻胶,M1金属层光刻(反胶)

- M1刻蚀

- M1互连。到此为止,PMOS器件结构绘制完成

- 高层金属互连。基础层(CT)、互连层(Via)。

8.4 物理验证

包括设计规则检查(Design Rule Check,DRC)和版图与原理图图(Layout Versus Schematic,LVS),DRC检查走线是否符合加工要求,LVS检查版图是否与原理图一致

DRC与LVS检查流程

DRC检查规则与示意图

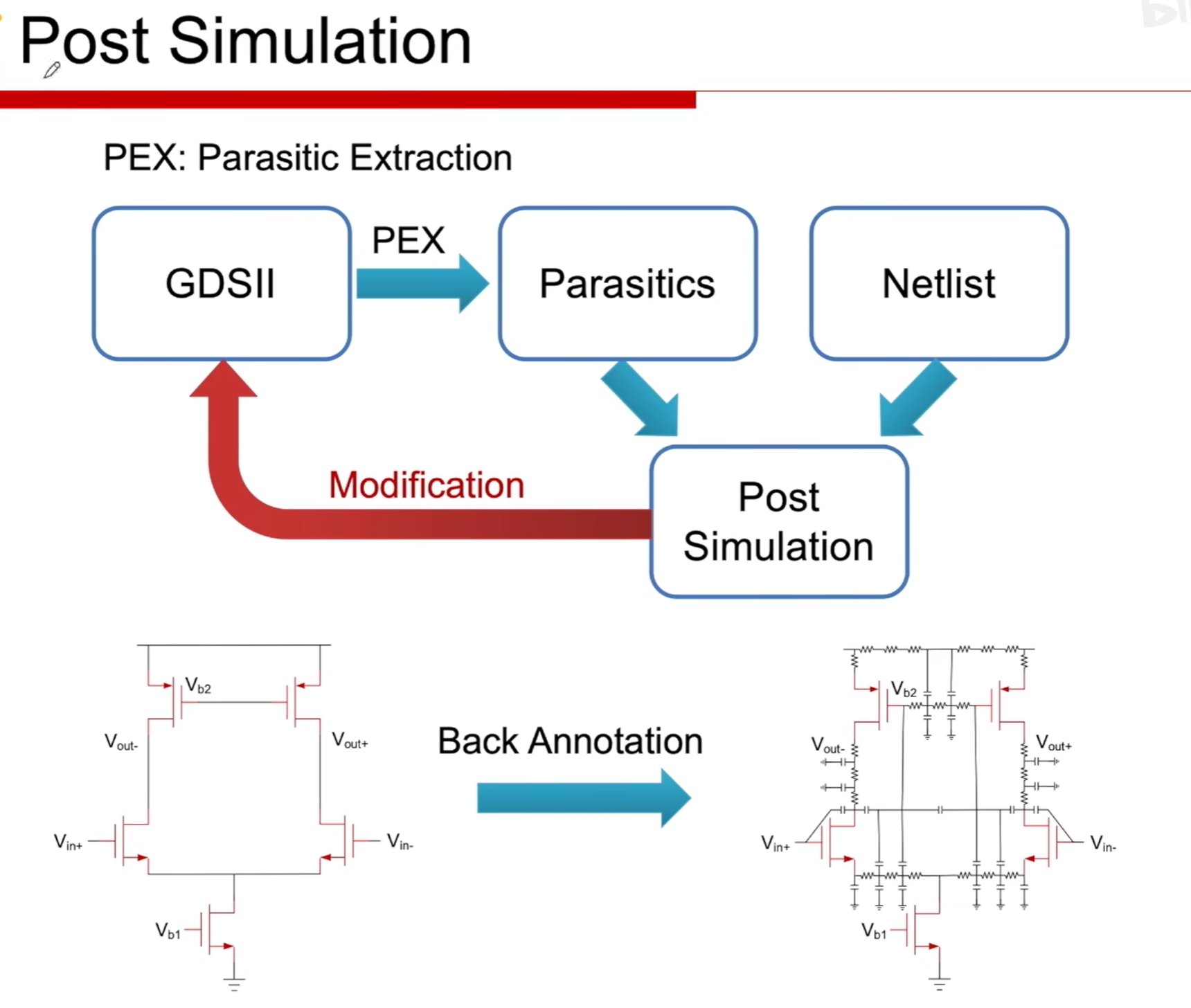

8.5 后仿真(Post simulation)

后仿需要对GDSII文件抽取寄生参数,然后将寄生参数反标到网表上,再次进行检查。

8.6版图绘制快捷键

参考

1.【集成电路版图设计技术更新版】https://www.bilibili.com/video/BV1dL411n7c2?p=2&vd_source=fb39f0e2d38a644c87834f3a6c240f6c