实战案例-FPGA如何实现JESD204B确定性延迟

目录

1.JESD204B原理概述

204B 的分层

传输层(Transport Layer)

链接层(Link layer)

物理层(Physical layer)

2.如何在FPGA中实现最小确定性延迟

弹性缓冲器实现

接收延迟

RX端到端延迟

ADC Timing

JESD204B核心延迟

计算端到端延迟

步骤1:确定需要的LMFC周期数(N)

步骤2-使用N计算端到端延迟

计算案例:

1.JESD204B原理概述

204B 的分层

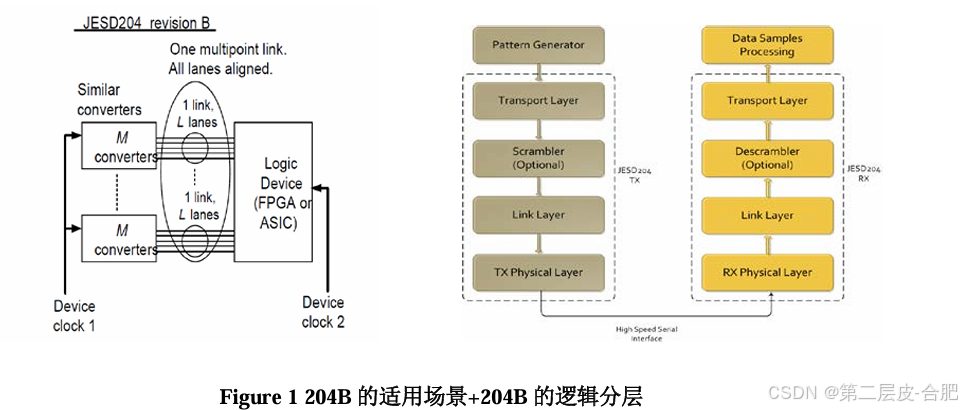

JESD204B 是一种高速的串行接口协议,它规定了收发双方的同步机制,告警机制及其告警后处理机制。 任何一种复杂的接口协议都将遵从逻辑架构分层来进行描述。 JESD204B 也是如此,其遵从如下的逻辑分层(右图)。

图1分别给出了204B适用的范围/对象(左边)和204B的逻辑分层(右边)。其中TX侧对应的是FPGA/ASIC 或者ADC,RX 侧对应的是FPGA/ASIC 或者DAC。 204B的所有相关动作的描述都将依据其分层来进行描述,所以理解和掌握分层是了解204B的基础,下面将对各个层的功能/原理做一个简单的描述:

传输层(Transport Layer)

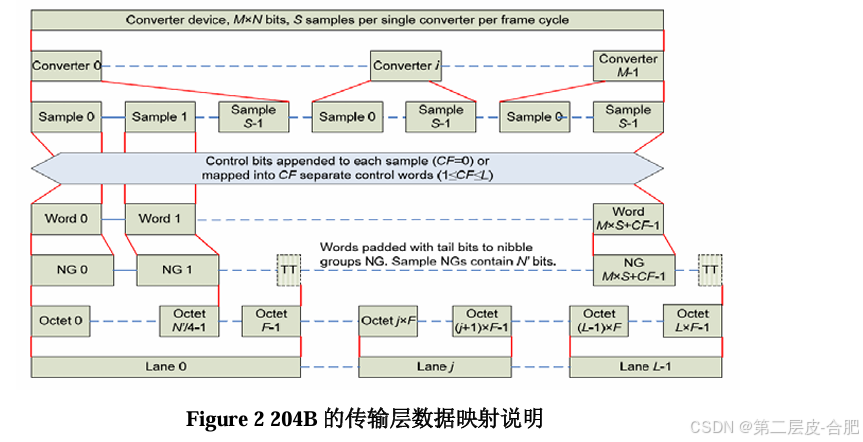

传输层的功能是将AD/DA的采集到的数据映射到非扰码的八字结的过程(The transport layer maps the conversion samples to non-scrambled octets)。

204B 协议规定了几种映射模式。

A single converter to a single-lane link

Multiple converters in the same device to a single-lane link

A single converter to a multi-lane link

Multiple converters in the same device to a multi-lane link

上述的四种模式是两个对象的几种组合,一个是数据转换器的个数,另外一个是对应的link的个数。 数据转换器就是对应的I/Q的数据组,例如我们无线系统中都是采用complex数据有16bits 的I 也有16bits的Q,那么对应的转换器就是2,就类似I数据需要一个转换器来完成,Q数据需要一个转换器来完成(注意这里的转换器的个数和我们通常所说的物理的ADC/DAC数据有区别,可以抽象为一个吞吐数据器件)。 通常情况下我们转换器的个数都是多个(多通道),这些转换器的数据可以一起来建链称之为单link也可以分组建链称之为多link。 所以下面将于常用的Multiple converters in the same device to a multi-lane link来说明。

在传输层映射过程中会用到几个参数:

• CF: Number of control words per frame clock period per link.

• CS: Number of control bits per conversion sample.

• NG: Nibble Group(group of half octets).

这三个参数会影响到映射的过程,但实际的过程中往往没有这些控制字,同时也不需要插入nibble数据,所以会比较简单。 这些数据的映射过程和排列过程会体现在JESD的LMFS 等配置中,一般数据手册中都会给出我们支持的模式说明。

链接层(Link layer)

链接层在再整个204B中占有及其重要的地位,是204B的核心。 它包含了8B/10B的编码过程, TX和RX 键链(link establishment)过程。下面会专门描述204B的键链过程。

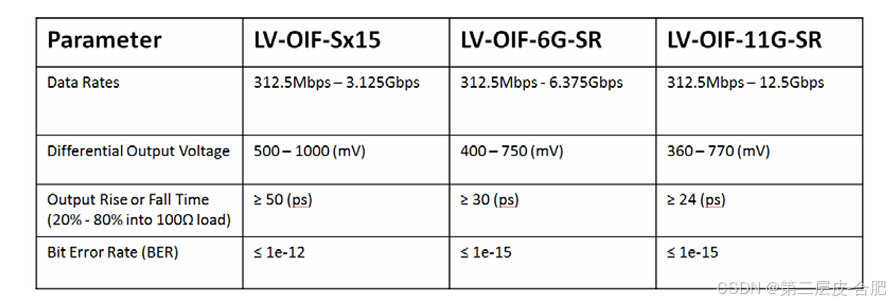

物理层(Physical layer)

物理层包含了完成高速并/串转换的SDRDES 模块, 时钟及时钟数据恢复模块(CDR)。 物理层也规定了接口的物理电器特性如下表所示。

2.如何在FPGA中实现最小确定性延迟

弹性缓冲器实现

在JESD204B设备中,接收通道对齐弹性缓冲区是在分布式RAM中实现的。您可以通过调整GUI中的“LMFC缓冲区大小(每个多帧的最大字节数)”值来选择缓冲区的大小。该值应设置为能够容纳一个完整多帧数据的大小。

接收延迟

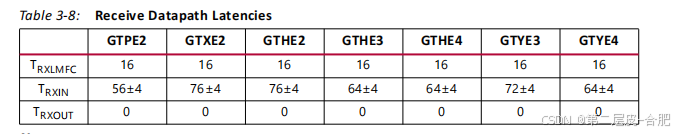

延迟变化对JESD204B系统至关重要。IP核心的延迟是固定的(用户可以控制其变化,详情请参阅《最小确定性延迟支持》),但收发器引入了一些延迟变化,因为收发器的内部接收弹性缓冲区被包含在数据路径中。接收数据路径的延迟见表3-8。核心会自动补偿这些延迟变化,确保整个端到端的延迟没有变化。

RX端到端延迟

JESD204系统中的总延迟需要考虑链路中各种固定和可变延迟的来源。

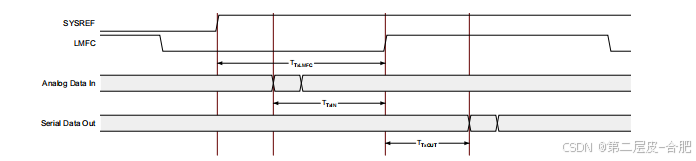

ADC Timing

计算端到端延迟所需的ADC关键参数包括:

1.从SYSREF到LMFC的固定延迟(TTXLMFC);

2.从模拟输入到LMFC的固定延迟(TTXIN);

3.从LMFC到JESD204串行输出的延迟(TTXOUT)。

对于Subclass 1设备,从SYSREF到LMFC以及模拟数据进入LMFC的延迟必须保持固定,而从LMFC到JESD204串行数据输出的延迟可以有所不同,因为这一延迟在接收器与LMFC对齐时已经进行了补偿。

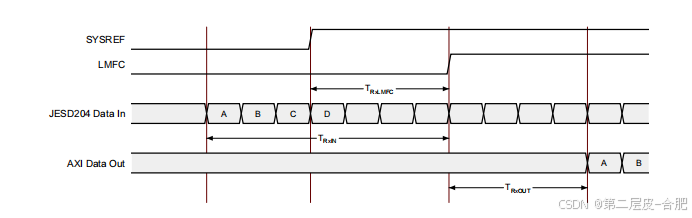

JESD204B核心延迟

FPGA接收器计算端到端延迟的关键参数包括:

1.SYSREF到LMFC(TRXLMFC)的固定延迟;

2.JESD204输入到LMFC(TRXIN)的延迟;

3.LMFC到AXI数据输出(TRXOUT)的固定延迟。

对于Subclass 1设备,从SYSREF到LMFC以及从LMFC到AXI数据输出的延迟必须保持固定,而JESD204串行数据输入到LMFC的延迟可以有所不同,因为接收器缓冲区会补偿端到端延迟的变化。在延迟计算中,TRXOUT设为0,所有固定延迟都包含在TRXLMFC中。

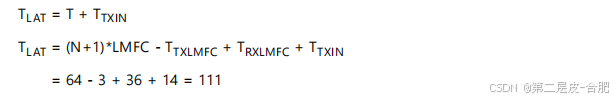

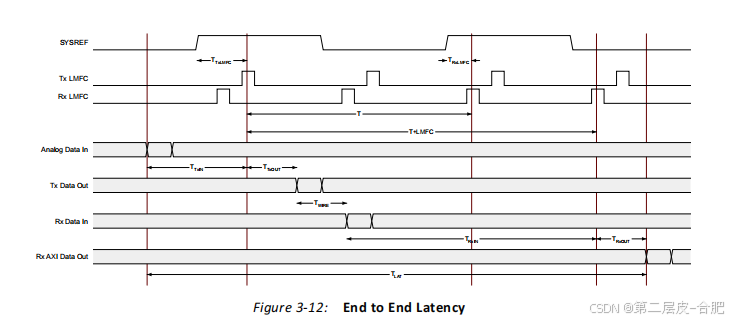

计算端到端延迟

端到端延迟始终是固定的,由多个LMFC周期加上固定的发送和接收延迟组成。要计算端到端延迟

步骤1:确定需要的LMFC周期数(N)

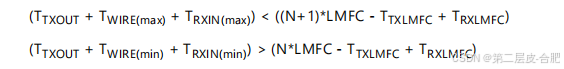

TX端LMFC与RX端LMFC(T)之间的延迟为由SYSREF到TX和RX的内部延迟调整的LMFC周期数(N):

![]()

为确保系统重启之间的总传播延迟保持恒定,最大传播延迟必须小于T加一个LMFC周期:

![]()

于是:

如果接收到的数据接近接收LMFC边界,且由于链路变化导致数据在系统重置后刚好落在边界前或边界后,可能无法找到有效的N值。这将表现为系统重启之间恰好一个LMFC周期的延迟跳跃。如果找不到有效的N值,可以通过调整SYSREF信号的相对延迟来移动接收LMFC边界相对于发送LMFC边界的位置。对于每个增加的TX SYSREF延迟周期,TTXLMFC值应增加4。为了实现这一点,可以在JESD204核心中对SYSREF处理添加额外的延迟;

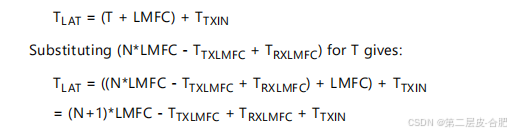

步骤2-使用N计算端到端延迟

数据在N个LMFC周期后和N+1个LMFC周期前接收,因此最小确定性延迟为T加上一个LMFC周期,再加上FPGA的固定输入延迟和DAC的固定输出延迟:

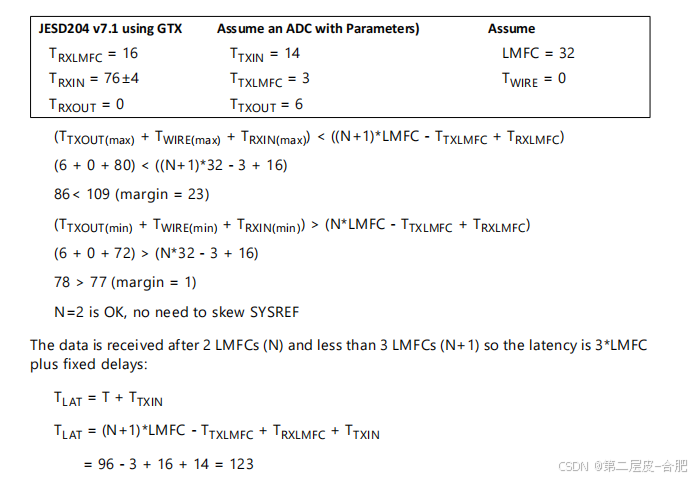

计算案例:

请注意,在这种情况下,数据到达接收LMFC后的延迟(即数据到达的时间)非常短(仅为1字节周期)。任何由ADC或ADC与FPGA之间的连接引入的延迟都可能导致数据提前到达,从而在LMFC边界之前接收到数据。由于在第三个LMFC之前还有足够的延迟,因此建议将发送LMFC的时间推迟1或2个周期,以增加延迟时间,提高数据接收的可靠性。

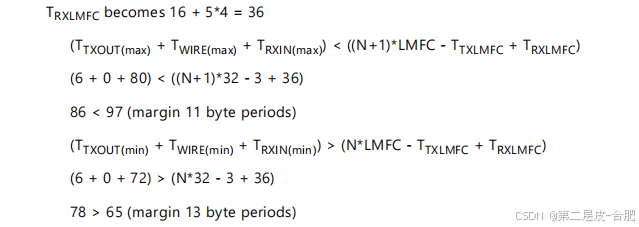

如果无法延迟TX LMFC,则RX LMFC可延迟5个周期,N减少1,如下所示:

最小延迟和最大延迟的边缘数值相近,这意味着系统在接收多帧边界接近接收LMFC周期中心时运行;这减少了因链路延迟变化导致延迟变化的可能性。数据在接收到一个LMFC(N)之后且少于两个LMFC(N+1)后被接收,因此延迟为2*LMFC加上固定延迟: