电流舵DAC设计(二)

通过面积、DNL/INL、THD等性能指标的折衷,采用混合编码方式,进行了最优的分段。电流舵DAC性能受器件噪声、器件失配、电流源有限输出阻抗、电源电压波动等非理想因素影响的,需要仔细分析。

电流源一般采用 PMOS Cascade 结构。电流源采用 PMOS 管的好处是空穴迁移率比电子迁移率低,其与同一尺寸的 NMOS 管相比,1/f 噪声低很多。又知 PMOS 管做在 N 阱里面,能有效隔离电路其他模块的串扰影响。

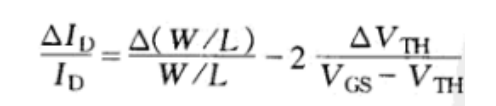

电流镜失配公式为:

所以要减小电流镜失配,要加大尺寸,增大VGS-VTH。管子面积的增大,又会导致寄生电容的增大,使得电路速度降低,同时整个芯片的面积也会增大,面积增大会导致晶体管之间的距离增加,长距离效应增加电流镜的失配,这就需要在确定电流源管子尺寸时在失配、速度和面积之间综合考虑。

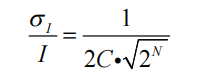

在 DAC 设计前性能指标已经规划好,INL 的大小也已给出,则电流源相对误差和 INL之间的关系为

C=inv_norm(0.5+yield/2), inv_norm 是正态分布反积分函数,N 为 DAC 的位数,yield 一般被称为成品率,它表示量产的芯片中 INL 小于 0.5LSB 的成品比例。下图描述了成品率与电流源匹配误差之间的关系。