SAR ADC 同步逻辑设计

SAR ADC的逻辑是重要的一个模块,可以分为同步逻辑和异步逻辑,对于低速SAR ADC,一般采用同步逻辑,对于高速SAR ADC,一般采用异步逻辑。

对于同步逻辑,由于架构不同,有先置位再比较,也有先比较再置位这两种架构,所以逻辑设计也不尽相同。

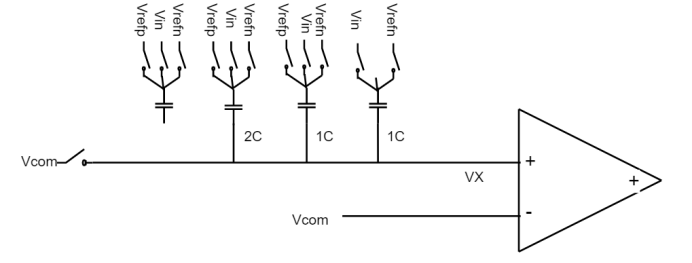

这里用单端10bit SAR ADC的架构做例子。逻辑是同步逻辑,同时是先置位再比较的逻辑。

首先逻辑分三个阶段,需分为这几个逻辑功能

1)采样阶段:给出ADC转换开始信号,另外包含比较器的offset校正

2)比较阶段:先置位再校正,如果正确,则置位不动,如不对,需要置位改变。

3)结果输出阶段:把结果输出,并产生比较结束信号

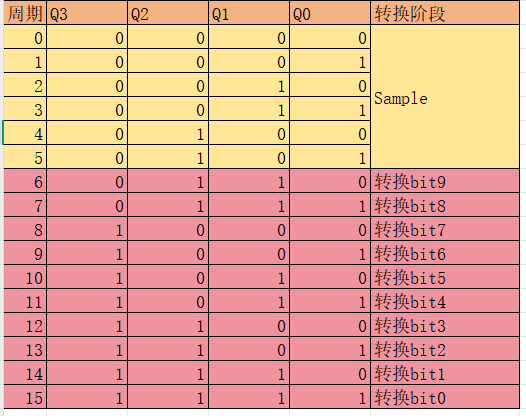

这里可以用一个计数器来定义3个阶段,其中周期0/1/2/3/4/5为采样周期(offset校正周期),这个可以用卡诺图得到采样周期的控制信号,周期0/1/2/3/4/5采样周期为高,其它数字低。其中转换开始信号可以作为计数器的复位信号,这个可以由外部给出,复位信号拉高计数器开始计数。另外,第6个周期可以作为转换bit9的转换周期,依次类推,到第15个周期可以作为转换bit0的转换周期。

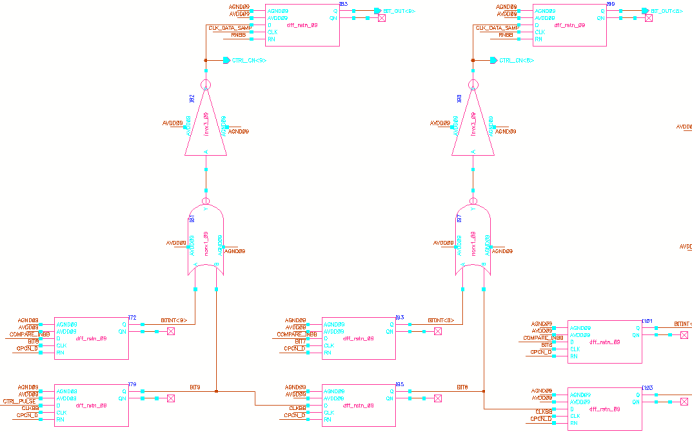

上图是转换阶段的实现:第6~15个周期进行先置位再比较的逻辑。看I79模块,CTRL_PULSE是第5个周期为高电平,其它周期均为低电平,这样通过CLKBB用dff打一拍后,得到BIT9,这样BIT9在第6个周期为高电平,这样使控制逻辑CTRL_CN<9>就为高电平;看I72模块,COMPARE_INBB为比较器输出,下一拍第7个周期,BIT8在第7个周期为高电平,其它为低电平。这样用BIT8打拍COMPARE_INBB得到BITINT<9>,此时BIT9在第7个周期为低电平,所以CTRL_CN<9>的输出取决于BITINT<9>,如果为1,则维持置位,如果为0,则重新置位为0.与此同时,看I95,由于BIT8第7个周期为高电平,相当于给CTRL_CN<8>置高电平,跟bit9一样,进行bit8的置位,比较,再重新判断置位。依次类推,直到bit0结束。

结果输出阶段:通过把第15个周期的pulse(第15个为高电平,其它周期为低电平)。第15个周期的pulse通过延时并与它的反向与得到I99的时钟信号CLK_DATA_SAMP,用这个信号把比较结果打一拍,并并行输出,同时此信号也可以作为转换结束的信号。

这样就基本上完成了SAR ADC的同步逻辑设计。