计算机组成原理——主存与CPU的连接

3.3主存与CPU的连接

整理自up主Beokayy_传送门在此

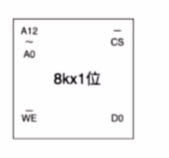

1.单个芯片

- A0~A12:

- 地址线。

- 8 k = 2 3 × 2 10 = 2 13 8k = 2^3×2^{10} = 2^{13} 8k=23×210=213,故地址线有13根。

- 若 2 n 2^n 2n,则地址线有n根。

- D0:

- 数据线。

- 1位,故数据线有1根。

- 若n位,则数据线有n根。

- WE:

- 读写控制信号。

- CS:

- 片选信号。

主存容量扩展

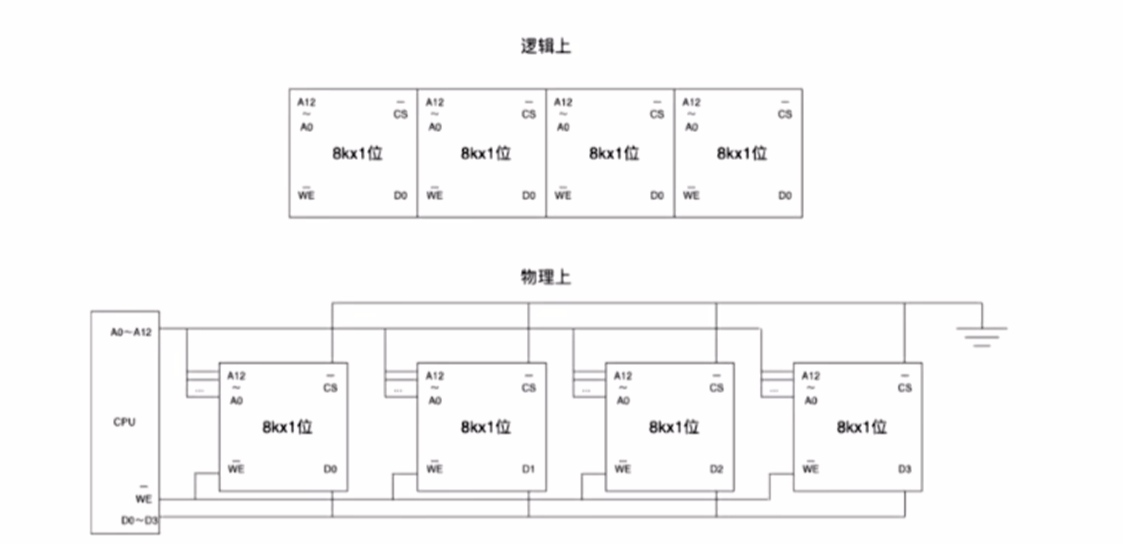

位扩展

- CPU的数据线与芯片的数据位数不一定相等,为了不浪费数据线,必须对芯片进行位扩展,使其位数与CPU的数据线根数相等。

- 位扩展就像把芯片粘在一起,例如用8片8K×1位的芯片构成8K×4位的存储器,需要在位方向上扩展4倍,而字方向上无需扩展。

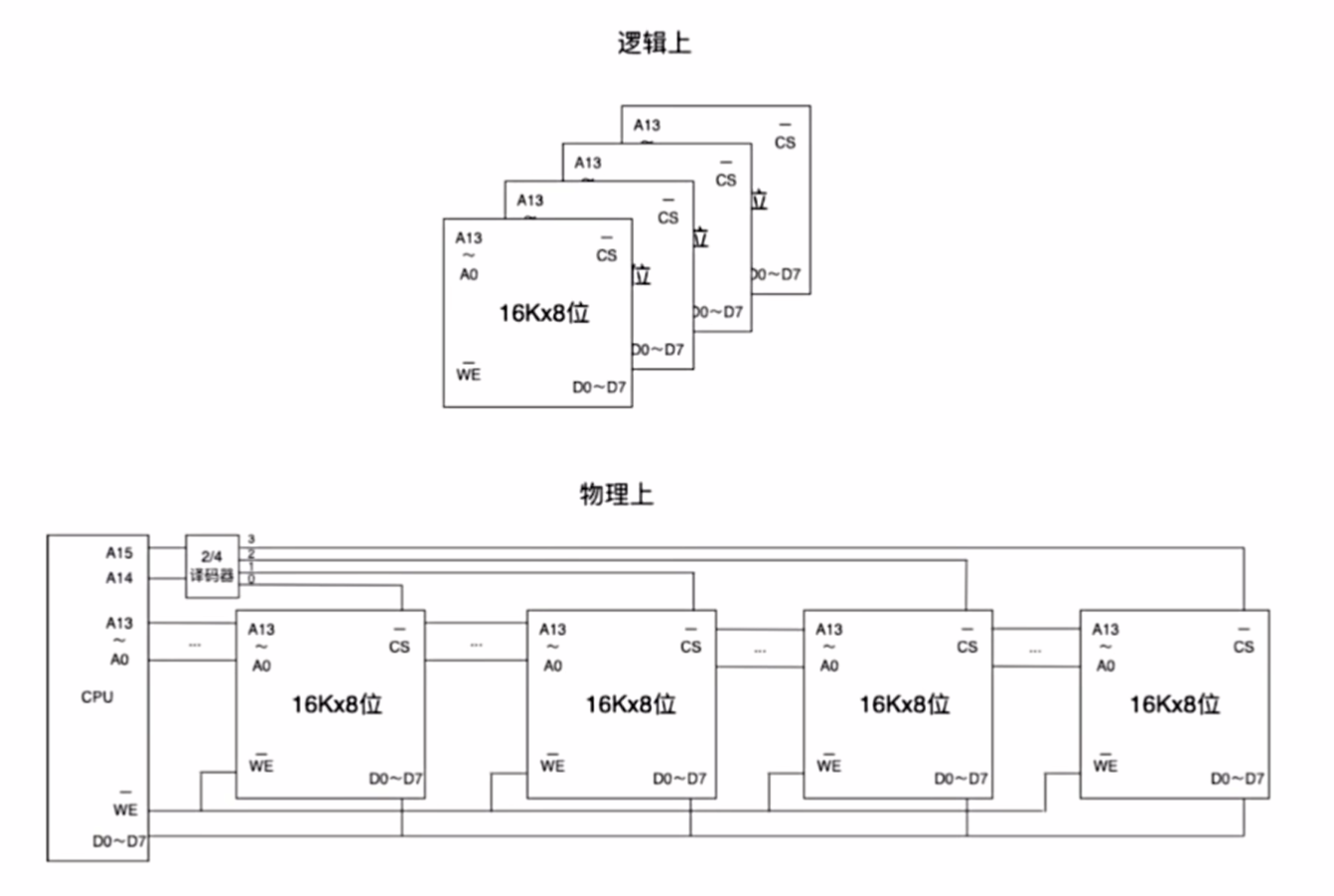

字扩展

- 增加存储器中字的数量,即增加存储单元的数量,而位不变。

- 字扩展就像把芯片组成一组,例如用4片16K×8位的芯片组成64K×8位的存储器,需要在字方向上扩展4倍,而位方向上无需扩展。

- A14和A15作为片选信号,A15A14=00时,选中最左边的1号芯片,A15A14=01时,选中2号芯片,以此类推。

- 各芯片的地址范围:

- 1号芯片:00 0000 0000 0000 00~00 1111 1111 1111 11

- 2号芯片:01 0000 0000 0000 00~01 1111 1111 1111 11

- 3号芯片:10 0000 0000 0000 00~10 1111 1111 1111 11

- 4号芯片:11 0000 0000 0000 00~11 1111 1111 1111 11

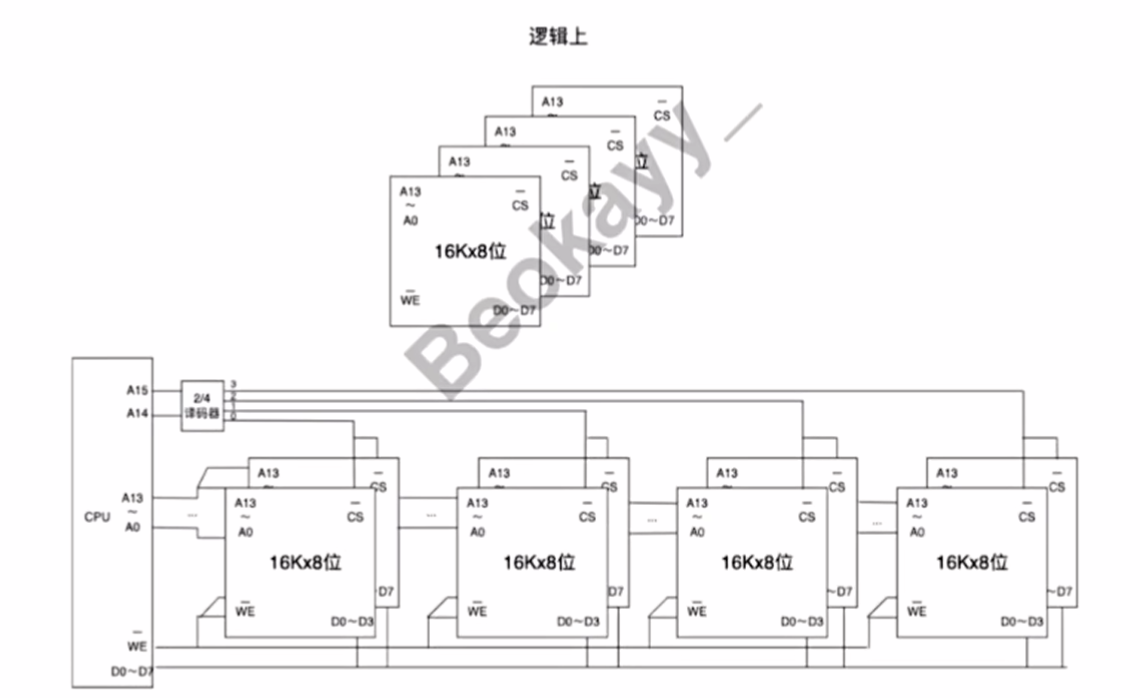

字位扩展

- 同时扩展字和位,逻辑上相当于多个芯片先粘在一起,再组成组。

- 例如用8片16K×4位的RAM芯片组成64K×8位的存储器,每2片构成一个16K×8位的存储器(位扩展),4组构成64K×8位的存储器(字扩展)。

3. 芯片的选择

线选法

- 使用除片内寻址外的高位地址线,分别连接各个存储芯片的片选端。

- 当某地址线为“0”时,就选中与之对应的存储芯片:

| 芯片 | A14~A11 |

|---|---|

| 0号 | 1110 |

| 1号 | 1101 |

| 2号 | 1011 |

| 3号 | 0111 |

- 线选法的片选地址线每次选片时只能有一位有效,不允许多位同时有效,这样才能保证每次只选中一个芯片。

- 地址空间不连续,造成地址资源的浪费。

译码片选法

- 使用除了片内寻址外的高位地址线通过地址译码器芯片产生片选信号