数字电子技术基础(五十七)——边沿触发器

目录

1 边沿触发器

1.1 边沿触发器简介

1.1.1 边沿触发器的电路结构

1.3 边沿触发的D触发器和JK触发器

1.3.1 边沿触发的D型触发器

1.3.2 边沿触发的JK触发器

1 边沿触发器

1.1 边沿触发器简介

对于时钟触发的触发器来说,始终都存在空翻的现象,抗干扰的能力较差,同时时钟控制的触发器的透明窗口会导致时序分析复杂化,在多级级联时可能引发竞争冒险。因此为了提高触发器的可靠性,可以改变电路的触发方式。

在时钟电路的上升沿或者下降沿到达的电路时刻,才会接受数据端的信号,并且完成数据状态的改变,在其他时间都会保持电路的稳定。边沿触发器是现代时序电路(例如CPU、存储器等)的核心组件。

1.1.1 边沿触发器的电路结构

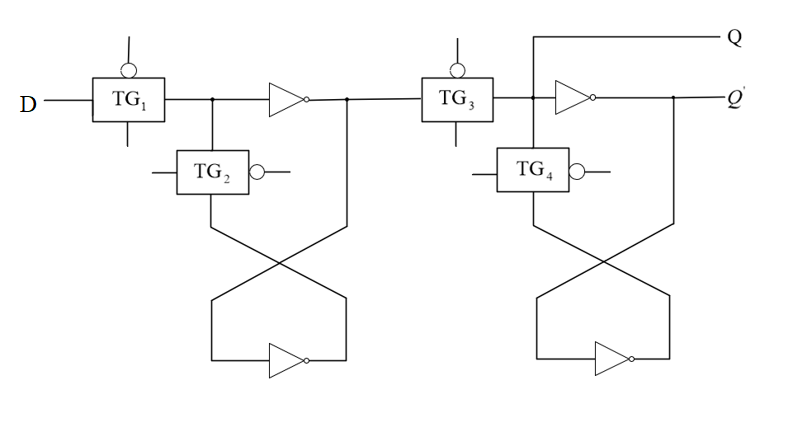

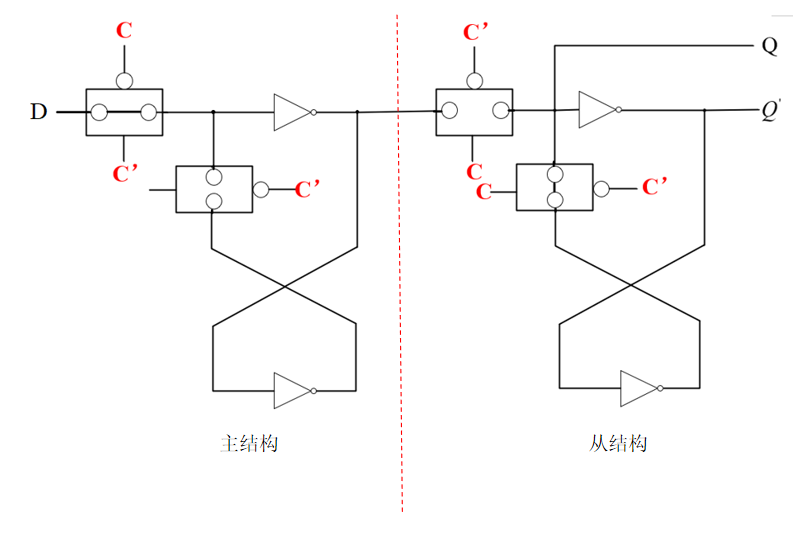

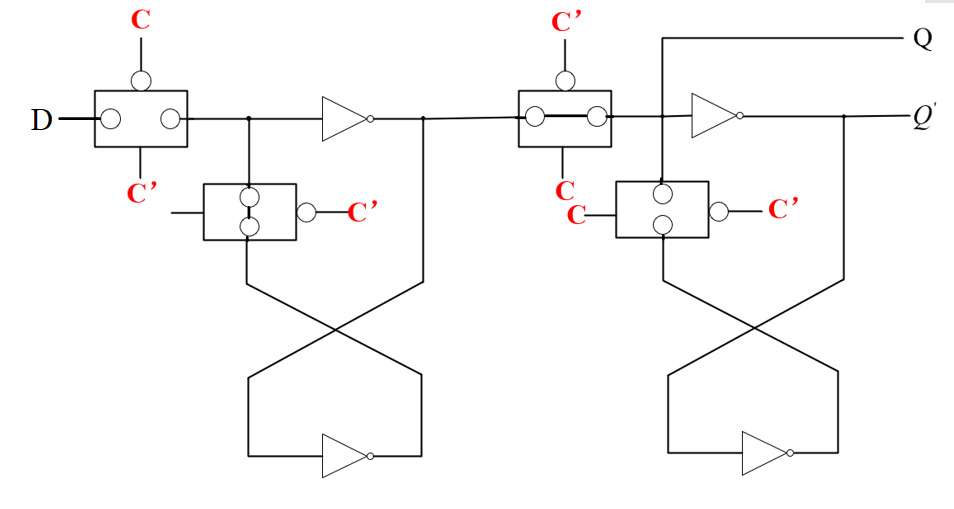

目前常见的边沿触发器产品,主要采用主从结构、维持阻塞结果以及利用门电路传输延迟时间等几种电路结构的边沿触发器,采用CMOS传输门构成主从结构的D触发器如下所示:

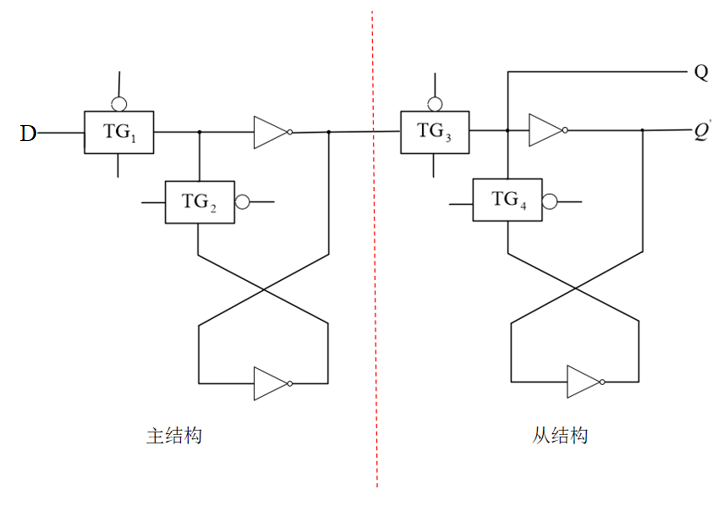

对于是上面的主从结构的D触发器可以分为主结构和从结构,如下图所示:

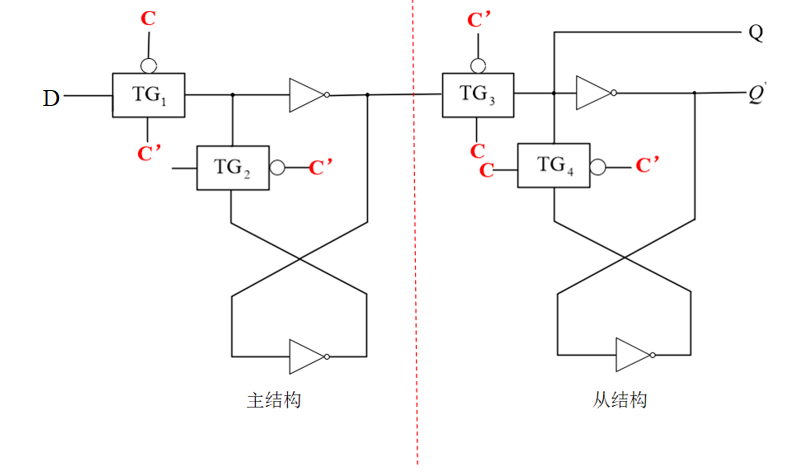

在上面的电路中,传输门的开关状态会受到时钟信号的控制。在主结构中,C分别控制的低电平使能端和

的高电平使能端;在从结构中,C分别控制

的高电平使能端和

的低电平使能端。如下所示:

当CLK=0时,则C=0、C'=1,此时主结构中的导通、

截止,从结构的

截止、

导通,此时电路的模拟开关可以为:

对于主结构来说,这种情况下主结构相当于组合电路,从结构相当于时序电路。

当CLK=1时,则C=1,C'=0,此时主结构中的截止、

导通,从结构的

导通、

截止,此时电路的模拟开关可以分为:

对于主结构来说,这种情况下主结构相当于时序电路,从结构相当于组合电路。

边沿触发器在上升沿到来之前接受数据端的输入信号,但是输出状态不变,在上升态的时候状态发生变化,这是边沿触发器的动作特点。

1.3 边沿触发的D触发器和JK触发器

下面对于各种类型的上升沿触发器进行介绍。

1.3.1 边沿触发的D型触发器

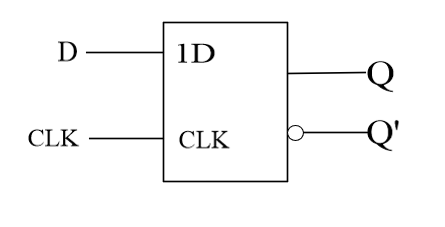

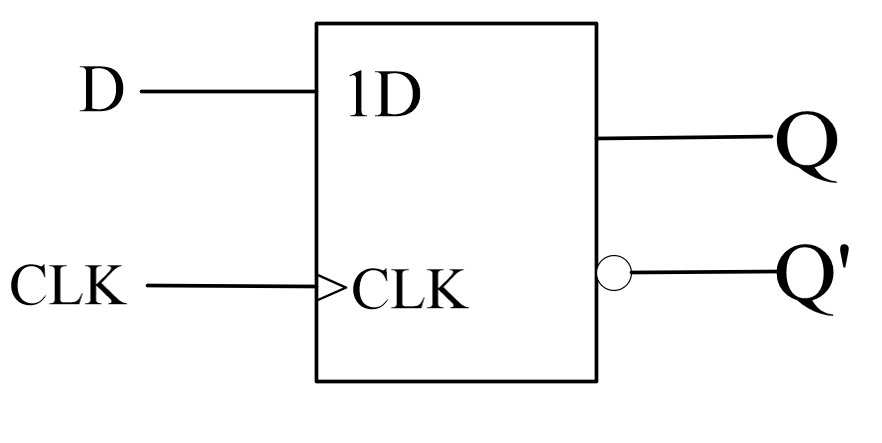

边沿触发的D触发器仅在时钟信号的上升沿或下降沿瞬间采样输入数据(D)并更新输出(Q),确保每个时钟周期只响应一次输入,抗干扰性强,适用于严格的同步时序电路;而电平触发的D触发器(通常称为D锁存器)在时钟信号为高电平或低电平的整个期间持续透明传输输入数据,输出可能随输入波动,抗干扰性较差,多用于异步设计或临时存储。下面列出电平触发的D型触发器和边沿触发的D触发器:

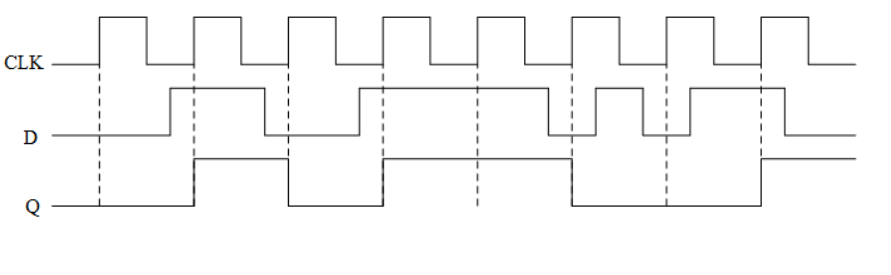

边沿触发D触发器的波形图如下所示:

1.3.2 边沿触发的JK触发器

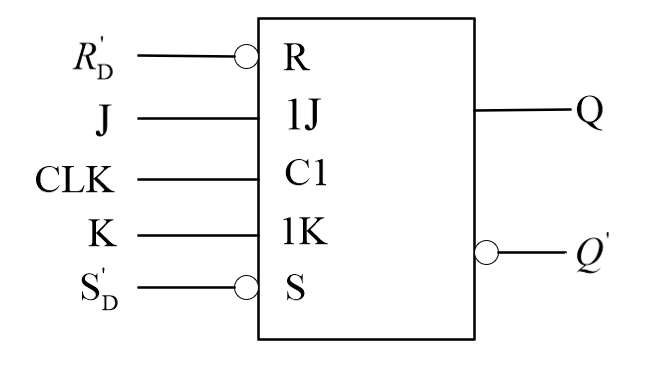

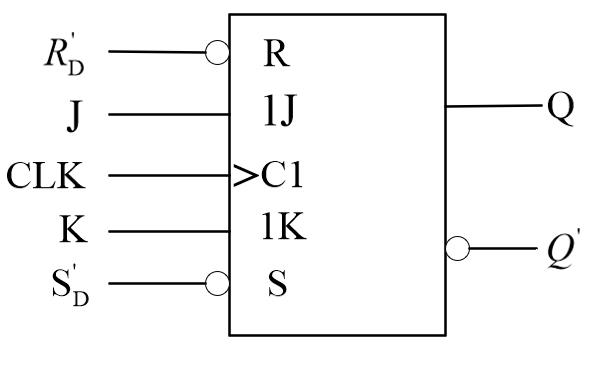

与D触发器类似,边沿触发的JK触发器只在时钟信号的上升沿或下降沿瞬间采样输入(J、K)并更新输出(Q),确保每个时钟周期仅响应一次输入变化,抗干扰能力强,适用于同步时序电路(如计数器、状态机);而电平触发的JK触发器在时钟为高(或低)电平的整个期间持续监测输入,可能导致输出随输入多次变化,抗干扰性差,通常用于异步设计或简单逻辑控制。边沿触发采用主从或负反馈结构确保稳定,而电平触发结构简单但时序约束严格,容易产生竞争冒险。电平触发的JK触发器和边沿触发的JK触发器如下所示:

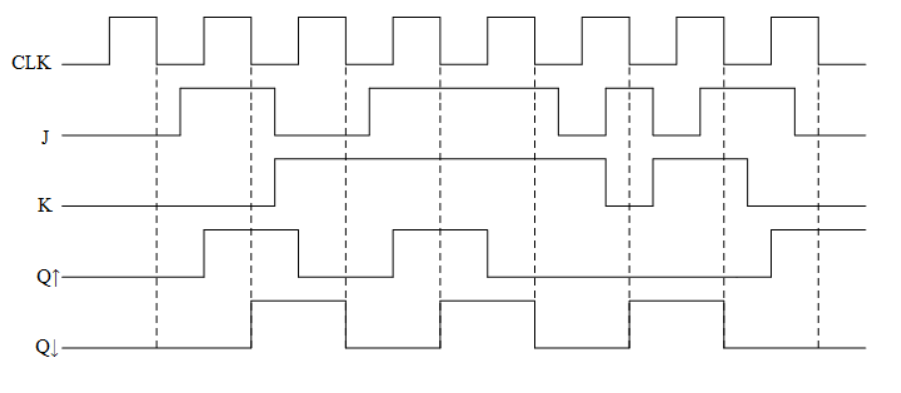

边沿触发的JK触发器的波形图如下所示: