差动讯号(3)弱耦合与强耦合

各位在设计高速差动对时,除了阻抗之外,可能还会被问到一个问题,P与N之间的间距要多少?

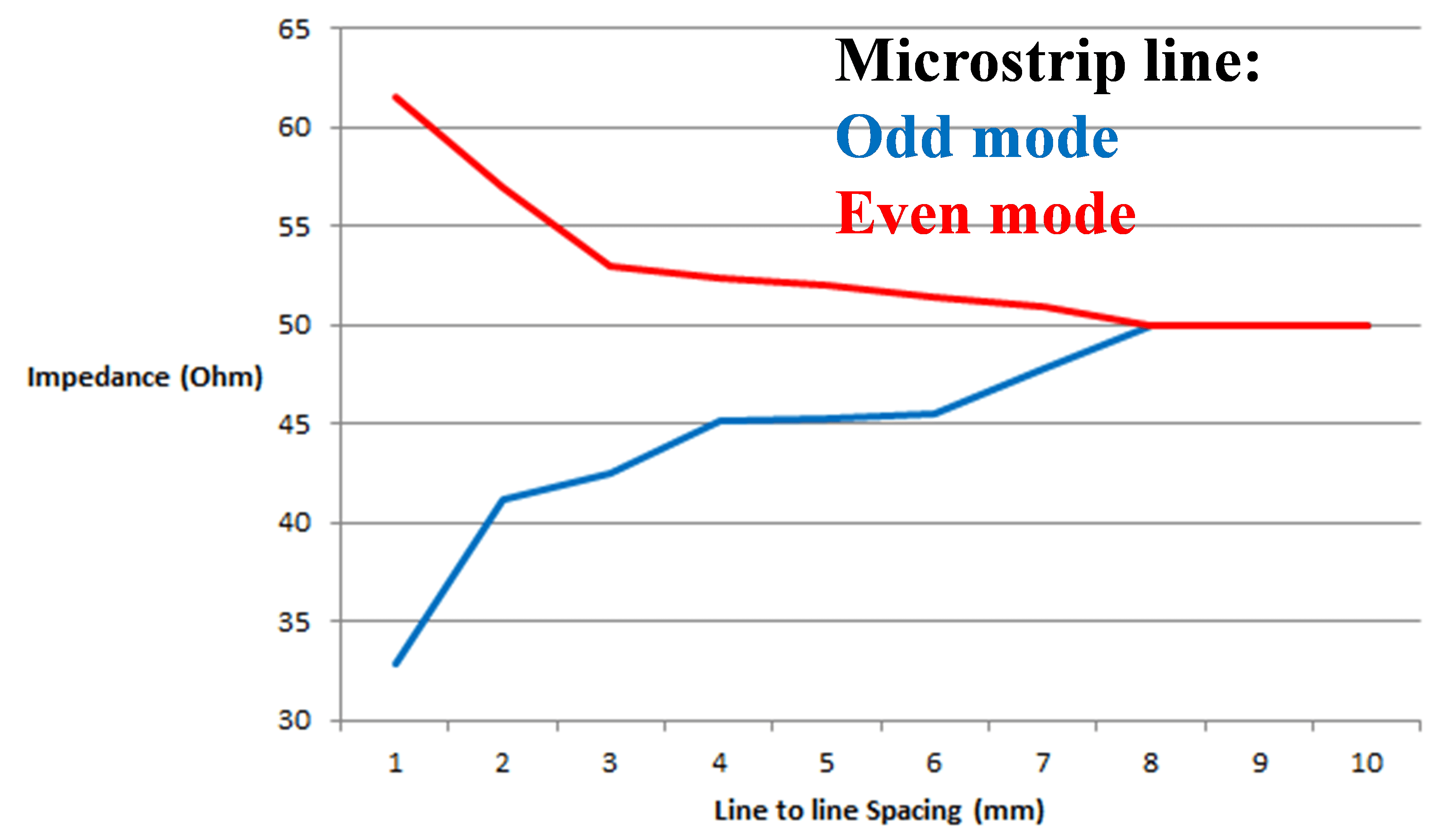

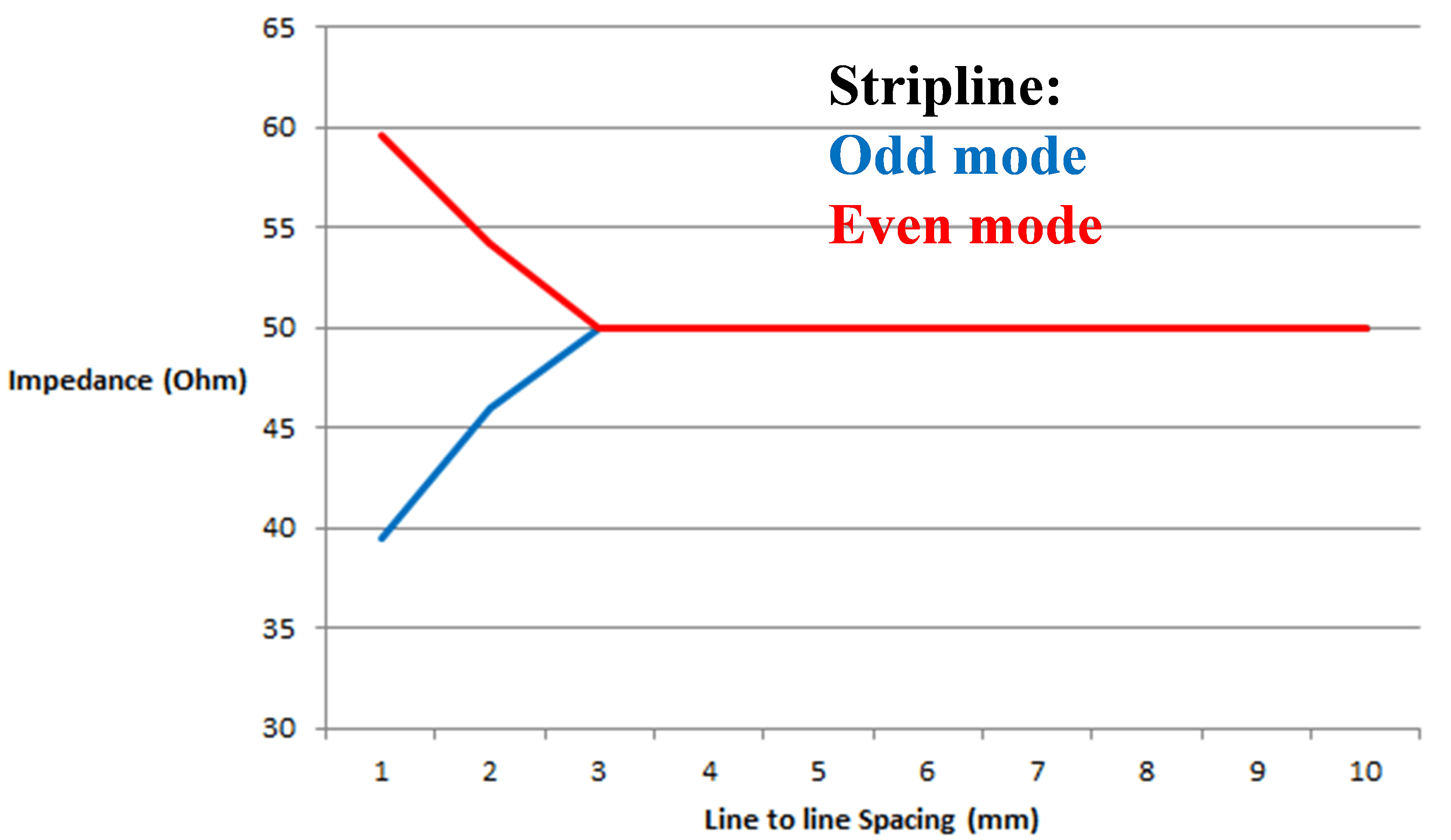

在差动讯号(2):奇模与偶模一文中,我们已经知道差动对两线间距会影响其特性阻抗,且在影响传输线阻抗的几个要素一文中,我们知道传输线阻抗是可以被介质厚度、 介质介电常数DK以及线宽所控制。 因此如在线宽及介质材料、厚度不变的情况下:

1.间距越小,奇模阻抗越小,则差动阻抗越小

2.间距越大,偶模阻抗越大,则差动阻抗越大

所以在阻抗可以被完美控制的前提下,我们来细数强耦合跟弱耦合的优缺点,以方便各位未来设计时的取舍

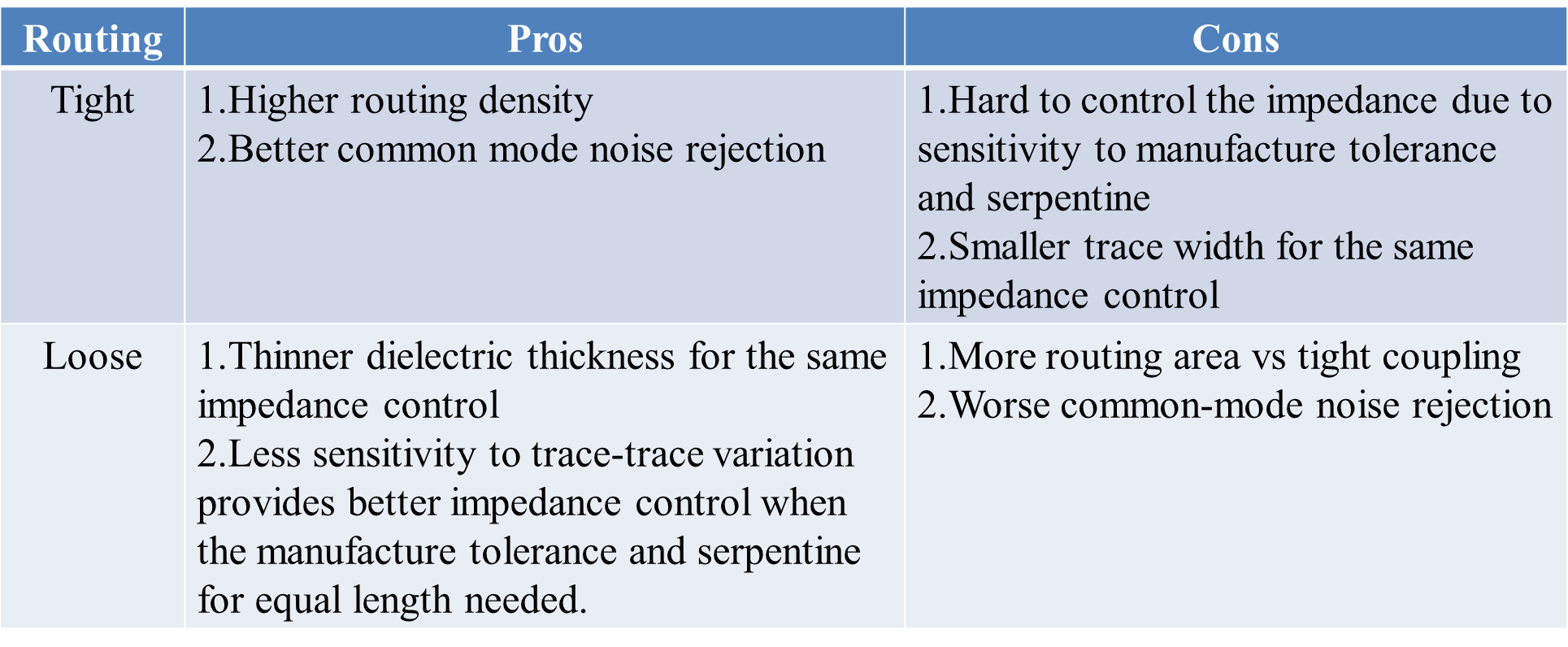

强耦合:

优点:

1.Layout 走线占用面积比较小,意思是板子可以做的精密、高密度

2.因为PN两条线靠得比较近,所以感受到的噪声近乎相等的情况下,差动对的噪声抑制能力会比较好

缺点:

1.相同介质厚度与材料的前提下,为了控制阻抗,线宽会变得比较小,则传输线的高频损耗会比较高,不了解的人可参考PCB中的损耗,你知道几个呢?一文。

2.PCB制程上总会有一些Tolerance,这些未知的变异会使得阻抗有变化,而且在设计上为了满足PN两线等长,往往会把较短的线tune长,这也会使阻抗有变化。 强耦合差动对的阻抗因为对线距变化较为敏感,因此阻抗会较不容易控制。

弱耦合:

优点:

1.可以做到较薄的介质厚度使PCB变薄

2.对制程变异及tune线较为不敏感,阻抗控制较为容易

缺点:

1.需要更多的走线面积,甚至更多走线层

2.比较差的噪声抑制能力

笔者个人是弱耦合的爱好者,除了在有空间限制的区域内(例如BGA封装、连接器),其余走线都是弱耦合为主。

我相信对每个人而言,高速讯号的定义都会不一样,在这边我就列个本身经验。

=>Data rate大于10G,走弱耦合

不过,前提是你需要给传输线有良好的走线环境,需要离power via、power plane、其他高速、低速走线尽量远一点,让耦合噪声相对小!