Cadence 高速系统设计流程及工具使用二

5.3 仿真库的建立和设置

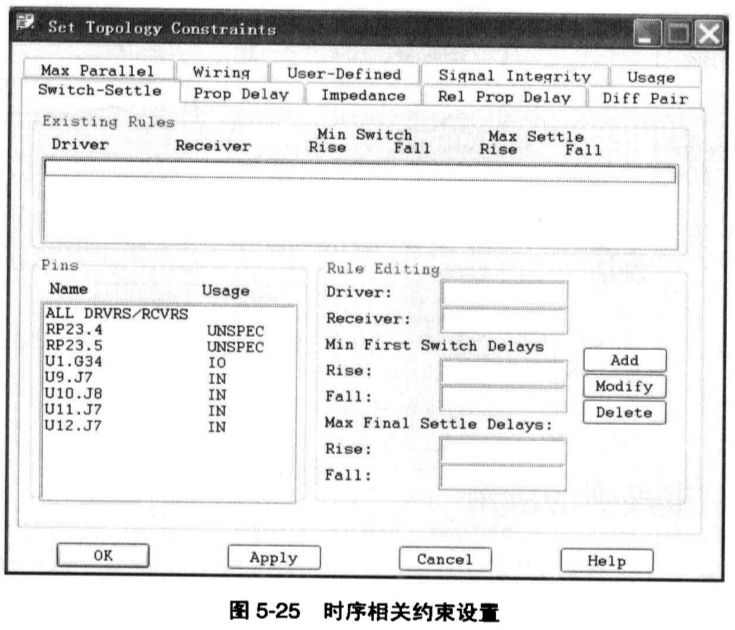

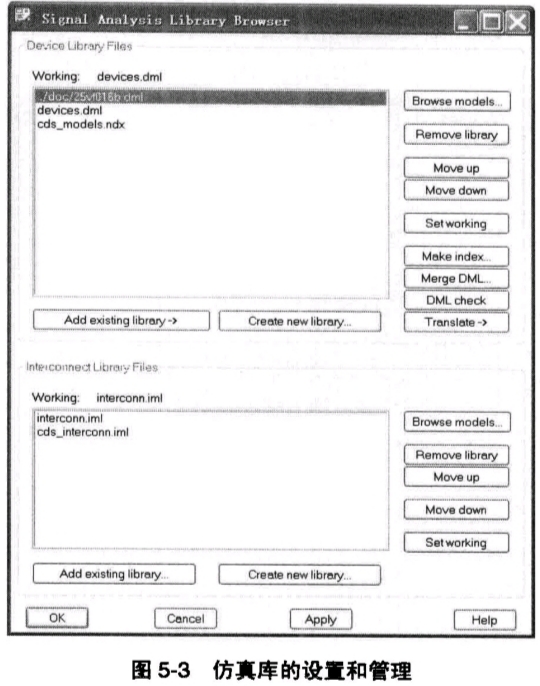

通过上面的步骤,我们得到了一个经过验证的 DML 模型库。为了在我们的设计中能够使用这个模型库,需要把这个模型库加入到设计中。在 PCB SI 的菜单中,选择“Analyze”–SU2EMI Sim–Library”命令,出现模型库管理界面,如图 5-3 所示。在这个界面里,可以添加、删除和编辑模型库,比如选择“Add Existing Library”命令或者“Add Existing Library–Local Library Path”命令,就可以把已经做好的模型库加入到当前的设计中,如图 5-3 所示。这样,就可以在仿真过程中,通过选择位于某个库中的 IO 模型,对信号进行仿真。如果没有在库管理中加入所需的器件模型,那么在仿真过程中,软件会提示找不到要使用的器件模型。

Cadence 提供了多种方式来方便用户使用。在这个界面中,用户可以通过单击“Translate”按钮,然后选择“IBIS2SigNoise”命令,直接将 IBIS 模型转换成 DML 模型,然后再选择“Add Existing Library”命令将刚刚转换成的 DML 模型加入的仿真库中。当然,这里是要保证运行 IBIS2 SigNoise 的过程中没有错误的情况下,才可以在这里直接进行转换。如果出现了警告和错误提示,用户还是需要进入 Model Integrity 环境,对出现的警告和错误加以甄别和修正,然后才可以在仿真中使用。

注意,从本章开始,我们要用很大的篇幅来介绍软件的使用,以及在使用过程中所遇到的各种参数设置。Cadence 高速设计流程中涉及几个工具的使用,每个工具中又有很多功能的使用和参数设置,如果每个参数的设置,作者都把软件的图形界面复制下来,显示在这里,那么估计这本书的厚度会相当客观。可是这样做最直接的后果就是读者花钱买了一堆软件图形界面的使用手册。在本书的开篇作者就声明过,写这本书,不是想冠以“Cadence 高速设计...”为名,然后以大量软件使用手册的翻译说明充斥内容,所以为了不冲淡作者想表达的信息,在本书结合软件使用的部分,尽量减少书中显示的图形界面,对于具有多个界面层次的软件功能,作者尽量只在关键点上显示软件界面。这样做虽然给读者留下了很多未尽之处,但同时也给读者留下一定的空间,让读者自己去发掘和探索软件的功能。我相信,聪明的读者一定会在自己的实践过程中,通过举一反三的能力建立自己对 Cadence 软件的感知和体会,甚至可能还会有意想不到的收获。

5.4 仿真分析条件设置

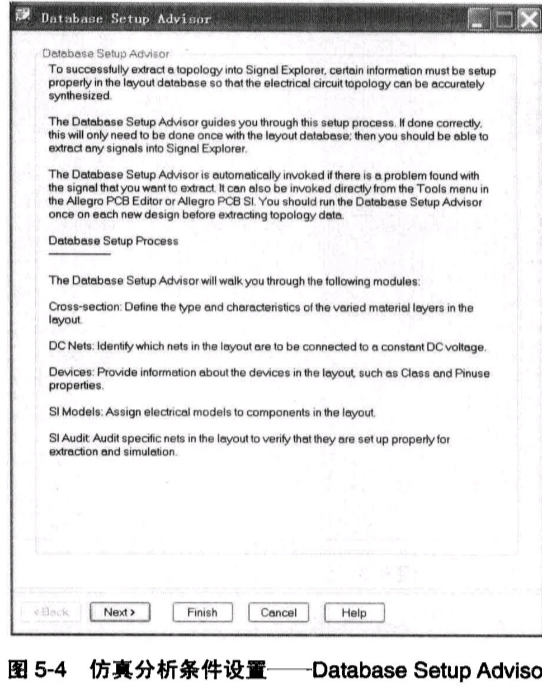

在 5.1 节中,我们已经讨论过了,要进行仿真分析,还需要设置其他的分析条件。Cadence 为了方便用户,按照设置条件的步骤,提供了一个集成的设置环境,

如图 5-4 所示,该集成环境的调用方法是选择“Tools→Database Setup Advisor”命令。

在这个集成环境中,用户可以一步一步按照预订的步骤对仿真条件进行设置。在此界面的中下部,有设置过程的简单介绍,内容如下。

• Cross-section:定义在 Layout 中使用的叠层和材料参数;

• DC Nets:定义直流电压值,也即系统静态工作点;

• Devices:指定器件的类型和 Pinuse 属性;

• SI Models:为器件指定电气模型;

• SI Audit:对前面的设置进行检查以确保能够正常地进行抽取和仿真。

以下几节的内容,我们按照这样的设置流程逐步对仿真库的设置过程进行讲解。

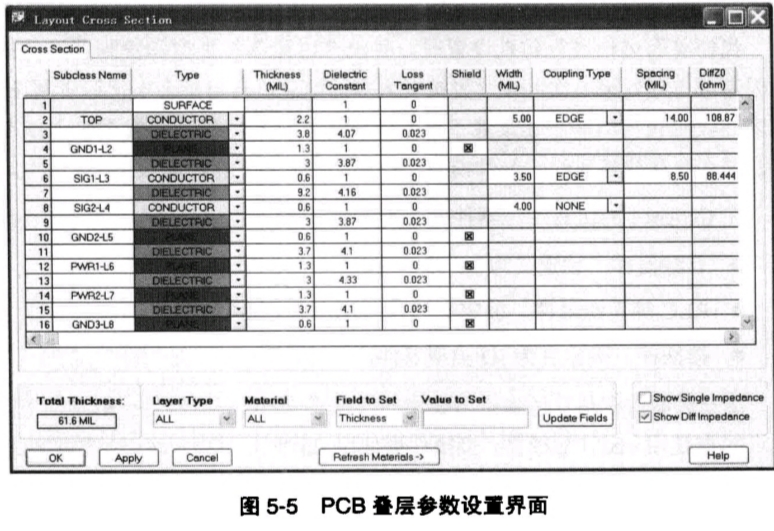

5.4.1 Cross-section—PCB 叠层设置

如图 5-5 所示是 PCB 叠层参数设置界面。在此对话框中,可以添加或删除叠层,也可以更改每一层的类型、材料、厚度、电导率、介电常数、线宽和特征阻抗等参数。这里的参数,不需要详细讲解,相信读者能够根据自己的工作做出正确的设置。只是有一点需要提醒读者的是,在右下的位置,有一个“Show Diff Impedance”复选框,这个复选框被选中,Cross Section 界面显示的内容会发生变化,留给读者自己去比较。如果读者的设计中包含很多差分线网络,那么一般要选中这个复选框。

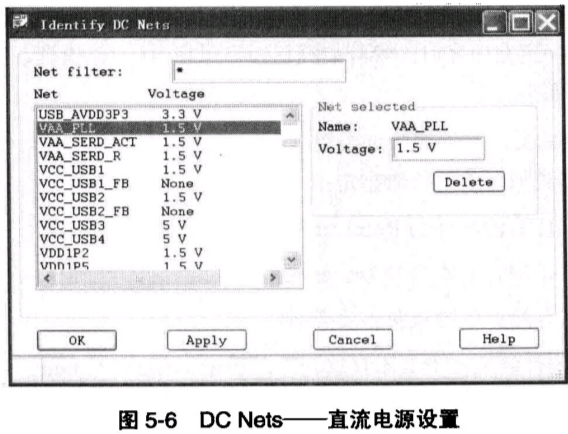

5.4.2 DC Nets—直流电压设置

做完并关闭叠层参数的设计之后,回到“Database Setup Advisor”界面,直接单击“Next”按钮,就可以进入直流电源网络的设置界面,如图 5-6 所示。

此界面的使用应该也不需要详细讲解,很明显,选择左侧列表框中的待选网络,在右侧的文本框中可以指定该网络的直流电压值。有一点需要读者注意的是,并不是所有的电压值我们都需要去做这样的设置。为什么?留给大家一个思考,在第 6 章中,做高速设计总结的时候我们再来揭晓答案。

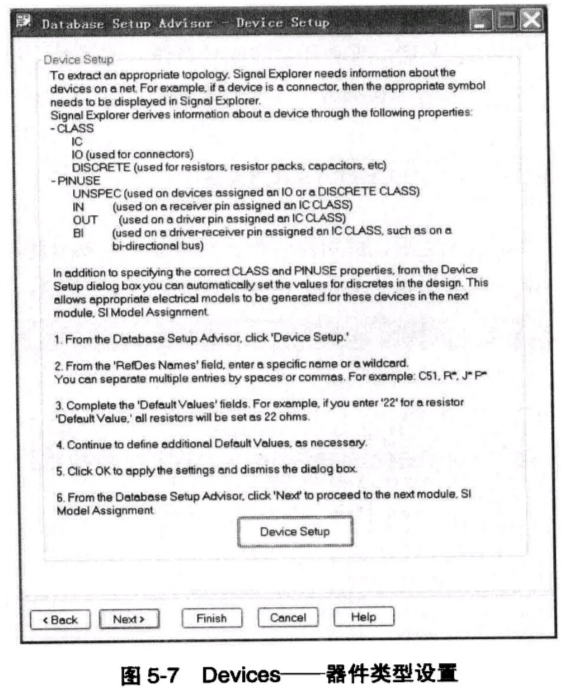

5.4.3 Devices——器件类型和管脚属性设置

我们前面讨论进行仿真设置时,并没有讨论器件类型和管脚属性的指定,这是因为考虑到如果一次性让读者接受太多的信息,有可能会干扰读者阅读的主线。所以,我们先从结构上让读者了解高速设计的流程,然后再慢慢加入细节性的东西,那么现在就是我们对器件模型使用细节进行讨论的时候了。

在 Cadence 的仿真中,器件被分为三类。

• 有源器件,被定义为 IC 类;

• RLC 等无源器件,被定义为 Discrete,也即离散器件;

• 接插件,被定义为 IO 类型器件。

这三类器件在仿真环境中所使用的模型不同:IC 有源器件一般使用 IBIS 模型,RLC 模型使用 ESPICE 模型,接插件也使用 ESPICE 模型。这三类模型的来源也不相同,有源器件使用的 IBIS 模型,在前面已经讨论过了,它一般来源于器件厂商;而无源器件的 RLC 模型,可以由系统自动生成;虽然 IO 类接插件也使用 ESPICE 模型,但是此类模型一般由用户在参考器件等效电路模型的基础上自己去生成(Create Model)。在进入 Devices 设置之前,Setup Advisor 给了我们一些提示,有必要对这些信息仔细解读,如图 5-7 信息所示。

图中的上半部分就是对器件模型分类及管脚类型的说明。对于器件的分类我们已经清楚了,为了明确各个器件管脚在仿真网络中的作用,还需要对管脚进行分类,以便确定在仿真时,管脚能够正确调用相应的 IO 模型。如图 5-7 所示,管脚基本分为四类。

• UNSPEC,未声明管脚类型,也即 Do-Not-Care 类型,一般用于接插件管脚和离散器件的管脚指定;

• IN,即有源器件的 Receiver 类型;

• OUT,即有源器件的 Driver 类型;

• BI,有源器件的双向驱动类型。

当然,器件的管脚类型不只这几个,还有 Power,Ground 和 NC 等类型。管脚类型的正确设置不仅能够保证模型的使用,还可以进行电气规则检查 ERC,比

如,在原理图设计的时候,如果一个网络中所连接的管脚类型都是 Input 类型(或者全是 Output 类型),那就说明原理图设计上出了问题。所以,在原理图设计阶段就要保证器件及管脚类型的正确指定。

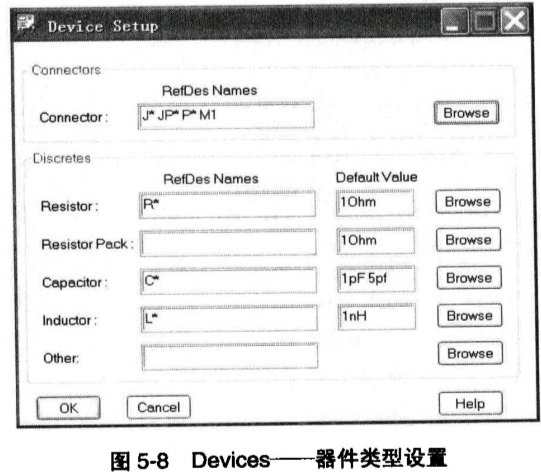

单击如图 5-7 中的“Device Setup”按钮,进入器件类型设置界面,如图 5-8 所示。

在器件类型设置的界面中,用户可以指定以特定字符开始的器件标号属于某一类器件。比如,图中显示的是电阻类型,我们就可以指定所有器件标号以字母“R”开始的都是电阻。我们还可以具体地指定哪个器件属于何种类型,比如在 Connector 类型中的参数设置,“JJPPM!”(注意,在各标识符之间有空格),这个设置的含义是,所有以 J,或 JP,或 P 开始的标号器件为连接器,并且标号为 M!的这个器件,我们也强行指定为接插件。这是一种强行指定方式。

5.4.4 SI Models—为器件指定模型

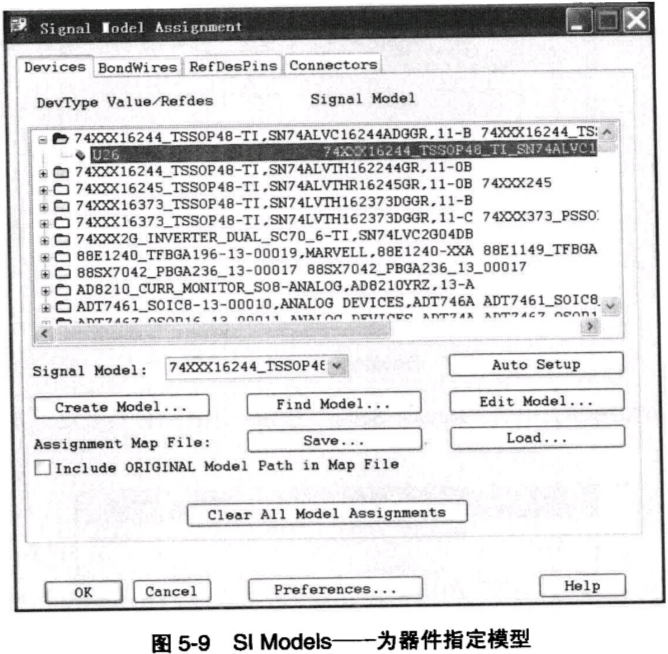

完成器件类型指定之后,就可以依据器件类型,对器件进行 SI 仿真分析使用的模型指定。器件模型指定“Signal Model Assignment”界面,如图 5-9 所示。

在为器件模型指定的这个界面中,当前设计中所使用的器件及其所使用的模型都可以找到,并且可以对某个器件进行模型的指定和编辑。

读者注意到,在模型的指定按钮中有一个“Auto Setup”按钮,使用这个按钮只是对 RLC 等离散器件的 ESPICE 模型进行自动生成,而对于有源器件和接插件是无效的(这句话也不完全对,虽然它不能为器件自动指定器件模型,但是可以根据器件中管脚的类型定义自动指定管脚默认的 IO 模型)。所以需要对仿真中用到的有源器件和接插件进行单独的指定或者编辑生成。

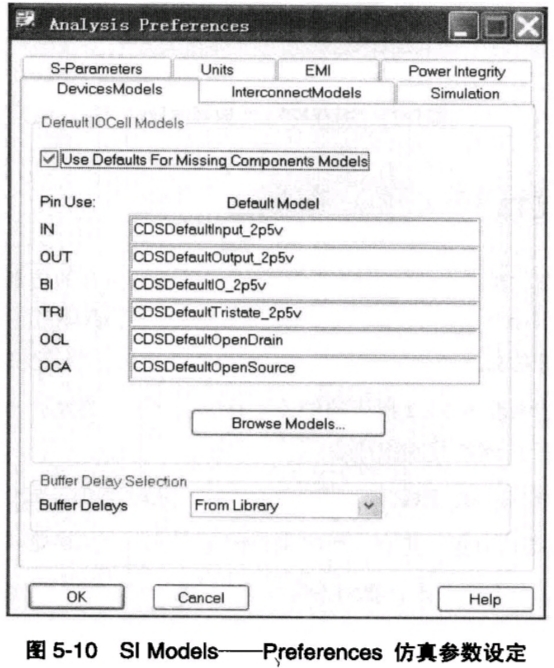

在这个“Signal Model Assignment”界面中,除了完成器件的模型定义之外,它还有一个很重要的功能,那就是仿真参数设定“Preferences...”按钮,单击该按钮可打开如图 5-10 所示内容。这里可以设置的参数包括器件模型参数、仿真模型参数、仿真精度、结果显示和测量单位、EMI 参数和电源完整性参数。其中常用的大致有:仿真的周期数(Measurement cycle)、时钟频率(Clock frequency)、占空比(Duty cycle)、偏移量(Offset)、固定仿真时间(Fixed duration)、波形采样精度(Waveform resolution)、仿真截止频率(Cutoff frequency)、仿真模式(FSM mode)、驱动激励(Drive excitation)、测量模式(Measurement mode),以及互连模型抽取方式等。一般可以使用默认值,各人根据自己的要求进行个别调整。注意,这些参数对于精度要求比较高的仿真而言要仔细设置,否则也会引起仿真结果不可信。作者就亲身经历过由于过孔模型抽取的参数设置不恰当,从而引起了 600MHz 的 DDR2 设计中出现时序问题的情况。

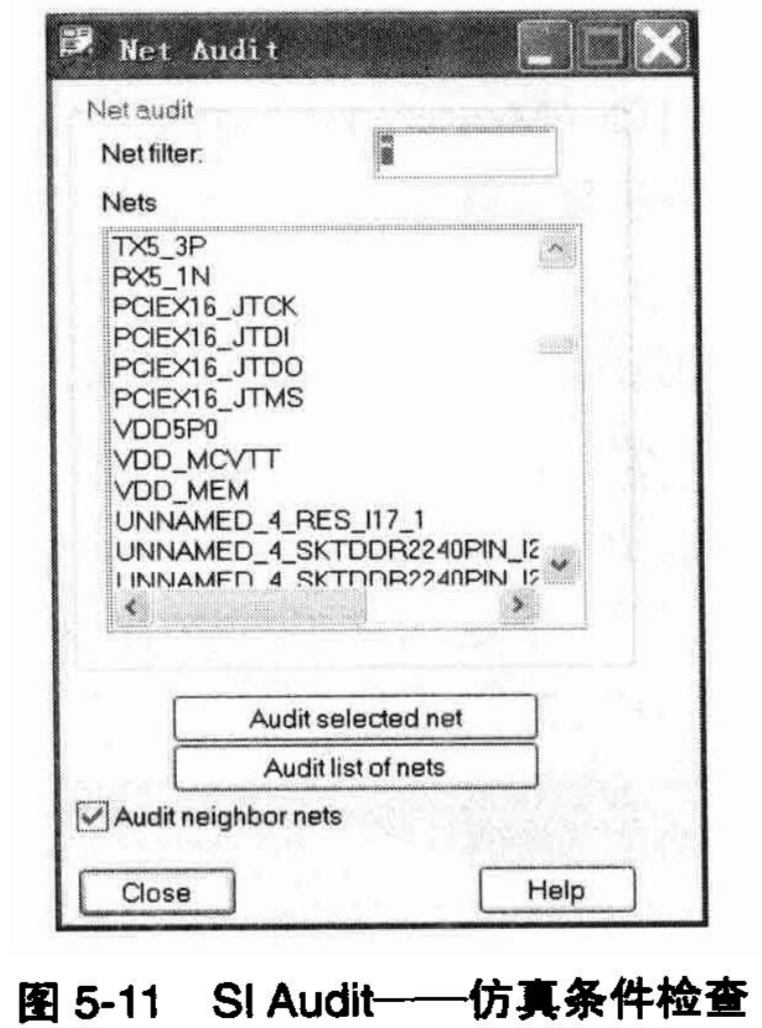

5.4.5 SI Audit—仿真条件的检查

当以上所有的仿真条件及参数设置完成之后,在 Database Setup 的最后一步我们可以用 SI Audit 进行一下验证,以确保我们所关心的网络上所有和仿真相关的因素都已经处理好了,如图 5-11 所示。如果 Audit 的结果有问题,那么用户可以按照结果的提示,找到出错的原因,重复前面的某些步骤,对仿真条件进行修改和完善。如果没有问题,那么恭喜你,我们可以准备进入下一节,准备进入实际的高速信号仿真。

5.5 系统设计和(预)布局

在上一节的结尾,我们做好了 SI Audit,并确认所有的仿真条件设置都已经正确的情况下,为什么还要说可以“准备”进入信号仿真环节了呢?这是因为在进行真正的信号仿真并获得约束之前,我们还需要考虑一些其他的约束条件。

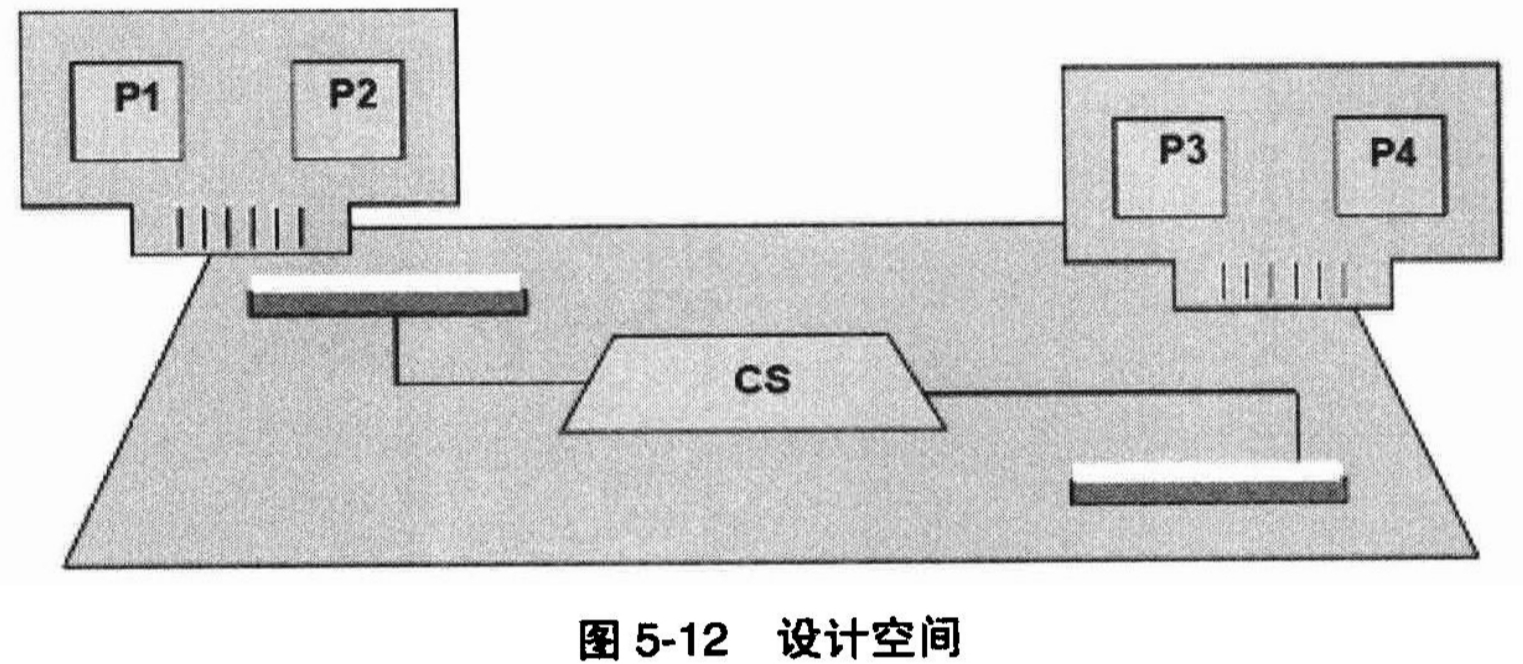

首先我们来看图 5-12 所示的例子。假如我们现在要设计一个信号处理系统,整个系统由三个 PCB 模块组成。

• 两个信号处理子板,分别带有两块信号处理器 P1,P2 和 P3,P4;

• 一个通信背板,带有一个中央处理器(或称为交换处理器)。

在这样的一个系统中,我们不仅要求位于同一个 PCB 板上的两个处理器,也即 P1 和 P2 之间,P3 和 P4 之间进行数据交换,还要求两个子板之间进行高速数据交换,那么对于信号仿真及约束的定义,就不能仅限于同一个 PCB 板之内,还要求能够进行整个系统的仿真。对于这样系统级别的仿真,在高速设计流程中,通常有两种做法。

• 通过 Cadence 提供的多板联合仿真功能,我们可以对多个板级进行“拼接”,使得对于我们感兴趣的信号,通过这种“拼接”方式贯穿于整个系统,这样就可以对这个信号进行全路径的系统级仿真。

另一种做法是,由系统架构师对这样的系统设计做个预先的估计(这种估计可能是基于丰富的设计经验,也可能基于严格的信号仿真,但最好做个合理的估计),然后分配给每个子板一个设计预算,只要每个子板的设计不超过这个预算,那么这个系统在集成的时候就不会出问题。比如,如图 5-12 中的系统,假如对于从 P1 到 P4 的信号传输延迟要求在 5ns 之内,那么系统架构师可能会给出如下的预算:P1 到接插件延迟 1ns,P4 到接插件延迟 1ns,背板上的两个接插件之间延迟 2ns,那么拿到设计任务的三个工程师就要按照这个要求去实施,只要不违反预算中的分配规则,系统整合的时候就应该足够安全。

这两种做法都有各自的利弊。第一种做法看起来很严谨、准确,但是缺点是可行性不强。因为无论哪个公司,涉及这样规模的系统设计,通常不是一个工程师,基本上是几个工程师协同工作。但是出于信息安全和系统设计管理的角度,不太可能一个工程师能够拿到所有的设计信息,所以这个方法实施起来有一定的限制。而第二种方法,由于有系统架构师的设计预算分配,使得每个子板的设计工程师能够很快启动自己的工作,并且每个工程师所关心的设计范围有限,这样可以使其更加集中精力做好自己的事情。虽然在预算阶段,看起来加入了系统架构师的一些主观因素在里面,但是系统架构师的估计也就在了他能够在早期凭借自己的丰富经验,对系统预期(包括成本、进度等其他因素)有个合理的估计,没有了这些“主观”的预见性,系统架构师的价值也体现不出来。

所以说,系统预算或者一些设计约束,在我们启动每个子板的设计之前就已经并且是一定会存在。我们在接下来的文章里面,再加入一些新的约束的时候,对这些规则的约束一定要执行,而不能随意推翻或者违反这些预先设置好的约束。除非你的仿真过程中,有足够的数据和理由来证明,这些预先的预算规则存在严重错误。

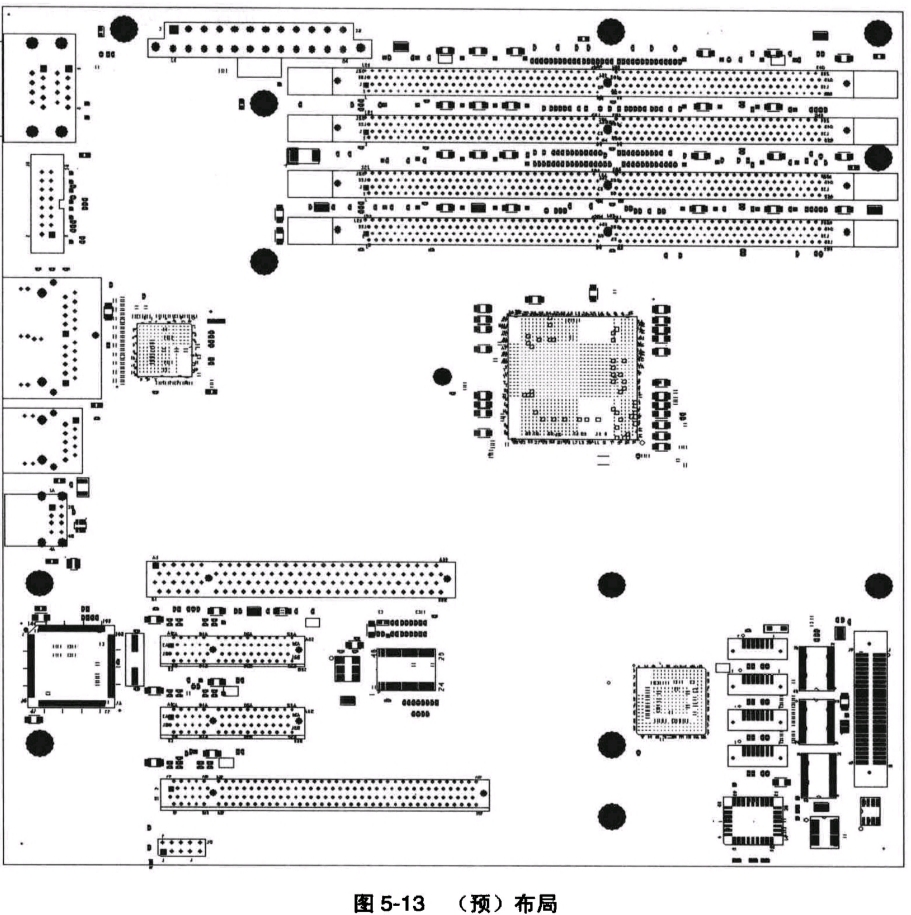

刚才讲的例子是从系统和子系统的观点来看待设计中存在的一些“预先”的约束条件。我们再来看下面的例子,在一个 PCB 板中,会有哪些预先的约束条件存在。为了大家能够更好的理解,我们用一个计算机的主板框架作为例子,如图 5-13 所示。

我们知道,在读到计算机系统时,一定不会缺少以下内容:CPU、大容量 Memory 插槽、几个 PCI 和 PCI-E 子板插槽、硬盘和 CD 排线插槽、各种外设连接接口、RS232、键盘、鼠标、网口和显示器接口等。这些器件(或接插件)的位置一定要按照工业标准进行设计,不能随意摆放。既然这些器件的位置有了具体的要求,那么隐含着连接各类器件之间信号线的电气规则也就受到了限制。这就是(预)布局的概念。

因此,在我们拿到一个设计任务,开始自己动手做仿真并设置约束之前,一定要对这些已经存在的要求有所了解,当然不仅是要了解,最好要理解。因为这些预先设定的布局布线规则,在我们做设计的过程中是具有最高优先级的。在迫不得已一定要违反(打破)这些预设的规则之前,必须清楚地知道为什么要这样做,以及这样做的后果。

题外话,虽然看起来做个计算机的主板,受到的限制和规则很多,但是这也正说明“做”计算机的主板并不难。这里的“做”是指单纯的 Layout。事实上,上面列举的仅仅是做计算机主板众多规则中的一小部分,还有很多机械物理规则(比如主板的大小形状、安装孔的位置大小)和热设计规则(散热器的安装位置、导流通道的高度限制)等。按照这些已经定义好的规则来做一个设计不难,难的是设计和定义这些规则的工作。

好,现在我们既做好了仿真分析的准备,也明确了在系统设计之前已经存在的一些预先设计规则和约束,而且这些规则是必须要遵守的。接下来,我们就可以在这个基础上开始我们自己的仿真分析和规则定义了。

5.6 使用 SigXP 进行仿真分析

SigXP 是 Cadence 设计系统中进行信号仿真分析的工具,它不仅能够和 PCB 设计、Constraint Manager 等工具结合使用,也能够作为一个单独的仿真分析工具使用。在这里,为了说明 Cadence 高速设计流程的理念,我们着重介绍如何在设计流程中使用 SigXP。但这并不妨碍读者脱离设计流程,用 SigXP 提供的强大功能有针对性地做一些专门的仿真研究工作。

5.6.1 拓扑结构抽取

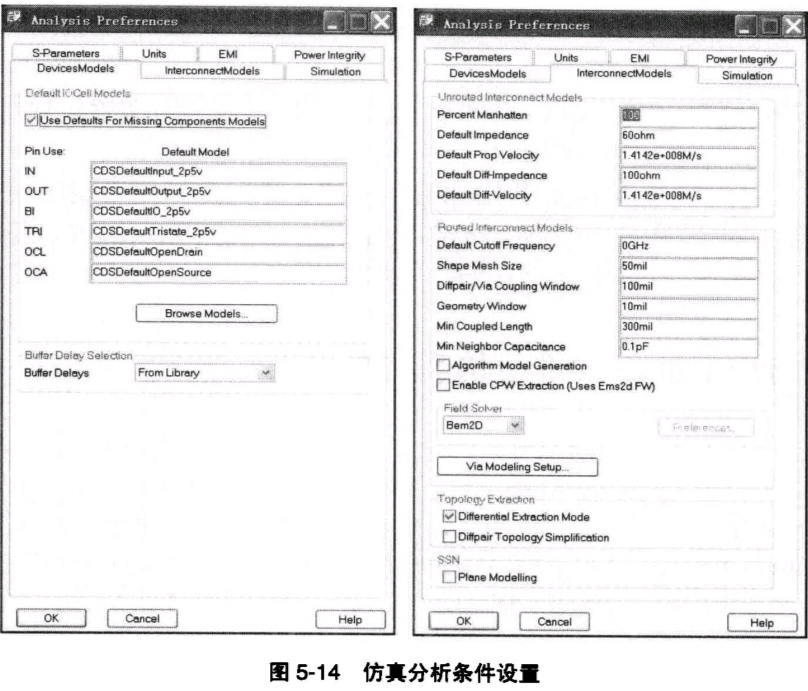

为了让 SigXP 能够获得 PCB 设计环境中的网络信息,在对拓扑结构抽取之前,还需要设置抽取参数(没办法,Cadence 就是这样,很严谨,因此也就很烦琐,熟悉它的流程结构后就能体会它的好处)。在菜单中选择“Analyze”→“Preferences...”命令,对抽取和仿真参数进行设置。这时将弹出如图 5-14 所示的仿真分析参数设置对话框“Analysis Preferences”。图 5-14 中左图是默认的器件模型的设置,如果想改变这些默认设置,用户可以通过单击“Browse Models”按钮,选择所需要的 Buffer Model 类型;右图是对互连参数的默认设置,分为布线前和布线后两种抽取参数,这个应该很容易理解,因为布线前和布线后最大的区别就是在网络中加入了实际的物理信息,比如,传输线的长度、阻抗、速度及过孔数量等。

这里需要提醒读者的是,随着系统时钟越来越快,造成信号的时序要求越来越严,Timing Margin 越来越小,这样就造成在信号仿真时,布线前的真和线后仿真的差别也越来越大,这些差别主要来自于布线前后的物理参数变化。而在Cadence 中,对同一个物理模型的抽取有不同的方法,这就要求读者要充分理解模型参数的含义和抽取方法,这样才能保证仿真结果更加接近真实情况。在本书的实例介绍中,还会谈到由于模型抽取的方法和参数设置的不同,对系统设计造成的影响。

有几种方式可以启动 SigXP 做仿真分析。你可以从 Windows 的 Programs 中,按照软件的层次,找到位于“Cadence SPB”下的 SigXP 程序,直接启动它。也可以直接在 PCB 的设计环境中,通过“Analyze”→SI/EMI Sim→Probe”命令直接对线网进行拓扑结构抽取,进入 SigXP 中进行仿真分析。但是我们一直在强调高速设计流程的概念,所以我们要在设计的流程中启动 SigXP,体会在高速设计流程中 SigXP 所起到的作用,以及它如何与流程中的工具有机地结合,进行数据共享,解决我们高速设计中的问题。

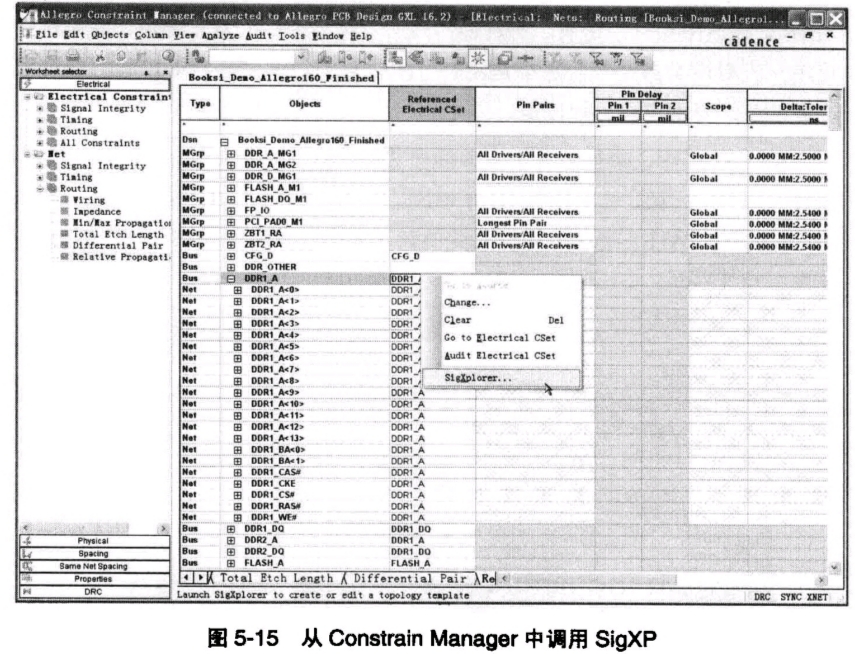

我们在前面已经完成了对仿真条件数据库的设置,下一步我们要通过仿真分析得到关于布线网络的设计约束。因此,我们先打开 Constraint Manager,然后在其中启动 SigXP,对关键布线网络进行分析。如图 5-15 所示,假如我们现在关心的网络是 DDR2_A 这个网络(实际上,图示中的 DDR_A 是个网络名,不是一个单独的网络,在实际设计中,我们通常会把功能相同的网络合并成网络组,这样对整个网络组的分析和约束自然地就实施到属于该组中的每个实际的网络,关于这部分的详细内容,我们在后面再详细介绍),可以通过在这个网络上单击鼠标右键的方式直接启动 SigXP,这时 SigXP 就会把这个网络中所有的信息抽取出来,包括我们前面已经设置过的相关器件的模型参数,进入 SigXP 的环境中进行分析。

5.6.2 在 SigXP 中进行仿真

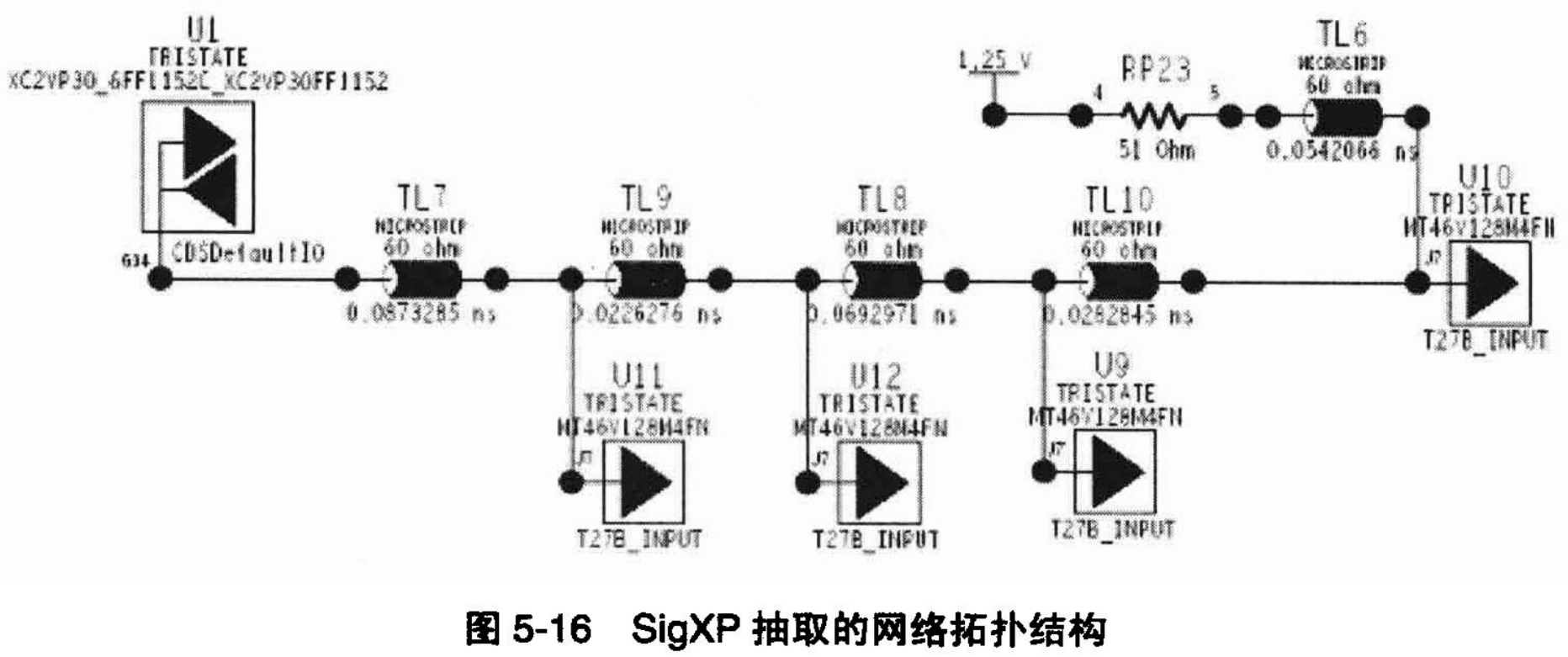

如果我们以前在 Database Setup Advisor 中所做的设置没有问题的话,那么通过对网络的抽取,现在就能够看到 SigXP 的工作界面了,如图 5-16 所示是 SigXP 抽取的网络拓扑结构。

5.6.2.1 设置激励和仿真类型

读者可以看到,SigXP 抽取的网络拓扑结构中的各个元素及连接关系和原理图中的设计是一致的,而各个器件的模型及电压值等参数都是在 PCB 的 Database Setup Advisor 环境中加以指定的。对这样的网络要进行分析,首先要设定激励模式。如果用户没有设定激励源,那么是没有办法仿真的,软件会自动提醒用户该网络缺少激励源,要求用户进行设定。

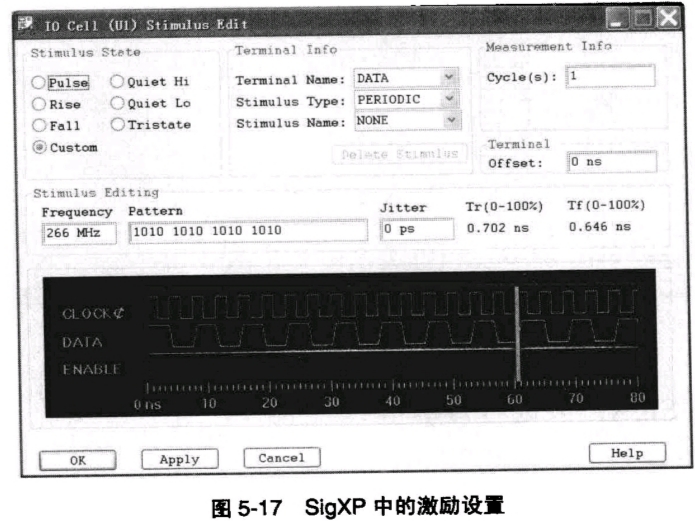

在 SigXP 中,要修改各个元素的参数很简单,只需要用鼠标单击图中各元素的参数即可,比如,修改器件 UI 的激励,在 UI 下面的“TRISTATE”上单击一下即可,“TRISTATE”是 UI 器件当前的默认状态。单击“TRISTATE”之后,会出现激励设置界面,如图 5-17 所示。

在该界面中,SigXP 提供了多种激励模式,读者可根据自己的需要对激励进行设置。一般 Custom 是使用最多的模式,选定 Custom 激励模式后,“Terminal Info”和“Stimulus Editing”两个区域的设置组合为用户提供了丰富的激励码型。当将 Terminal Name 设置为“Data”的时候,Stimulus Type 有三种类型可选,同时 Stimulus Editing 也会相应地配合 Stimulus Type 的激励类型变化而发生变化,这三种类型分别介绍如下。

• Periodic,周期性码型,即数据随时钟周期,在每个时钟的上升沿发生变化。选择该类型后,用户可以在“Stimulus Editing”区域中输入频率和数据。读者可参考图 5-17 对该码型进行理解。

• Async,异步码型,即数据和时钟没有必然联系,选择该类型后,用户可以在“Stimulus Editing”区域中直接输入实时数据电平和状态转换时间,则数据就在用户指定的时间点上发生状态转换,这个状态转换时间点和时钟没有关系。

• Sync,同步码型,即数据的变化和时钟同步,选择该类型后,用户可以在“Stimulus Editing”区域中直接输入时钟周期,状态转换时机(是在时钟的上升沿,或是下降沿)和数据变化模式,数据随着时钟周期,按照指定的转换时机发生变化。数据也可以由系统自动生成最大长度为 1024 位的随机码流。

在实际仿真中,用户可以根据仿真网络的实际功能需求生成定制的激励模式和激励码型。

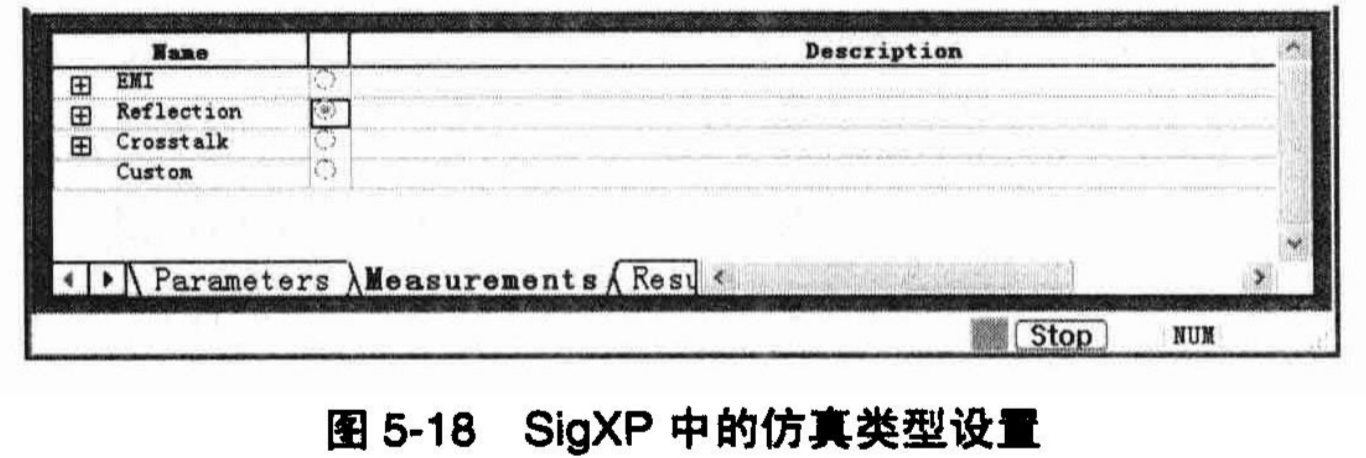

设置仿真激励后,还需要选择仿真类型,仿真类型的选择位于 SigXP 界面下部的“Measurements”选项卡中,如图 5-18 所示。SigXP 提供了四种仿真类型(实际上是三种),EMI,Reflection,Crosstalk 和 Custom 类型。其中大部分信号完整性问题都可以通过对关键信号的 Reflection 仿真得到解决,这是用得最多的仿真方式。如果想对串扰进行分析,就需要选择 Crosstalk 类型,但此时,仿真网络中必须具有两个或两个以上的网络,而且也必须适用耦合传输线模型,才可以进行 Crosstalk 仿真。在本书中只对 Reflection 类型进行讲解和实例分析,其他的几种仿真类型的使用及 Reflection 仿真中众多测量参数的设置,读者可以自己去尝试。

Custom 类型是 SigXP 为了方便用户对仿真结果的多种需求,而扩充的用户自定义仿真类型。在 Custom 类型中所使用的数据来源都是从上面三种仿真结果中直接得来的(因此说实际上只有三种仿真类型)。用户根据自己的需求,可以通过各种表达式组合方式,从上述三种仿真类型中获得数据灵活的组合,从而达到自己的仿真测量要求。这里,我们只介绍一下 Custom 这种仿真类型的存在和意义,对其具体的使用,我们将在第 6 章中以 DDR3 测量的实际例子做详细介绍。

5.6.2.2 设置仿真参数

按照设置激励源的方法,同样,如果需要对传输线模型参数或者网络中一些例如电阻、电容元件,或者传输线的参数进行调整,可以单击此元件的第一行文字,即元件名,这时 SigXP 的电子表格会自动跳到“Parameters”选项卡,并展开此元件的所有参数,然后根据需要在电子表格中更改参数值。如果元件的某个参数栏带有下拉按钮的标记,那么表示该参数可以进行多值输入,也就是我们常说的多值扫描分析。例如,我们单击了某个电阻的“Resistance”参数栏的下拉按钮,那么会弹出如图 5-19 所示的参数设置界面。

在这个参数设计界面中,有四个部分,分别对应四种不同的参数设定方式。

• Single Value,单值输入,也即设定该电阻的阻值为某一特定值,例如 560Ω。

• Linear Range,多值输入,指定线性变化范围。比如设定该电阻仿真扫描时起始值 500Ω,终值 700Ω,以步长 100 进行三次参数扫描仿真。

• Multiple Values,多值输入,指定固定扫描值。比如,设定该电阻仿真扫描时也是进行三次参数扫描仿真,但是这三次变化的值是指定的,如 500Ω、560Ω 和 590Ω,这三个值没有办法通过 Linear Range 来指定。

• Expression,表达式关联。比如,在一个仿真中,用户希望所有的电阻都按照同样的变化方式进行参数扫描,那么用户可以指定某一个电阻,例如,R1 的阻值按照一定的方式变化,然后对其余的电阻 R2、R3...指定它们的变化方式等于 R1 的变化方式,这时就可以在“Variables”列表框中选择“R1.Resistance”选项。

这种参数指定的方法适用于对网络中所有元素的参数进行指定,包括对传输线的各种参数进行扫描设置,更多的功能还需要读者自己在实践中尝试体会。

参数设置完毕后,就可以通过选择“Analyze→Simulate”命令或快捷按钮执行仿真了。

5.6.2.3 查看仿真结果

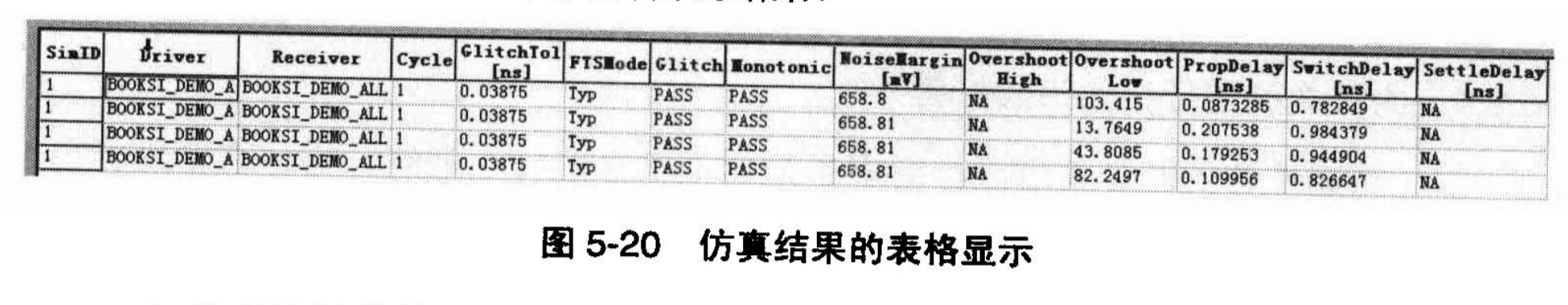

仿真的结果有两种方式提供给用户,一种是在 SigXP 的正下方,在 Result Tab 中以数据表格的方式显示,如图 5-20 所示,用户可以对众多测量结果中的某一项进行排序,从而很快地找到所需的结果。

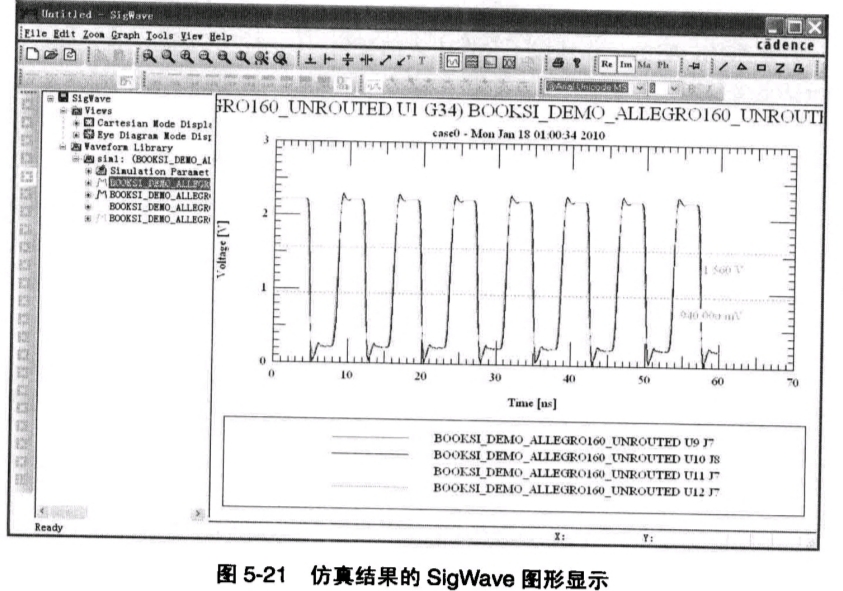

仿真结果的另外一种显示方式,就是在专用图形工具 SigWave 中以图形方式显示,如图 5-21 所示。SigWave 是个非常有用的工具,它不仅可以通过多种方式显示仿真结果,比如 FFT 频域分析、Eye Diagram 眼图,还可以在图形上进行各种标注测量,以方便用户进行数据提取。并且,它还可以和多种测量仪器的数据格式兼容,支持多种格式的数据导入和导出功能,以方便用户将仿真数据和实际测量的波形加以对比。更多的功能还需要读者自己花些时间,通过自己的尝试,掌握工具的使用方法之后,将众多功能融入到自己的工作中。

需要用户注意的是,仿真结束之后,SigXP 的电子表格界面会自动跳到“Results”选项卡并显示仿真结果,如果当前仿真是在没有执行参数扫描仿真的情况下(即所有参数都是某一个固定值)进行的,仿真结果后,SigXP 会自动调入 SigWave 显示仿真结果的波形。如果当期仿真是参数扫描仿真(即在多种可能参数设置下进行的仿真),SigXP 不会自动启动 SigWave 工具,需要用户自己选择某个仿真结果来作为启动 SigWave 的输入条件。所以,当遇到没有图形输出的时候,用户要首先查看“Results”选项卡中是否有多个扫描仿真结果出现。如果在其中,有多组仿真结果,那么用户可以指定其中一组或者几组感兴趣的结果,通过单击鼠标右键,在 SigWave 中进行图形显示。

5.6.2.4 为什么要进行参数扫描仿真

高速设计的初学者可能会对多参数扫描仿真感到不理解,为什么要进行多参数扫描仿真?

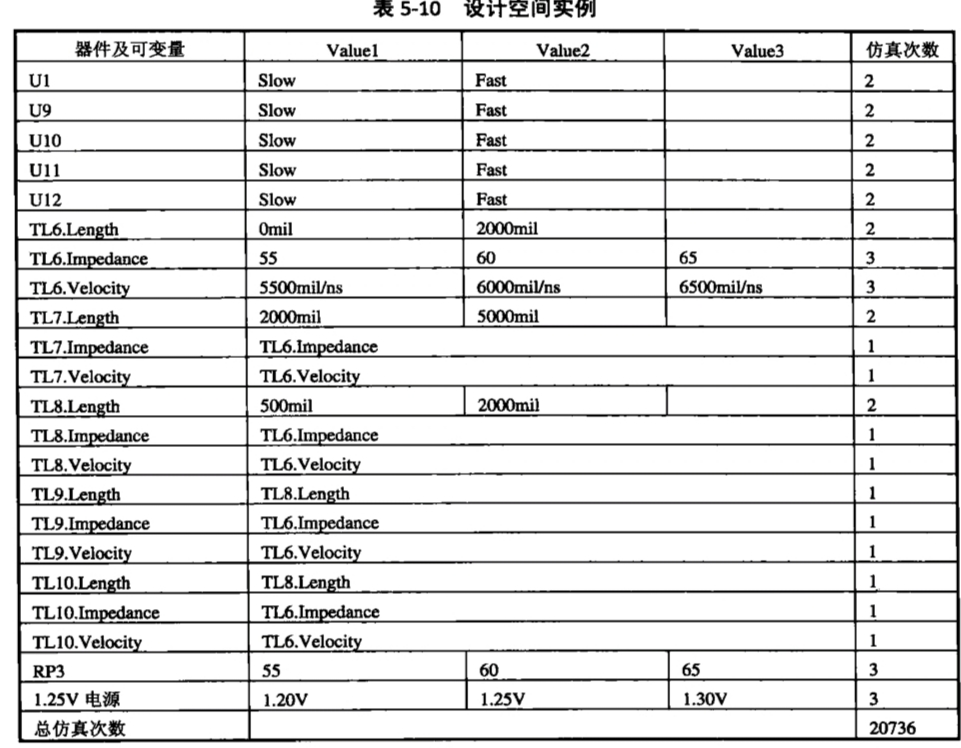

我们知道,前仿真的目的是要在布线之前给出设计中所有可能的设计方案(也称为可行性设计空间,Solution Space)。比如说,一个器件它可能用在机载设备中(如雷达信号处理系统),那么机载设备在低空和高空飞行时,仪器所在的运行环境温度和压力是变化的,低空时环境温度可能是 0℃或者 0℃以上,高空时可能是零下 20℃,这样器件的工作状态是不一样的,对应于器件模型中,就可能是 PVT 的参数变化。我们做仿真就是需要考虑这种工作环境的变化对系统的影响,具体一点说,就是每个信号在不同的工作条件下的完整性。如果读者不从事机载设备的研制,这个例子还不好理解的话,那么再举一个更加实际的例子,即使你设计一个系统,它的工作环境不会发生大的变化,比如机房中适用的计算机,那么也请思考这样一件事情,当我们做传输线阻抗的设计时,我们通常希望 PCB 板上每条传输线阻抗是一致的,比如 560Ω。但是,大家都知道,就目前的工艺而言,PCB 上的金属都是靠腐蚀出来的,而 PCB 上在配置腐蚀药液的时候,其浓度是有波动的,腐蚀的控制时间也不是绝对稳定不变的,所有这些变动的因素就会造成一个 PCB 上不同区域的传输线阻抗会不是“完美”连续的,同样不同批次生产的 PCB 也不是绝对相同的,一般 PCB 的生产厂商都会在生产之前提示客户“我们的阻抗控制能力为±10%”。如果这两个例子还不够说明问题,那么还有一个更加简单明了的例子,想一想我们能够采购到的电阻,比如说 560,在这个器件的包装上一定会标注“560,10%”,这下明白了么?那么以我们抽取的图 5-16 中的网络为例,可能的设计空间如表 5-10 所示。

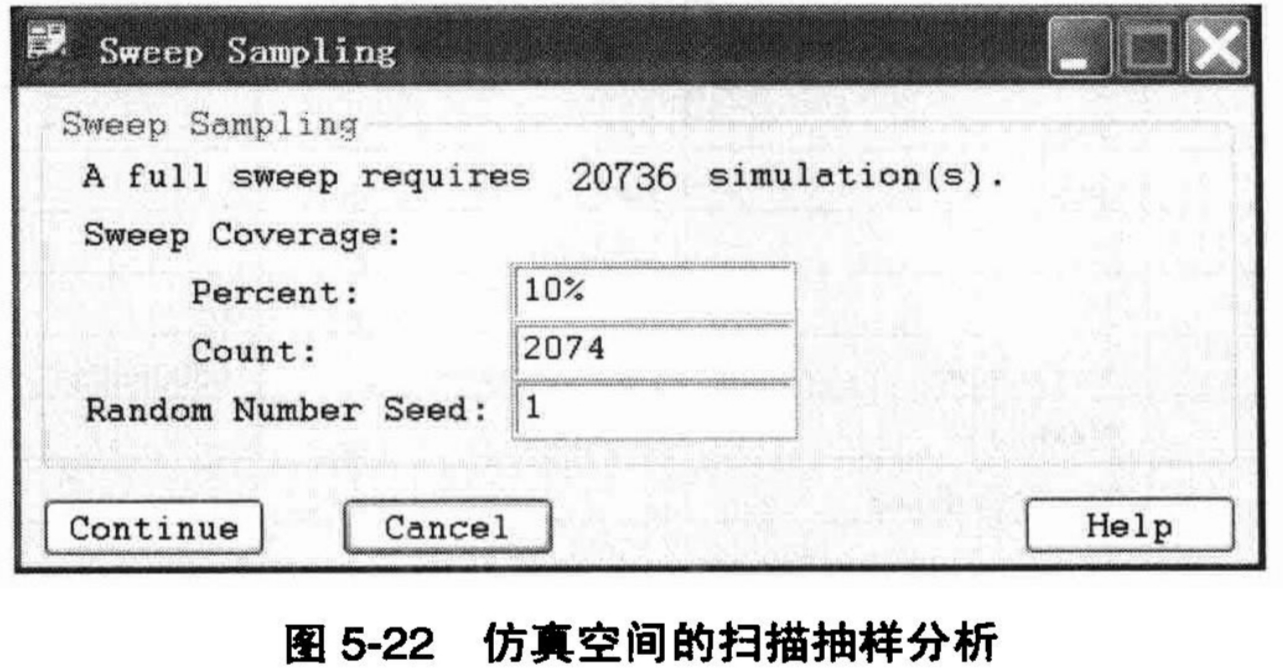

从这个表格中,读者可以看到,要做完所有可变参数的扫描仿真分析,需要进行 20736 次计算,其运算时间还是比较长的。正是由于现实条件是变化多样的,所以我们在进行高速信号仿真时就需要考虑到所有可能出现的情况,在这些现实条件下,尽可能地为所设计的系统提供更大的工作空间。作为高速设计工程师,我们的工作就是找出所有这些可能的工作条件组合,这就是我们前面所讲的可行性设计空间,Solution Space!针对 Solution Space 进行的仿真分析是一种方法学,它能够分析系统设计、制造和生产,以及运行环境中所有可能的情况组合,仿真的结果就是帮助我们找到在各种可能的恶劣条件下,系统还能够正常工作的最健壮的参数组合。一旦找到了这样的目标,剩下的工作就是把这种条件(参数)组合转换成设计规则,应用到系统设计中,指导布局布线。

观察出某些参数变化对信号性能影响的趋势,根据变化趋势,调整关键参数,重新定义设计空间,再进行抽样扫描分析,经过这样逐步求精收敛的过程,缩小设计空间范围,直至形成最终的设计约束规则。

5.7 约束规则生成

对于仿真结果,以反射分析为例,它包含的信息有:SIM ID(模拟次数的标识)、Driver(激励源)、Receiver(接收端)、Cycle(测量的周期)、FTS Mode(仿真模式)、Monotonic(波形单调性)、Noise Margin(噪声裕量)、Overshoot(上过冲)、Overshootlow(下过冲)、Prop Delay(传输延迟,驱动端到接收端)、Switch Delay(开关延迟)和 Settle Delay(建立时间)等。而很多的情况下,我们更看重 SigWave 显示的结果波形图,可以结合波形图一起分析。

一般对信号质量的要求是噪声裕量足够大,上过冲和下过冲不要超过规定电压,没有明显的振铃现象。波形没有严重失真,波形上升沿和下降沿要保持单调性等。从仿真图形中,可以对这些参数有个直观的判断,但对于不同的电路,有时对于传输延迟时间的长短,或者上升时间的快慢有特别的要求,这就需要设计者具体问题具体分析了。有了这些仿真结果,我们接下来就要根据这些仿真结果设定布线的约束,然后将这些约束的定义返回到 Constraint Manager 中。

全部的约束定义是很复杂的,包括阻抗、拓扑结构、传输延迟、建立保持时间及 EMI 等。在实际的设计中,对于某个网络(关键信号)并不是所有的约束类型都要用到,仅对那些需要的规则进行定义就可以了。在本书里,作者只讲解了几个最常用的约束定义方法,更多的功能将留给读者在实际工作中继续学习和掌握。

5.7.1 简单约束设计—Prop Delay

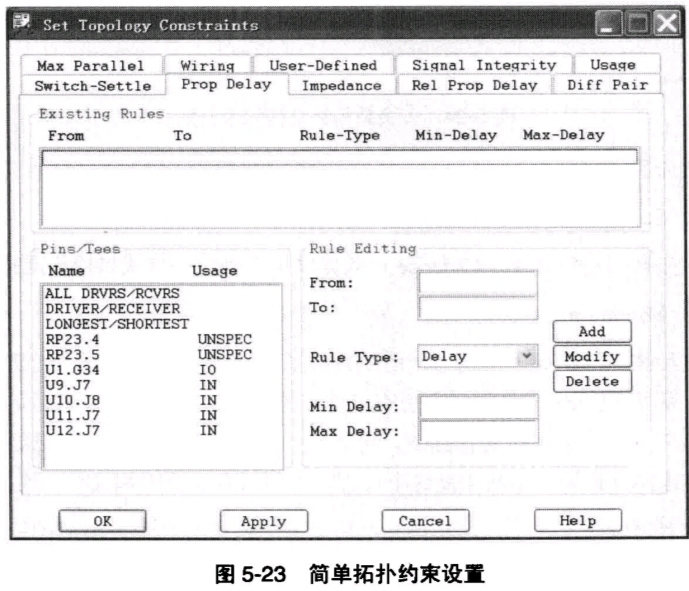

对当前信号进行拓扑约束设计,可以通过在 SigXP 中,在菜单中选择“Set-Constraints...”命令,打开约束设置界面“Set Topology Constraints”,如图 5-23 所示。

在约束设计中,最简单的约束就是绝对传输延迟,也即绝对传输线长度的约束。无须太多的解释,按照图 5-23 所示,左下角的“Pins/Tees”列表框中是当前仿真网络中的所有可选元素(器件),从该列表框中选择要定义约束的起点“From”和该约束的终点“To”,输入最大长度和最小长度就可以了。注意,这里可以以两种方式对长度进行描述,一种是时间单位,即“Delay”,另一种就是真正的长度,即“Length”,在“Rule Type”下拉列表框中选择你需要的单位就好了。这两种描述长度的方式存在于整个 Cadence 系统中,所以在以后的描述中,不再特意区分长度和延迟,请读者根据当时的描述环境进行理解。

特别需要提醒的是,每设置一个规则之后,一定要单击“Add”按钮,这样才能真正生成一个新的约束规则,否则直接单击“OK”按钮之后,刚刚定义的约束规则就会丢失掉。

5.7.2 拓扑约束设计—Wiring

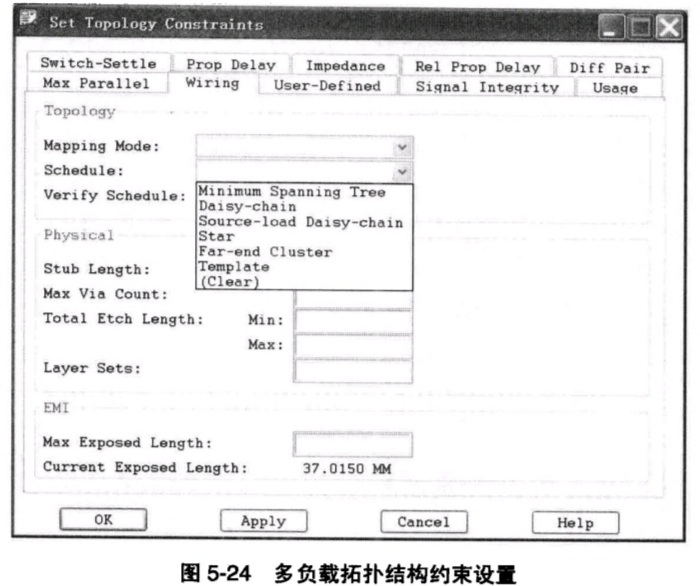

在图 5-23 的“Set Topology Constraints”界面中,单击“Wiring”选项卡,切换到如图 5-24 所示关于 Wiring 布线规则定义的界面。

在 Wiring 布线规则定义的界面中,包括了三部分的内容:Topology—拓扑结构定义,Physical—布线的物理规则定义和 EM—布线控制规则定义。其中,Topology—拓扑结构规则的定义比较复杂、难以理解,而其他两个规则的参数含义都很明了。

首先我们对图 5-24 中,“Topology”区域中的各项规则定义进行讲解。

1. Schedule 拓扑结构定义

在拓扑结构定义中,Cadence 一共提供了七种拓扑方式供用户选择。

• Minimum Spanning Tree(最小生成树)

这种拓扑结构保证网络中所有的连线长度总和为最小。算法的实施过程是这样的,从某个 Driver 开始,在所有未连接的管脚中,寻找离它最近的那个进行连接,然后继续在未连接的管脚中,再寻找一个管脚,这个管脚和已经连接的某个管脚连线距离最短,不断重复这个过程,直到所有的管脚都进行了连接。

读者可以想象一下,这种拓扑结构的随意性很大,最后形成的结构也是不可预期的,也就导致了它的阻抗连续性得不到保证,电气性能很不可靠。所以这种拓扑方式除了能保证所有连线的长度总和最小之外,别无它用,在作者的设计中几乎没有用过这种拓扑结构的约束。当然,这只是作者自己的看法,如果读者有自己独特的应用环境,不妨交流一下。

• Daisy-chain(菊花链)

菊花链不用多说了,做过 PCB 设计的工程师,一定知道这个结构。它在保证每个管脚最多有两个连接的前提下(其实就是串行方式),保证连线总长度最短。

• Source-load Daisy-chain(源负载菊花链)这是一个比较新的拓扑概念。它的算法基本和菊花链的算法一致,但是它有一个限制就是,先连接所有的 Driver 管脚,当所有的 Driver 组成菊花链之后,再开始连接 Receiver 管脚。这种结构相对于菊花链的改进之处就是,能够更好地保证 Driver 到 Receiver 的时序。但是,如果一个网络中所有的管脚都是双向驱动管脚,那么这种拓扑结构就退化成普通的菊花链方式了。

• Star(星形拓扑)

星形拓扑的严格概念是:先按照菊花链的方式把所有的 Driver 连接在一起,然后把所有的 Receiver 管脚直接和菊花链中的最后一个 Driver 相连。

• Far-end Cluster(远端簇拓扑)

这种结构和星形拓扑相似。区别是,在连接最后一个 Driver 和其他所有 Receiver 时,从最后一个 Driver 延展出一段传输线,然后做出一个 Tee 点,所有的 Receiver 和这个 Tee 点相连,而不是直接和最后一个 Driver 相连。

• Template(用户模板拓扑)

用户自己决定如何连接当前网络中的所有管脚,然后把这种用户自定义的连接方式作为一个拓扑结构的模板。

• 不使用任何拓扑结构的约束,以随机方式任意连接网络中的各个管脚

对于这些网络结构的优缺点讨论,本书的 3.3.2.2 一节中已经做了详细的阐述。在拓扑结构设置中的这些拓扑结构形式,其本质结构都源于本书 3.3.2.2 一节中的基本类型,读者在使用这些拓扑结构时,要非常清楚这些拓扑结构的优缺点和适用场合。

2. Mapping Mode 映射规则定义

在对网络定义了拓扑结构规则之后,我们就可以应用这个网络的拓扑结构,这里叫映射,到系统中的其他网络,那么映射过程也要有一定的方式和规则。Cadence 设计理念中,拓扑结构的映射,基于以下几个规则。

• Pinuse—管脚类型

在进行网络拓扑映射时,依据网络中的管脚类型,即 Input、Output、Bidir 和 Unspec 这些类型,进行映射。同类型的管脚在网络映射中具有相同的地位和优先级。这种映射规则有时会被使用到。

• Refdes—器件标号

按照器件标号进行映射,属于相同器件的管脚在网络映射中具有相同的地位和优先级。这种映射规则很少被使用到。

•Pinuse And Refdes—器件标号和管脚类型同时使用

同时按照器件标号和管脚类型进行映射,属于相同器件的管脚或者同类型的管脚在网络映射中具有相同的地位和优先级。这种映射规则使用最频繁。

• Clear—不指定映射规则

即在映射时完全采取随机的方式对拓扑结构进行映射,不加以任何限制。

拓扑结构的映射规则对仿真结果的使用具有非常重要的作用。如果映射方式不对,那么对某个网络所定义的布线规则就没有办法被其他类似的网络重复利用,所以必须重视映射规则的使用。有些工程师觉得映射规则很难掌握,总是不能很好地定义映射方式。其实,对于映射规则的使用只要掌握一点即可,那就是在运用映射规则之前要考虑清楚,欲采用的映射规则所能涵盖(控制)的对象范围到底有多大?搞清楚了这个问题,那么映射规则的使用就不难了。

在这里说句题外话,读者可以看到,器件的类型和管脚类型的使用,会贯穿于 Cadence 高速设计系统的始终。因此从第一步,做原理图器件库开始,就要对器件的类型及管脚类型有明确而准确的定义,否则在接下来的布局布线中,甚至生产流程中,都会遇到很多问题,导致工作流程不能正常继续。虽然 Cadence 设计工作在每一步都提供了对设计元素的属性进行修改的机会和工具,但是这种在设计流程中半途所做的修改,会导致整个设计中数据信息不一致的错误,也会对将来的 IP 设计复用带来隐患。

3. Verify Schedule 拓扑结构校验

这个参数是让设计决定,如果一个网络被映射了某种拓扑结构,那么对拓扑结构的检查是否属于 DRC(Design Rules Check)中的一项。

除了拓扑结构规则定义之外,在 Wiring 布线规则定义的界面中,还包括布线的物理规则定义和 EMI 布线控制规则定义。这两个规则的参数含义还是比较清楚的,不需要再占用篇幅讲解。如果读者对这两个参数有疑问的话,可以直接单击当前界面上的“Help”按钮,从帮助文件中学习。

5.7.3 时序相关的约束设计—Switch-Settle Delay

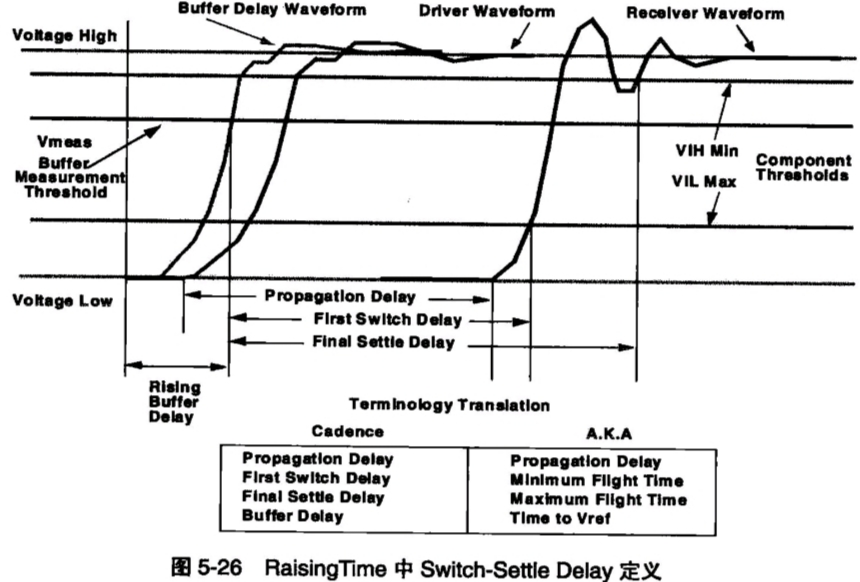

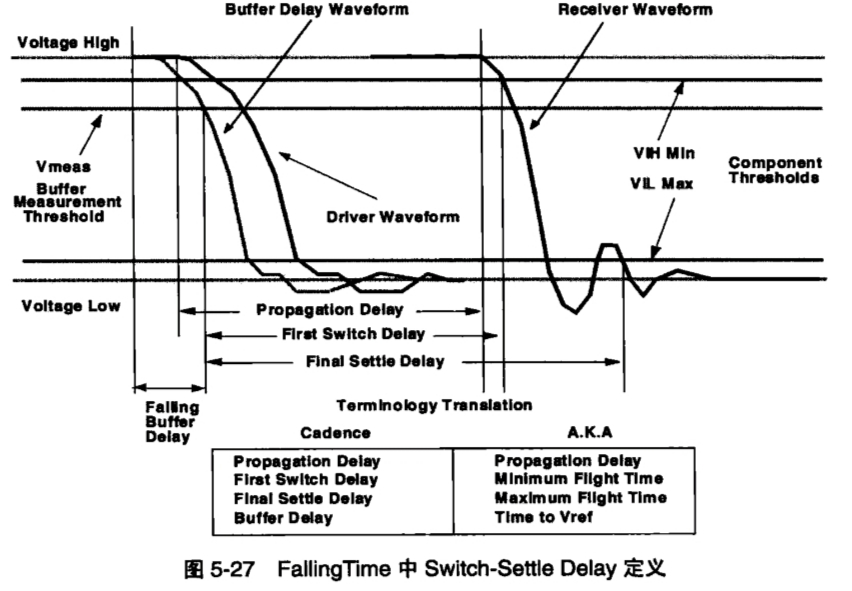

时序相关的约束的设置界面非常简单,如图 5-25 所示,其使用方法和前面介绍的设置界面基本相同。

之所以把这个问题单独拿出来讨论,是因为在 Cadence 设计系统中,有些术语名词和业界的一些命名稍有区别,如果不了解这些差别,可能在理解和交流上造成误解。Switch-Settle Delay 分为上升时间 RisingTime 和下降时间 FallingTime 两种情况。这两种情况下的 Delay 术语及所对应的时间起图,请分别参照图 5-26 和图 5-27 中的图示定义进行理解。这两个图多次出现在 Cadence 的技术资料和帮助文件中,希望读者认真解读图中各参数所表达的信息,以免在使用 Cadence 系统的过程中出现误解导致仿真错误。