时序约束高级进阶使用详解二:Set_Min_Delay

目录

一、前言

二、设计示例

2.1 示例代码

2.2 时序约束

三、Set_min_delay

3.1 start points

3.1.1 对象有效性

3.1.2 边沿有效性

3.1.3 start point非有效起点

3.2 Through points

3.2.1 约束对象为Cells

3.2.2 约束对象为Cell pin/Net

3.3 to points

3.4 rise/fall

3.5 Reset path

3.6 多对象设置

3.7 Max_delay 与 Min_deay

一、前言

关于Set_max_delay/Set_min_delay的基础用法之前的文章已进行过简单的介绍,主要作用就是修改时序路径默认的setup/recovery或hold/removal时间要求,本章将对约束Set_min_delay的一些细节使用进行解释。

二、设计示例

以一个简单的3个触发器为例,包含同步时钟路径和异步时钟路径,以异步时钟路径为主

2.1 示例代码

module MAX_MIN(d1,clk1,clk2,ce,ff3);

input d1,clk1,clk2,ce;

output ff3;

reg ff1,ff2,ff3;

wire bus;

always@(posedge clk1,negedge ce)

begin

if(!ce)

begin

ff1<=0;

end

else begin

ff1<=d1;

end

end

always@(posedge clk2,negedge ce)

begin

if(!ce)

ff2<=0;

else begin

ff2<=ff1;

end

end

assign bus=ff2+ff1;

always@(posedge clk2)

begin

if(!ce)

ff3<=0;

else begin

ff3<=bus;

end

end

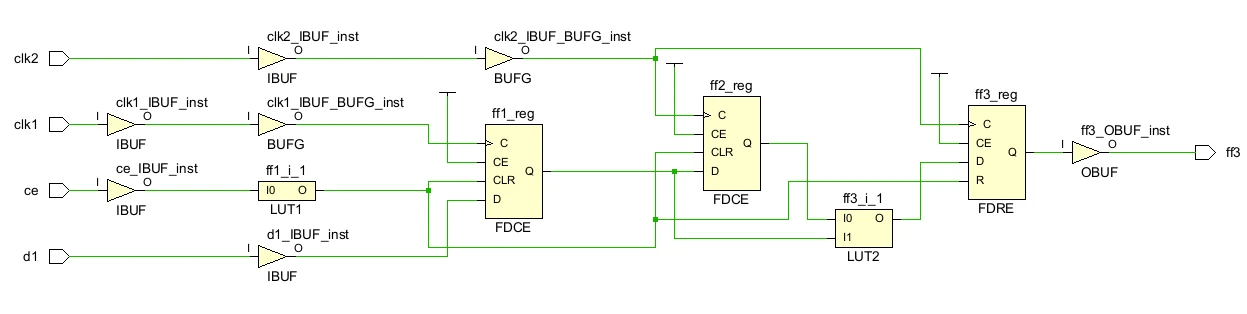

endmodule连接关系如下图,clk1中同步时序路径下,ff1_reg到ff2_reg,clk1与clk2的异步时序路径中,ff1_reg和ff2_reg逻辑运算后输出到ff3_reg

2.2 时序约束

此处主要是主时钟约束

create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} -add [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} -add [get_ports clk2]三、Set_min_delay

Set_min_delay约束的设置中,不仅可以指定起点,中间点,终点,还可以设置对应单元生效的上升沿或下降沿,生成时序报告时建议将配置nworst和max path设大,可报告出所有路径

3.1 start points

start points为set_mix_delay约束的时序路径起点,需为时序路径的有效起点,可为Clock,Cell,Cells pin,IO port

3.1.1 对象有效性

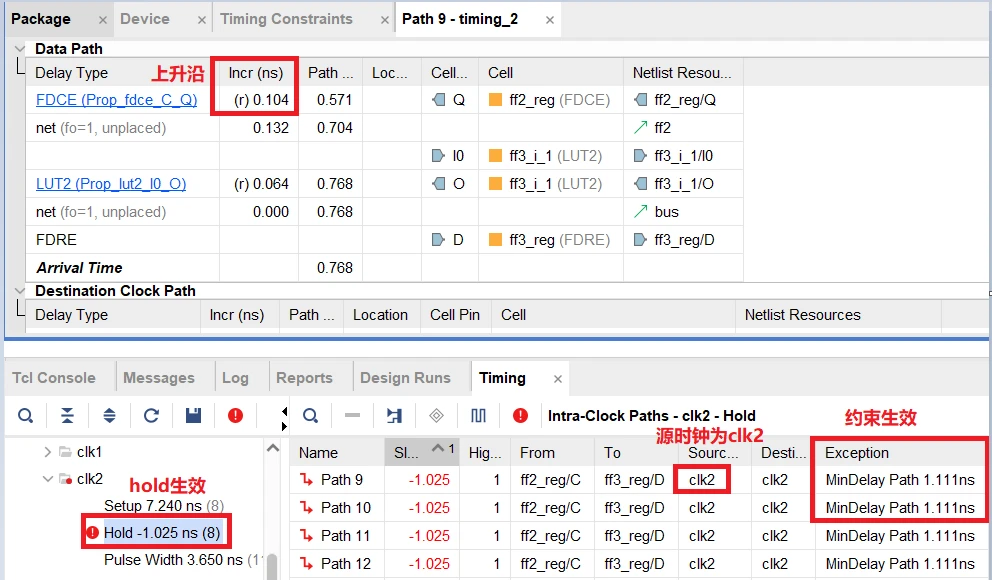

以clock为clk2为例,设置约束如下

set_min_delay -rise_from [get_clocks clk2] 1.111只有以clk2为源时钟,并且上升沿触发的时序路径约束才会生效

源时钟为clk1,目的时钟为clk2的不属于约束范围

3.1.2 边沿有效性

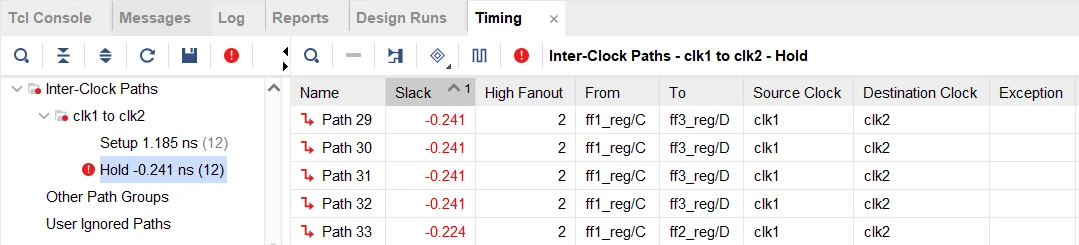

对源时钟为clk1,下降沿的路径设置min_delay

set_min_delay -fall_from [get_clocks clk1] 1.111下面ff1_reg到ff2_reg的路径因为clk1为上升沿,因此min_delay约束不生效

将约束设置为clk1的上升沿有效

set_min_delay -rise_from [get_clocks clk1] 1.111此时约束生效

3.1.3 start point非有效起点

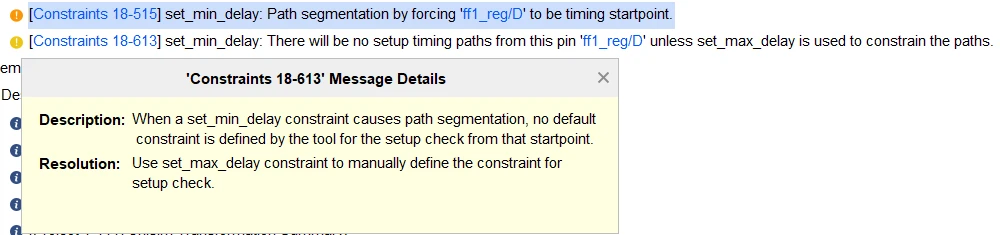

将ff1_reg/D设置为min_delay的起点,因为ff1_reg/D不是有效的时序路径起点,约束不会生效

set_min_delay -from [get_pins ff1_reg/D] 1.111同时有对应的告警

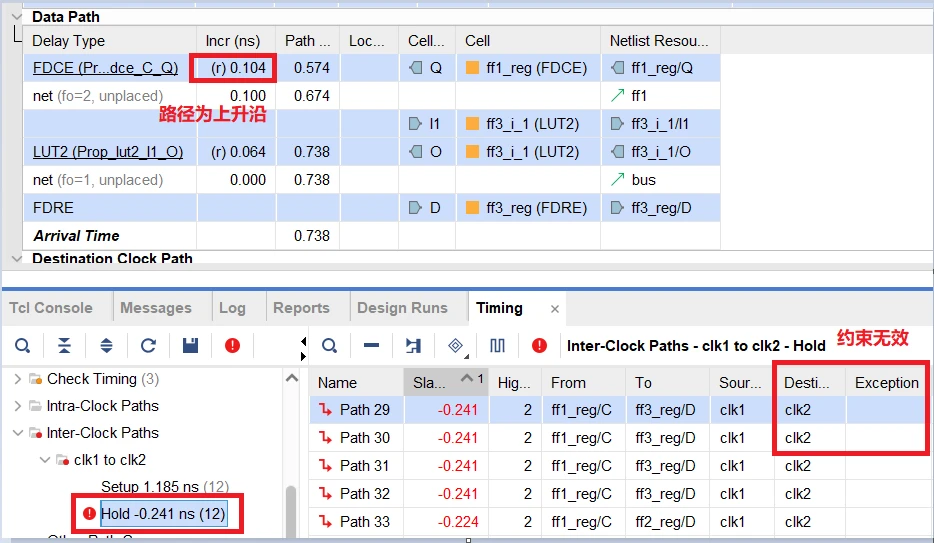

如果将ff1_reg/C设置为max_delay的起点,同时上升沿有效

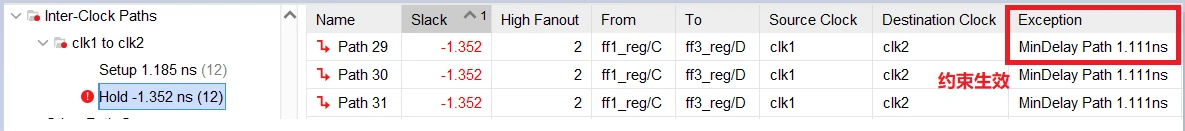

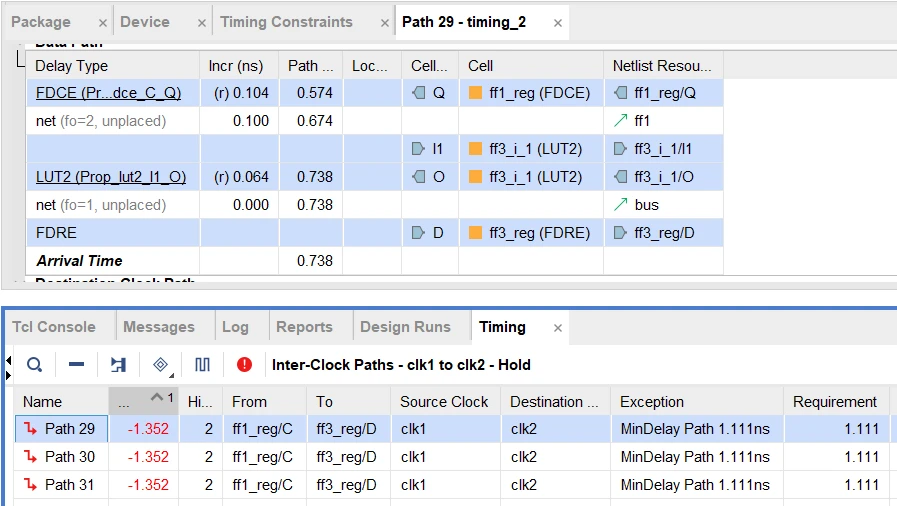

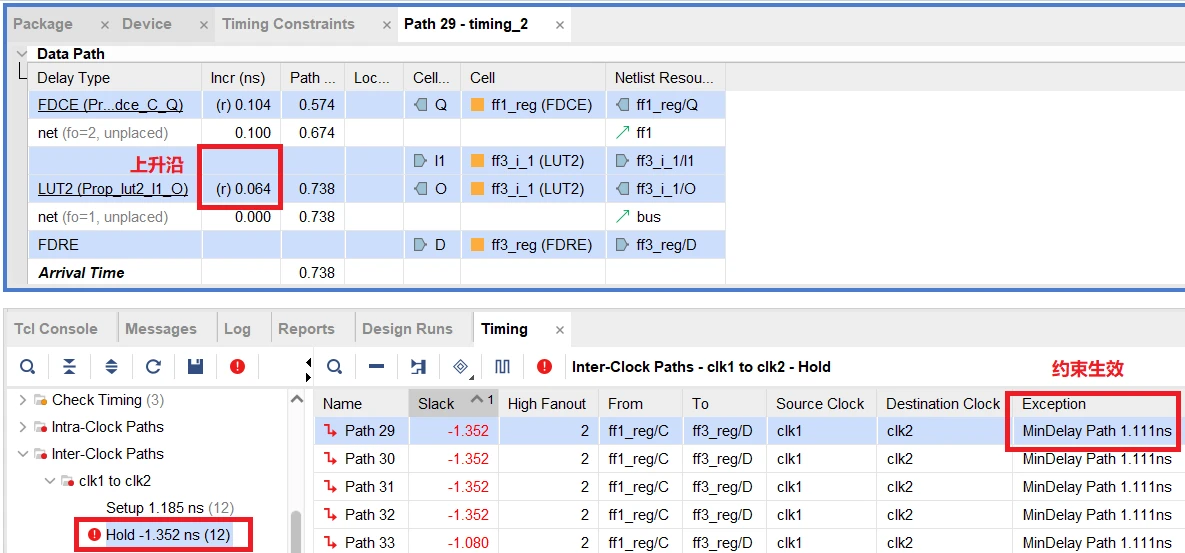

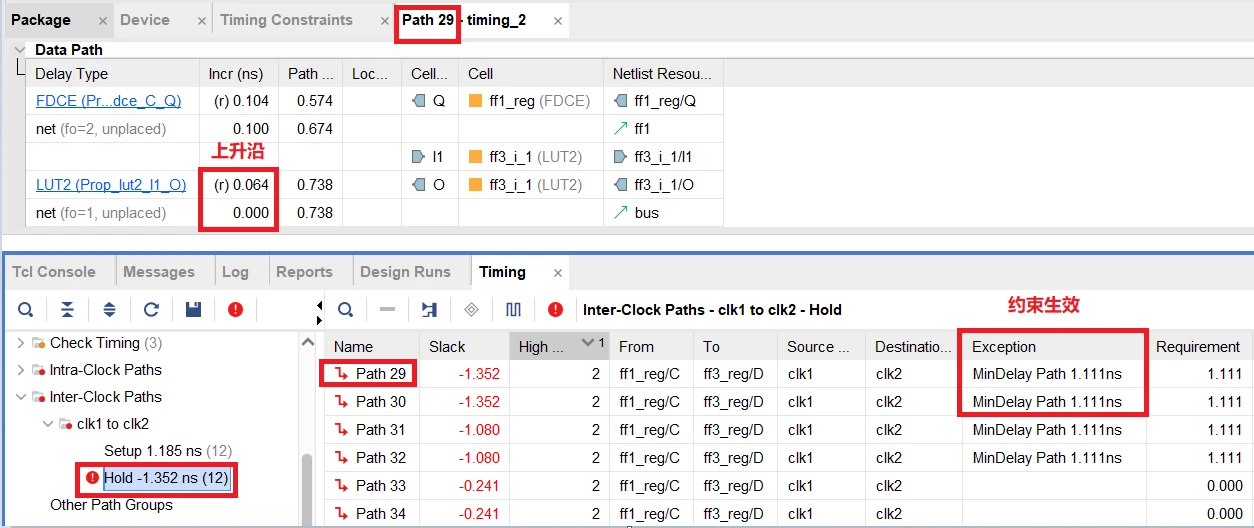

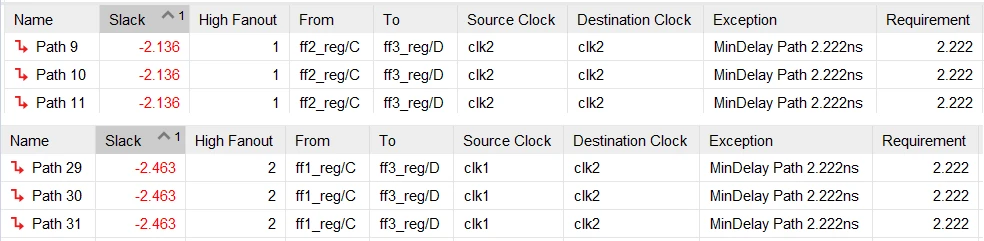

set_min_delay -rise_from [get_pins ff1_reg/C] 1.111以path29的结果看出,符合上述约束条件,因此约束生效

3.2 Through points

3.2.1 约束对象为Cells

约束对象为Cell时,设置的Transition边沿是直接对该单元的相应边沿生效,查看的路径都是ff1_reg到ff3_reg的时序路径

a)以经过中间的组合逻辑ff3_i_1(LUT2)为例,Transition默认为rise/fall,即上升沿下降沿都支持,在Transition为默认值时,约束命令如下

set_min_delay -through [get_cells ff3_i_1] 1.111查看对应的时序报告结果,此时ff3_i_1使用为上升沿时约束生效

查看ff3_i_1为下降沿时的路径,约束依旧生效

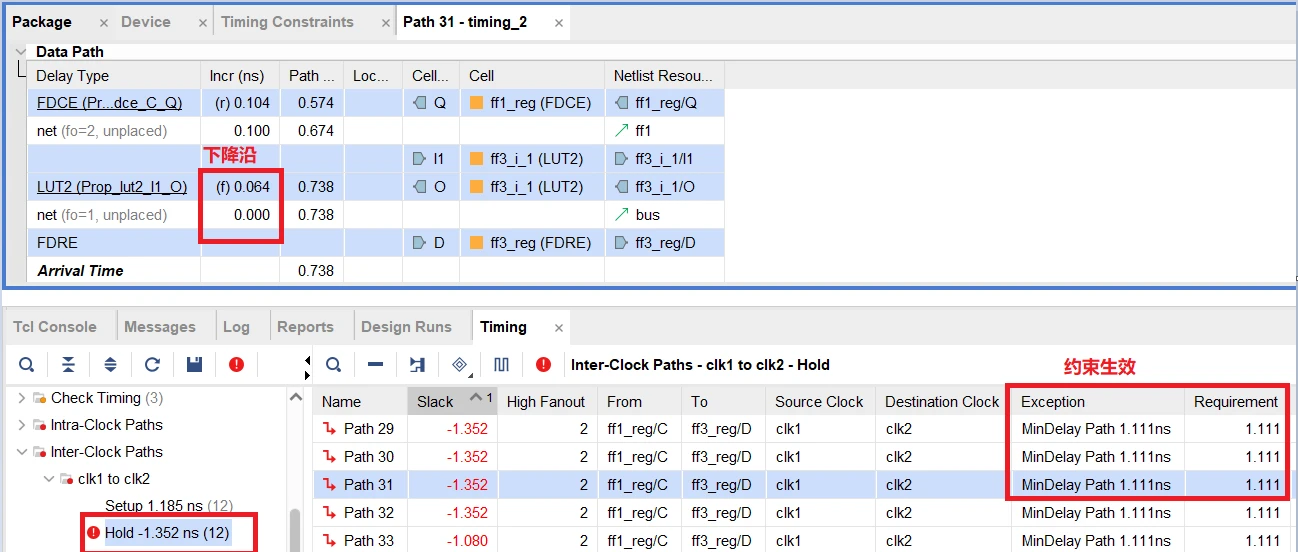

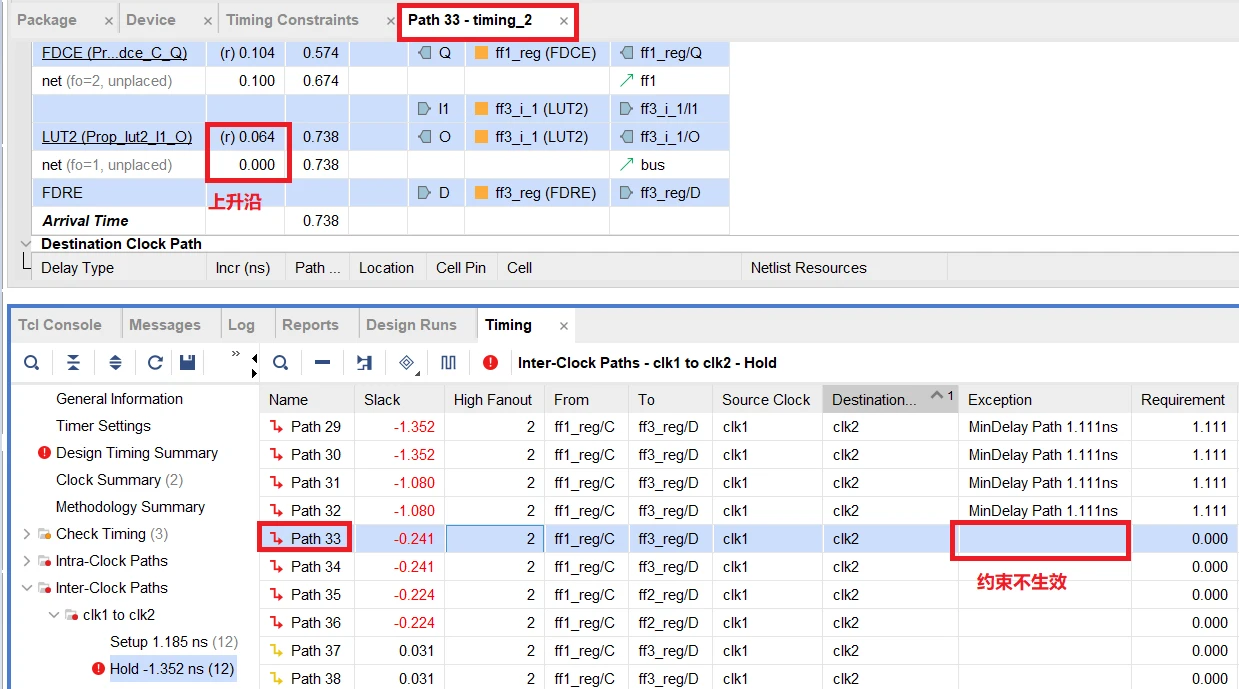

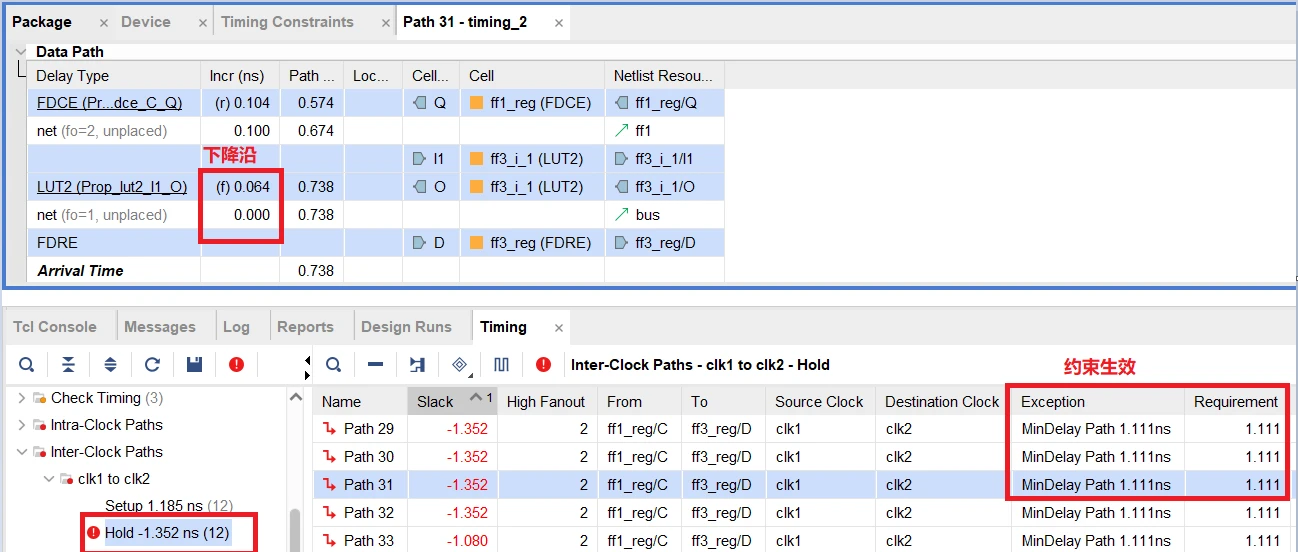

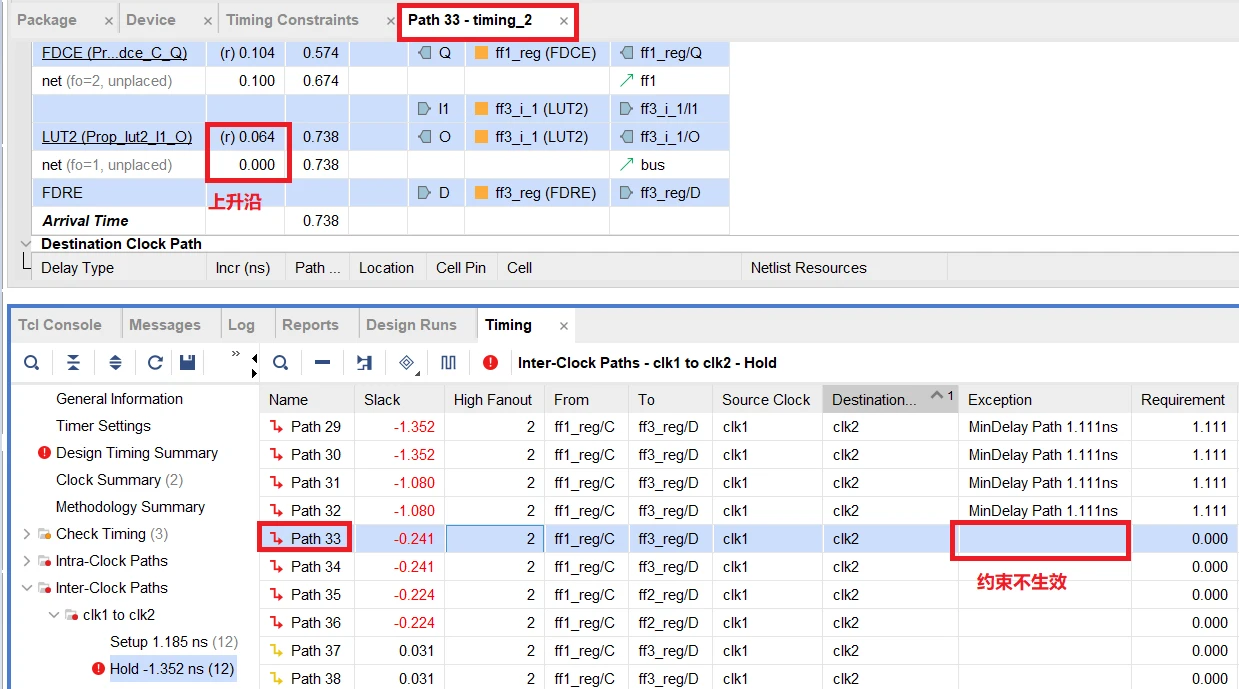

b)修改约束,指定Transition为下降沿fall_through

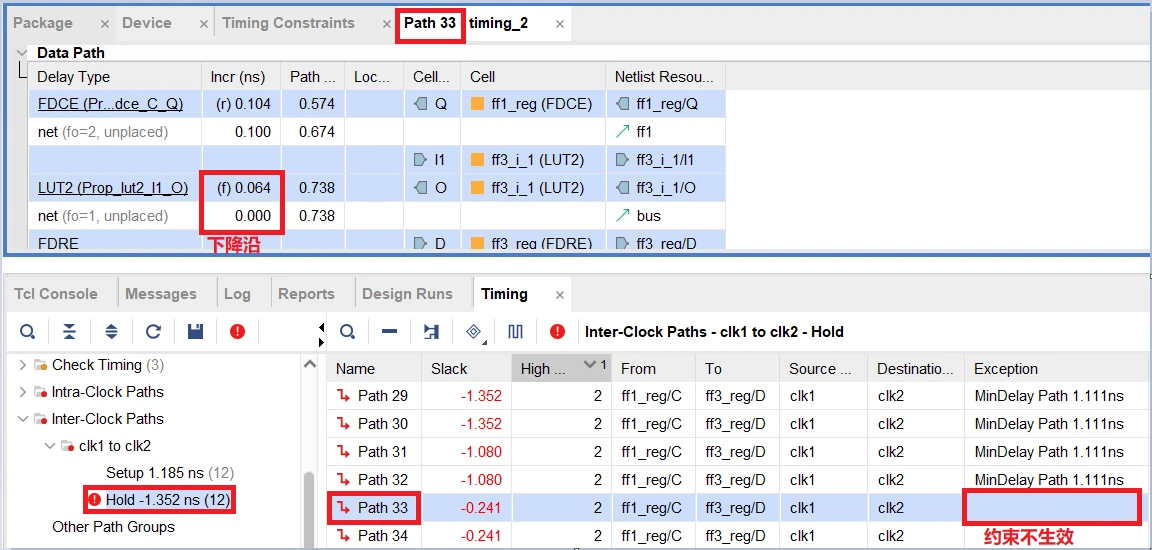

set_min_delay -fall_through [get_cells ff3_i_1] 1.111此时时序路径中ff3_i_1为下降沿的4条路径,约束生效

ff1_reg到ff3_reg的另外4条路径中因为ff3_i_1为上升沿,故约束不生效

3.2.2 约束对象为Cell pin/Net

当through point的对象更加具体,如为pin时,此时Transition是体现在对应对象的时序边沿上

a)修改约束对象为pin,指定ff3_i_1/I0为下降沿fall_through

set_min_delay -fall_through [get_pins ff3_i_1/I0] 1.111时序报告中,ff2_reg到ff3_reg中约束生效的4条路径中,ff3_i_1前面连接的ff2_reg都为下降沿触发

对于另外4条ff2_reg到ff3_reg约束未生效的的时序路径中,ff2_reg为上升沿触发,故不属于约束生效的范围

3.3 to points

to points的与start points的使用相同,可参见start piont的介绍

3.4 rise/fall

在options中勾选Only rising/falljing path delays are to be constrained,下拉框中选择rising/falling可对约束路径设置边沿生效,边沿为终点数据端口的边沿

以下列约束rise为例

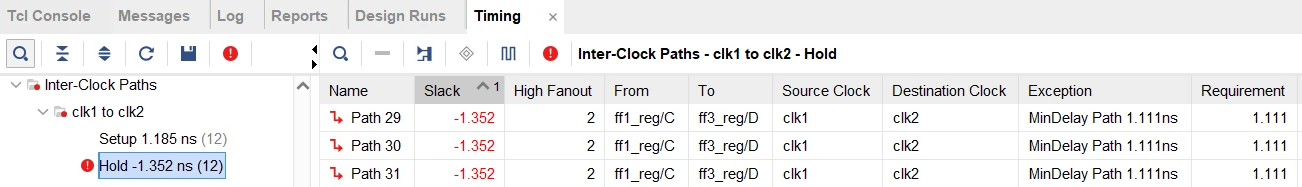

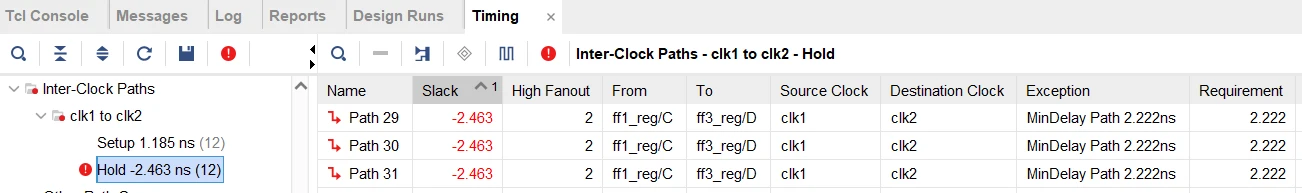

set_min_delay -rise -from [get_clocks clk1] 2.222第29号路径生效,对应data path中ff2_reg/D的边沿为上升沿

第17号路径中,data path中 ff2_reg/D的边沿为下降沿,故不生效

3.5 Reset path

Set min delay约束中存在一个配置项"Remove existing path exceptions before setting path delays",即约束的路径上如果已存在max_delay时序约束时是否被新的覆盖

以如下两条约束为例,

set_min_delay -from [get_clocks clk1] -to [get_clocks clk2] 1.111

set_min_delay -from [get_clocks clk1] 2.222第二条max_delay无reset_path时,尽管第二条是后加的,但生效的是第一条约束1.111

如果第二条约束添加-reset_path,则会覆盖第一条的约束

set_min_delay -from [get_clocks clk1] -to [get_clocks clk2] 1.111

set_min_delay -reset_path -from [get_clocks clk1] 2.222报告结果如下图

3.6 多对象设置

start/through/to中也可以同时设置多个对象,将同时生效。如下图中对from为ff1_reg/C和ff2_reg/C的时序路径都设置max delay为2.222ns

set_min_delay -from [get_pins {ff1_reg/C ff2_reg/C}] 2.222相关路径都将生效

3.7 Max_delay 与 Min_deay

set_max_delay和set_min_delay的使用较多共同之处,下面对其它们的特点进行总结

1)set_max_delay为约束setup/recovery的requirement时间,set_min_delay为约束hold/removal的requirement时间,二者相互独立

2)set_max_delay支持通过设置datapath only只考虑发起时钟的数据路径延迟,set_min_delay不支持

3)set_max_delay如果设置了datapath only,则不会对对应的路径进行hold分析,即不存在hold路径

4)set_max_delay如果设置了datapath only,必须设置from对象

5)set_max_delay/set_min_delay不适合用于输入端口/输出端口到对应时序单元的路径约束,输入端口/输出端口的约束应使用set_input_delay/set_output_delay

6)set_max_delay/set_min_delay如果约束的不是有效的起点或终点,会出现时序分段现象,即该位置的前面(from)或后面(to)的时序传播会断开,使约束的位置称为有效的起点或终点,其他经过约束位置的路径全部受影响