ASP4644双PLL频率同步架构:多相降压系统的工程验证

引言

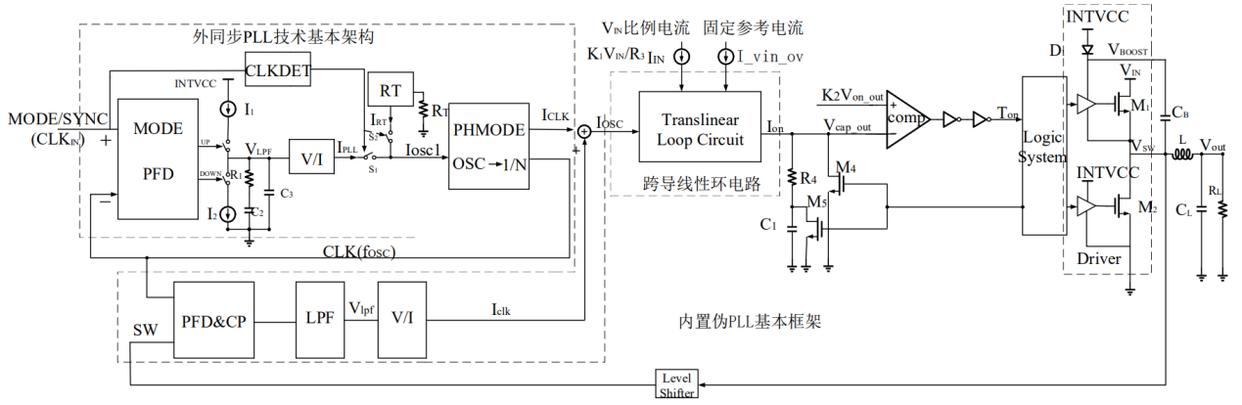

现代便携式电子设备与分布式电源系统对DC-DC变换器提出了高频化、低EMI及快速瞬态响应的复合要求。恒定导通时间(COT)控制架构凭借其环路结构简洁、瞬态响应迅速等固有优势,在降压型Buck变换器领域获得广泛应用。然而,传统COT架构的开关频率随输入电压、负载电流及外部元件参数漂移而显著变化,导致EMI频谱难以预测、多相并联时均流精度恶化,并可能引发音频噪声干扰等工程问题。国科安芯推出的ASP4644芯片采用双锁相环(Dual-PLL)协同控制架构,通过频率同步PLL与时钟同步PLL的级联耦合机制,实现开关频率对外部参考时钟或内部可编程频率的自适应跟踪。本文对该架构的工程可行性、电路实现细节及多相并联应用价值进行系统性技术分析。

COT控制架构的固有局限与演进需求

COT控制模式的理论开关频率fSW ≈ VOUT/(VIN·Ton),在稳态下应保持相对恒定。然而工程实践中,比较器延迟、驱动传播延时及死区时间的工艺角漂移、温度变化等因素导致有效Ton偏离设计值。轻载时进入DCM模式引入附加谐振周期,进一步加剧频率不可控性。多相并联时,各相PCB走线寄生参数差异引起时钟skew,破坏相位交错精度。单PLL时钟同步方案虽可锁定振荡器频率,但无法消除功率级延迟引入的相位误差,难以实现逐周期精确跟踪。

ASP4644提出的Dual-PLL架构将频率锁定分解为"时钟源同步"与"功率级跟踪"两个子任务,通过电流域跨导线性环实现低延迟耦合,为多相系统的相位精确控制提供了新的技术路径。

双PLL架构原理与系统框图

ASP4644系统架构严格遵循功能模块化原则,划分为七大功能单元。其中频率同步PLL与时钟同步PLL构成双环控制核心。为行文清晰,本文将前者称为"外同步PLL",后者称为"内置伪PLL"。

外同步PLL:振荡器频率基准生成

外同步PLL由鉴频鉴相器(PFD)、电荷泵(CP)、跨导OTA、RT电流产生电路、六级差分环振振荡器及分频器构成。当SYNC引脚检测为悬空、接地或电源电位时,时钟选择电路判定为内部频率编程模式,振荡器频率由RT引脚外接电阻设定的电流决定;当检测到有效外部时钟(幅值需大于1.8V高电平、小于0.4V低电平)且频率高于阈值时,PFD逐周期比较外部时钟与分频器输出相位,CP将误差转换为电压,经OTA调节振荡器偏置电流,实现频率锁定。

振荡器每级通过电容充放电产生延迟,整体频率由偏置电流与电容比值决定,并可通过trimming端口修调。分频器提供1/12分频输出,并支持通过PHMODE引脚配置两相、三相或四相输出(相位差分别为π、2π/3、π/2)。

内置伪PLL:功率级频率跟踪

内置伪PLL构成频率锁定外环,其参考频率为振荡器输出fCLK,反馈信号取自SW节点经电平转换后的开关脉冲。该PLL的独特之处在于其输出不直接调节振荡器,而是转换为电流Iclk注入跨导线性环,进而调节Ton产生电路的充电电流Ion,由此构成"频率误差→电流调整→时间修正→频率补偿"的间接反馈路径。

跨导线性环是连接双PLL的枢纽,由双极型晶体管Q1-Q4构成电流模式运算单元。Q1集电极电流为外同步PLL电流IPLL与伪PLL调整电流Iclk之和(比例1:2),Q2为VIN比例电流,Q4输出Ion驱动Ton电容。基于跨导线性原理,环路满足电流约束关系:Ion与Iosc、IIN成比例关联。

时间超前AOT电路:Ton自适应调节

Ton产生电路通过电容C的恒流充电过程计时,当电压达到VON阈值时比较器翻转。VON由VOUT电压经TON_VOUT电路钳位限定,Ion经跨导线性环调节后正比于VIN/fSW。在Burst模式下,DCM_add信号控制附加电容并联,延长Ton以降低轻载开关频率。

设计约束:Ton的精度取决于Ion的匹配度、比较器延迟及电容绝对值精度。开关频率稳定度需在-40℃至125℃全温区、±10%电源电压波动下验证。

关键模块电路技术分析

跨导线性环的工程实现

跨导线性环基于双极型晶体管的指数特性实现电流域运算。Q1-Q4形成发射结电压闭环,顺时针与逆时针方向结压降之和相等,由此导出电流约束关系。该架构优越性在于将频率误差信号转换为电流模式处理,避免电压域传输的RC延迟累积,适合高频应用。

工程实现中,器件匹配提出严苛要求。Q1-Q4的发射区面积比、电流镜复制精度及Early电压效应均会引入误差。

高精度基准源设计

电压基准:带隙基准摒弃传统高增益运放钳位,改用三极管Q3-Q4电流密度匹配自偏置,简化电路并降低功耗。M6管作为隔离级改善中低频PSRR。启动电路采用交叉耦合结构,规避零电流简并点,无需额外启动支路。

电流基准:运放选用套筒式共源共栅架构,在3.3V电源下实现高增益。该结构输出IREF为跨导OTA提供偏置。

高速比较器设计权衡

ICOMP比较器:四级放大结构,前两级电阻负载将主极点推向高频。PTAT偏置电流补偿高温下跨导衰减,但延迟随工艺角变化未予量化,影响高频相位裕度。

反流比较器:三级结构追求最低延迟,失调电压与噪声性能逊于ICOMP。

SW电平转换电路的接口意义

该电路将高压域SW信号转换至3.3V逻辑域,为内置伪PLL提供反馈。

多相并联的工程考量

ASP4644支持两相、三相、四相可配置输出。理论上,双PLL架构可确保各相频率锁定于fCLK,相位差由分频器生成,均流精度取决于功率管参数匹配与PCB对称性。

应用场景与技术定位

ASP4644目标市场为智能手机、SSD等音频敏感应用,及通信设备POL转换器等需多相并联场合。其技术价值在于不依赖数字补偿的纯模拟频率同步,相比数字COT方案具备低延迟、可预测EMI频谱的潜在优势;相比传统模拟COT,解决了多相同步难题。

技术局限性亦明确:工艺匹配要求高,修调增加测试成本;AOT降频范围有限,极轻载效率或不及数字PFM;外同步时钟需满足幅值频率双重要求,接口兼容性较弱。

结论:架构创新与工程实现的鸿沟

ASP4644的双PLL架构在理论层面具备原创性与合理性。通过外PLL锁定振荡器、伪PLL跟踪功率级、跨导线性环电流域耦合,为多相COT变换器提供了新颖同步路径。关键模块设计体现BCD工艺工程经验。