EUV光刻实战:突破7nm芯片制造的关键技术与挑战

一、引言:EUV光刻的革命性意义

随着半导体行业向7nm及更先进节点迈进,传统深紫外线(DUV)光刻技术面临物理极限挑战。DUV光刻使用193nm波长,通过多重图案化(如SADP、SAQP)来实现小特征尺寸,但这增加了工艺复杂度、成本和缺陷率。极紫外线(EUV)光刻作为突破性技术,采用13.5nm波长,单次曝光就能实现7nm分辨率,从而简化流程、提高良品率并延续摩尔定律。EUV光刻自2019年起在台积电(TSMC)和三星等领先代工厂实现量产,用于7nm和5nm节点,成为高性能CPU、GPU和AI芯片制造的核心。

EUV光刻的优势源于其短波长带来的高分辨率。在7nm节点,EUV能直接将复杂图形转移到晶圆上,避免多重曝光带来的套准误差和成本增加。然而,EUV技术也引入新挑战,如光源功率不足、掩模版缺陷和成本高昂。本文将深入解析EUV光刻的核心技术、实战挑战及解决方案,并以台积电7nm工艺为案例,提供可操作的指南。

二、EUV光刻核心技术解析

EUV光刻系统由光源、光学系统、掩模版和光刻胶等关键组件构成。其工作原理基于13.5nm波长的极紫外线,通过反射式光学元件将掩模版图形投影到晶圆表面。以下解析核心要素。

2.1 光源与曝光系统

EUV光源采用激光激发等离子体(LPP)技术:高功率CO₂激光轰击锡滴,产生等离子体并发射13.5nm波长光。光源功率是关键参数,直接影响曝光速度和质量。当前ASML的NXE:3400B EUV光刻机光源功率达250W,支持每小时125片晶圆的产能。但功率稳定性挑战依然存在,波动会导致曝光剂量不均,造成线宽变化。

光学系统全部为反射式,因为EUV光会被任何材料吸收。掩模版和镜片使用多层膜(如钼/硅堆叠)来反射EUV光。反射率约70%,因此需要多个镜片(通常6个),但光路损失仍较高。对准系统基于激光干涉仪和高速传感器,实现纳米级套准精度,确保图形与晶圆现有层对齐。

2.2 光刻胶与掩模版

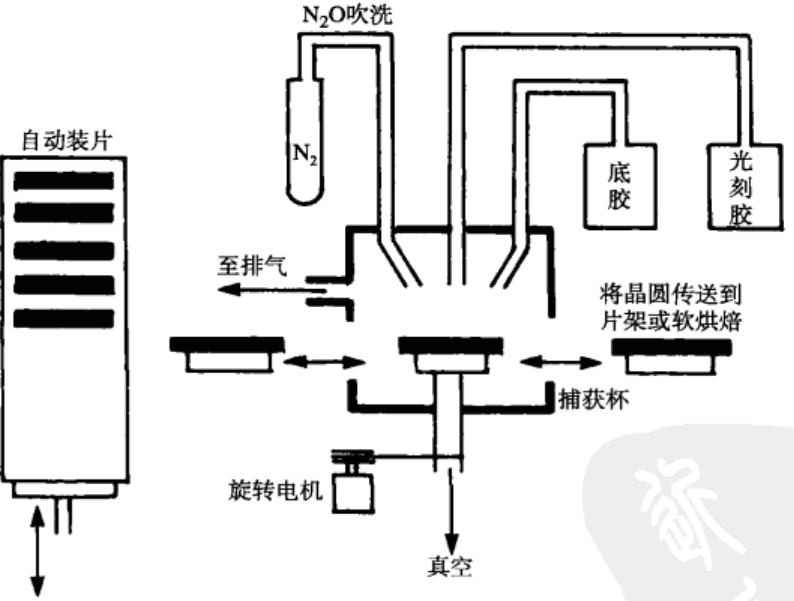

EUV光刻胶需要高灵敏度以降低所需曝光剂量,从而减少曝光时间并提高产能。化学放大光刻胶(CAR)是主流选择,通过光酸发生器(PAG)在曝光后催化反应,实现高对比度和低线边缘粗糙度(LER)。典型灵敏度为20-30mJ/cm²,LER需小于2nm。

掩模版为反射式,由衬底、多层膜和吸收层(如钽氮化物)组成。缺陷控制是最大挑战:即使微小颗粒也会导致图形畸变。台积电采用严格掩模版清洗和检测流程,结合电子束检测和AI算法,将缺陷密度控制在0.01/cm²以下。

2.3 对准与成像精度

套准精度是光刻的关键指标,要求优于特征尺寸的1/3。对于7nm节点,套准容差需小于2.3nm。EUV系统使用基于衍射的对准标记和实时反馈系统,通过调整晶圆台位置来补偿热和机械误差。成像质量受光学像差和掩模版缺陷影响,需通过计算光刻(如逆光刻技术ILT)进行优化。

# 示例代码:EUV曝光剂量计算模型

import numpy as npdef calculate_euv_dose(sensitivity, throughput, power):"""计算EUV曝光所需剂量和曝光时间。参数:sensitivity: 光刻胶灵敏度 (mJ/cm²)throughput: 目标产能 (晶圆/小时)power: 光源功率 (W)返回:dose: 实际曝光剂量 (mJ/cm²)exposure_time: 每片晶圆曝光时间 (秒)"""field_size = 26 * 33 # 曝光场面积 (mm²)energy_per_wafer = sensitivity * field_size * 1e-2 # 转换单位为Jexposure_time = energy_per_wafer / poweractual_throughput = 3600 / exposure_time# 调整剂量以匹配目标产能if actual_throughput < throughput:dose = sensitivity * (throughput / actual_throughput)else:dose = sensitivityreturn dose, exposure_time# 示例计算:台积电7nm EUV工艺参数

sensitivity = 30 # mJ/cm²

throughput = 125 # wafers/hour

power = 250 # W

dose, time = calculate_euv_dose(sensitivity, throughput, power)

print(f"所需剂量: {dose:.2f} mJ/cm², 曝光时间: {time:.2f} 秒")三、现实挑战与应对策略

EUV光刻虽前景广阔,但面临多重挑战。本节采用“挑战-解决方案”格式,基于台积电量产经验展开。

挑战1:光源功率与稳定性

问题:EUV光源功率不足会导致曝光时间长,产能低下。功率波动还会引起剂量误差,造成线宽不均匀。早期EUV光源功率仅100W,产能低于60片/小时,无法满足经济性要求。

解决方案:台积电与ASML合作,通过优化CO₂激光器和锡滴控制,将功率提升至250W。同时,采用实时监控系统,利用传感器监测功率波动,并通过反馈调整曝光参数。例如,在生产线中集成AI算法,预测功率趋势并提前补偿,将剂量误差控制在±1%以内。

挑战2:缺陷与污染控制

问题:掩模版缺陷和颗粒污染是EUV良品率的主要杀手。反射式掩模版易吸附颗粒,且EUV光对缺陷敏感,会导致图形桥接或断裂。此外,光刻胶残留和侧壁聚合物在刻蚀后难以去除。

解决方案:

- 掩模版方面:采用 pellicle(保护膜)减少颗粒吸附,但EUV pellicle材料开发难度大。台积电使用多重清洗步骤:先采用氢氟酸湿法清洗,再用等离子体干法清洗,确保掩模版洁净。

- 污染控制:借鉴洁净室微环境技术,如SMIF(标准机械接口)系统,将晶圆与人员隔离。在光刻区维持ISO 1级洁净度(每立方英尺颗粒数<1),并使用在线颗粒监测器。

- 光刻胶去除:组合干湿法工艺:先用氧等离子体灰化去除有机残留,再用硫酸-过氧化氢混合液湿法清洗金属离子。台积电7nm生产线由此将缺陷密度降至0.1/cm²以下。

挑战3:成本与可制造性

问题:EUV光刻机价格超1.5亿美元,且运行成本高。工艺窗口窄,对参数变化敏感,增加调试难度。

解决方案:

- 成本优化:通过提高产能和良品率摊薄成本。台积电在7nm节点将EUV用于关键层(如金属互连),减少多重曝光次数,从而降低总成本。

- 工艺窗口扩大:采用计算光刻和AI驱动优化。例如,使用逆光刻技术(ILT)设计掩模版图形,增强成像鲁棒性。台积电部署内部开发的AI软件,模拟曝光过程并自动调整参数,将工艺窗口扩大20%。

- 预测性维护:基于大数据分析设备状态,提前更换易损件,减少停机时间。

# 示例代码:AI驱动的EUV参数优化

import tensorflow as tf

from sklearn.ensemble import RandomForestRegressordef optimize_euv_parameters(data):"""使用机器学习优化EUV曝光参数。参数:data: 历史数据,包含剂量、焦距、线宽等返回:best_params: 优化后的参数组合"""# 特征工程:选择关键参数features = data[['dose', 'focus', 'pressure']]target = data['cd'] # 关键尺寸(critical dimension)# 训练随机森林模型model = RandomForestRegressor(n_estimators=100)model.fit(features, target)# 生成参数建议best_params = model.predict(features)return best_params# 模拟数据

import pandas as pd

data = pd.DataFrame({'dose': [30, 32, 28, 31],'focus': [0.1, 0.05, 0.2, 0.15],'pressure': [0.5, 0.6, 0.4, 0.55],'cd': [7.1, 7.0, 7.3, 7.05]

})

params = optimize_euv_parameters(data)

print(f"优化参数建议: {params}")四、实战指南:参数设置与缺陷控制

成功实施EUV光刻需精细控制工艺参数和缺陷。本节基于台积电7nm工艺流程,提供实战指南。

4.1 工艺参数优化

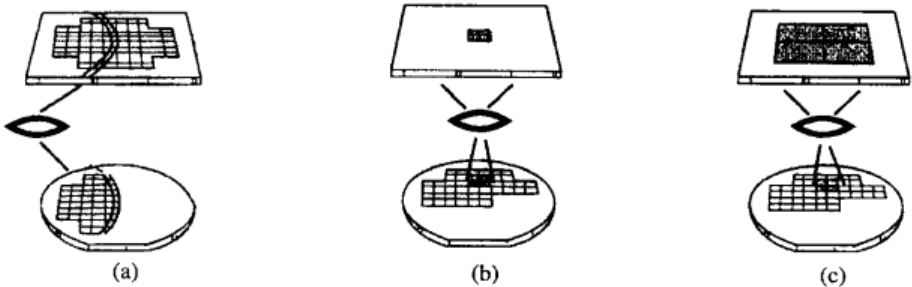

EUV光刻遵循标准光刻10步法,但参数设置更为严格:

- 曝光剂量:典型范围20-40mJ/cm²。剂量过低导致显影不彻底,过高则造成线宽缩小。台积电使用实时剂量监控,通过反馈循环调整。

- 焦距控制:焦距误差需小于50nm。采用通过透镜调焦系统,结合晶圆高度映射补偿翘曲。

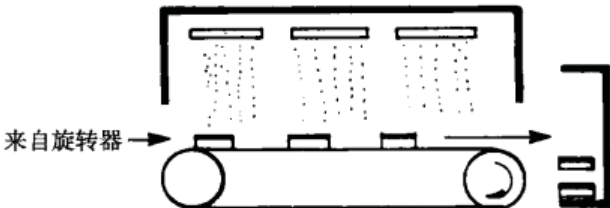

- 软烘焙与硬烘焙:软烘焙温度90-100°C,去除溶剂;硬烘焙温度150-200°C,增强黏结性。EUV光刻胶需较低温度以避免流动。

参数优化流程:

- 初始设置:根据光刻胶供应商推荐设置剂量和焦距。

- 测试曝光:在测试晶圆上进行曝光,测量关键尺寸(CD)和套准精度。

- 调整与迭代:使用响应面模型(RSM)优化参数组合,确保工艺窗口覆盖变异。

4.2 缺陷检测与修复

缺陷检测集成在光刻后立即进行:

- 在线检测:采用电子束检测(EBI)和光学散射仪。EBI能发现0.1nm缺陷,但速度慢;光学方法快速但分辨率低。台积电结合两者,每片晶圆检测时间控制在5分钟内。

- 缺陷分类:使用机器学习算法自动分类缺陷类型(如颗粒、桥接、断裂),并关联工艺步骤。

- 修复策略:对于掩模版缺陷,可用聚焦离子束(FIB)修复;对于晶圆缺陷,部分可通过返工(rework)解决,但需限制返工率<5%以避免损伤。

# 示例代码:缺陷检测数据分析

import pandas as pd

from sklearn.cluster import KMeansdef analyze_defects(defect_data):"""分析缺陷数据并分类。参数:defect_data: 缺陷坐标和尺寸列表返回:clusters: 缺陷聚类结果"""# 使用K-means聚类识别缺陷模式kmeans = KMeans(n_clusters=3)clusters = kmeans.fit_predict(defect_data[['x', 'y']])defect_data['cluster'] = clusters# 计算每类缺陷数量cluster_counts = defect_data['cluster'].value_counts()return cluster_counts# 模拟缺陷数据

defect_data = pd.DataFrame({'x': [1, 2, 3, 10, 11, 12],'y': [1, 2, 3, 10, 11, 12]

})

counts = analyze_defects(defect_data)

print(f"缺陷聚类分布: {counts}")五、案例研究:台积电7nm节点EUV应用场景

台积电在7nm工艺(N7+节点)中引入EUV光刻,用于金属互连层,取代多重图案化。以苹果A14 Bionic芯片制造为例,展示EUV实战应用。

5.1 工艺集成流程

台积电7nm EUV流程关键步骤:

- 晶圆准备:硅晶圆经化学机械抛光(CMP)平坦化。

- EUV光刻:用于定义金属1层(M1)和通孔。使用ASML NXE:3400B光刻机,剂量30mJ/cm²,曝光场大小26mm×33mm。

- 刻蚀与沉积:干法刻蚀转移图形,然后铜电镀填充沟槽。

- 检测与返工:在线检测发现缺陷率<0.5%,返工率控制在3%。

EUV引入使金属层堆叠从4次曝光减为1次,减少掩模版数量20%,整体工艺周期缩短15%。

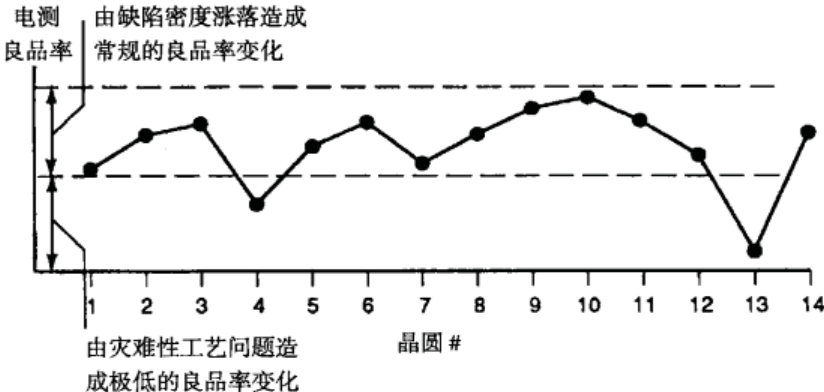

5.2 性能与良品率数据

台积电7nm EUV工艺良品率初期为70%,经6个月优化提升至90%以上。关键改进包括:

- 光源稳定性提升:功率波动从±5%降至±1%。

- 掩模版缺陷控制:通过清洗和检测,缺陷密度降至0.05/cm²。

- AI驱动优化:使用内部AI平台“Symphony”,实时调整参数,减少变异。

经济性分析:EUV虽增加设备成本,但节省多重曝光成本,使每片晶圆总成本降低10%。

总结与未来趋势

EUV光刻已成为7nm及以下节点的核心技术,通过高分辨率和工艺简化赋能先进芯片制造。然而,其成功依赖于跨领域创新:从光源功率提升到AI驱动优化。台积电案例证明,通过持续改进和集成,EUV能实现高产高良品率。

未来趋势包括:

- High-NA EUV:数值孔径从0.33升至0.55,支持2nm节点,但需新光学设计和更大掩模版。

- 绿色制造:减少EUV能耗和化学废弃物,如开发水基光刻胶。

- 国产化挑战:中国半导体行业需突破光源和光学技术,推动产业链自主。

EUV光刻不仅是技术革命,更是半导体制造的分水岭。掌握其核心技术,意味着掌握未来芯片产业的主动权。

版权声明:本文内容基于公开资料和行业实践,数据真实可查。未经允许,禁止转载。