数电基础:触发器

目录

一、SR触发器

(1)为什么需要有触发器?

(2)SR触发器的原理

(3)SR触发器存在的问题

二、水平触发的D触发器

(1)D触发器的原理

(2)封装图与抗干扰弱的问题

三、上升沿触发的D触发器

四、脉冲触发的SR触发器

五、脉冲触发的JK触发器

(1)JK触发器的原理图与工作原理

数字电路的世界里,‘记忆’与‘时序控制’是永恒的命题。从 SR 锁存器的‘敏感易误’,到触发器家族的‘精准可控’,每一次电路演进都在解决‘如何稳定存储、如何抗干扰’的核心难题。本文将带你走完‘SR 触发器→D 触发器→边沿 D 触发器→JK 触发器’的完整进化链,拆解从‘电平触发’到‘边沿触发’的设计智慧,剖析从‘约束重重’到‘功能完备’的逻辑闭环,最终让你明白:这些触发器不是孤立的电路模块,而是数字系统‘时序心脏’的一个个精密零件。

一、SR触发器

(1)为什么需要有触发器?

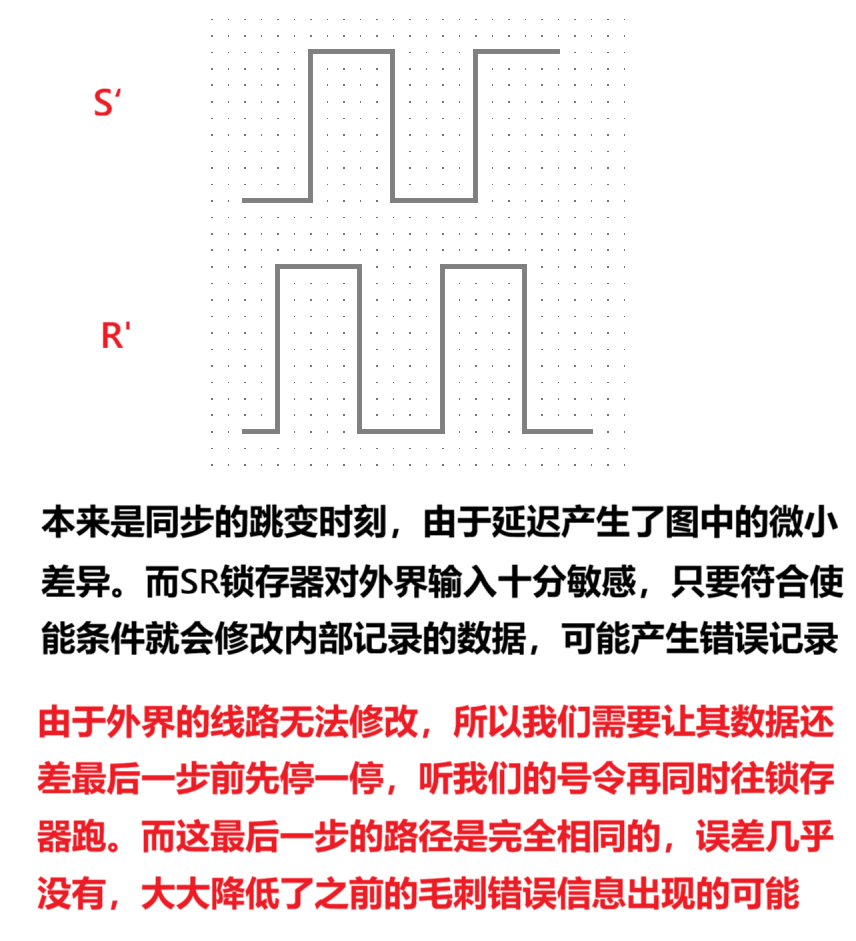

因为锁存器对外界的输入十分敏感,只要输入端S'和R'两端的电平发生了跳变就可能会改变锁存器记录的数值。但是我们无法保证电路通路中是完全没有延迟的,本来理论上同时跳变的信号,可能由于误差使得一端稍稍慢于另一端,而SR触发器这种敏感器件就会对其产生反应,可能就导致记录了错误的数据。所以我们需要有一种能力,使得信号到来时,快的信号稍稍等一等慢的信号,然后同时进入锁存器。

(2)SR触发器的原理

所谓触发器,就是在锁存器的基础上,增加触发控制信号(在时序电路中我们称为时序信号CLK),使得锁存器在控制信号有效时候才能将数据锁存、或者是修改。一旦时序信号没有给他使能条件,锁存器就好像没有开机一样,不会对外界数据线有任何反应。

于是人们开始思考,什么器件可以有两种状态:一方面是正常工作时,能让信号顺利传递到后面,退化成锁存器;另一方面又能通过这个器件来控制锁存器是否工作,对外界产生响应。

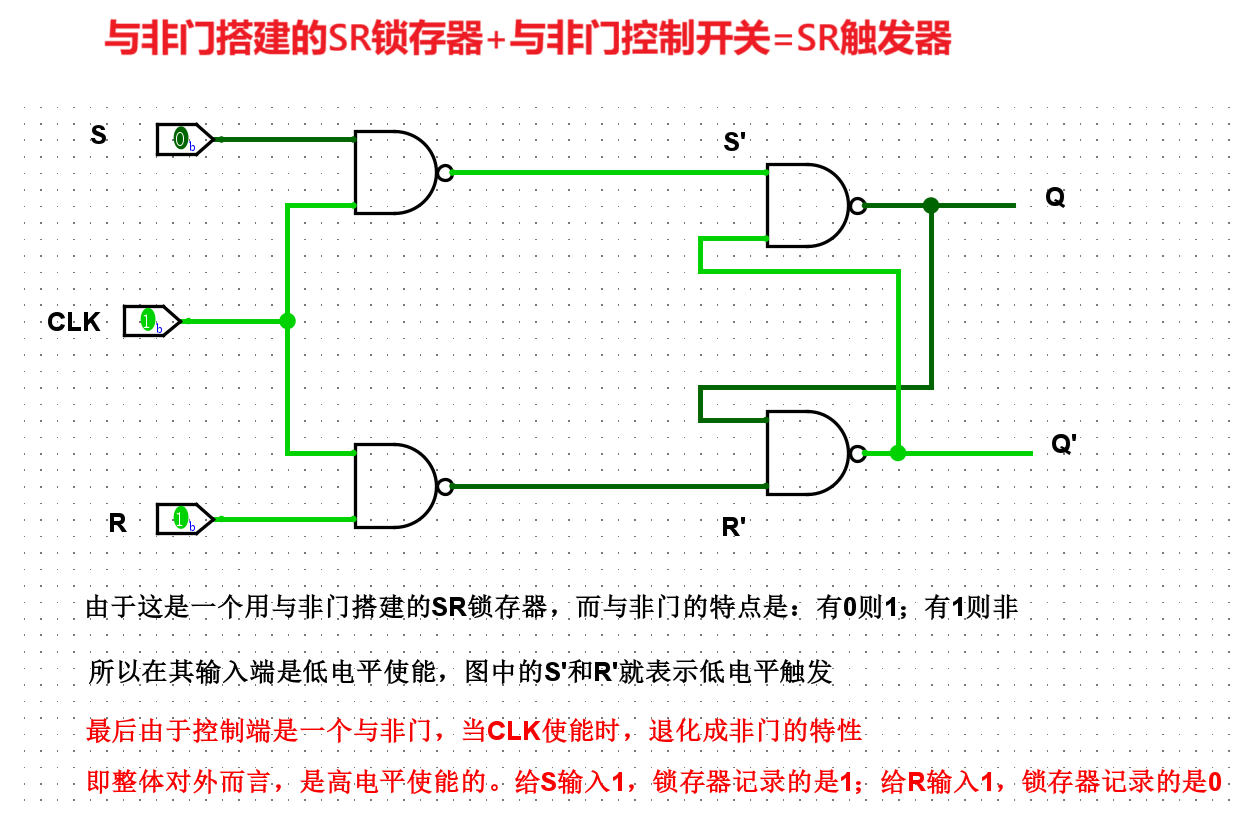

诶,这个描述是不是特别像三态输出门用与非门、或非门充当控制器件啊?于是人们尝试用与非门来做控制器件。得到了下图的电路结构:

分析一下:

(1)当CLK=0时,由与非门开关特性,对外永远输出1。而这个输出的1对于与非门做的SR锁存器是保持信号。所以当CLK=0低电平时,内部的锁存器不响应外界输入的变化,呈现关断的状态。

(2)当CLK=1时,由于与非门有1则非的特性,外界通过S、R两输入端进来的数据能顺利传递到SR锁存器的输入端,此时就完全退化成基本的锁存器,和上一篇文章类似。所以当CLK=1时,SR触发器退化成SR锁存器,正常工作。

(3)SR触发器存在的问题

(1)SR锁存器由于本质还是SR寄存器没有改变,所以他对于输入有着较为严格的要求:不允许同时输入高电平、也不允许同时从高电平跳变成低电平。

如果是简单的器件,还能人为控制一下,但是一旦系统变得庞大,我们无暇再顾及。所以最好把这个问题一次性解决掉,使其输入任何电平都至少不会错误。我们说他会有约束输入的问题。

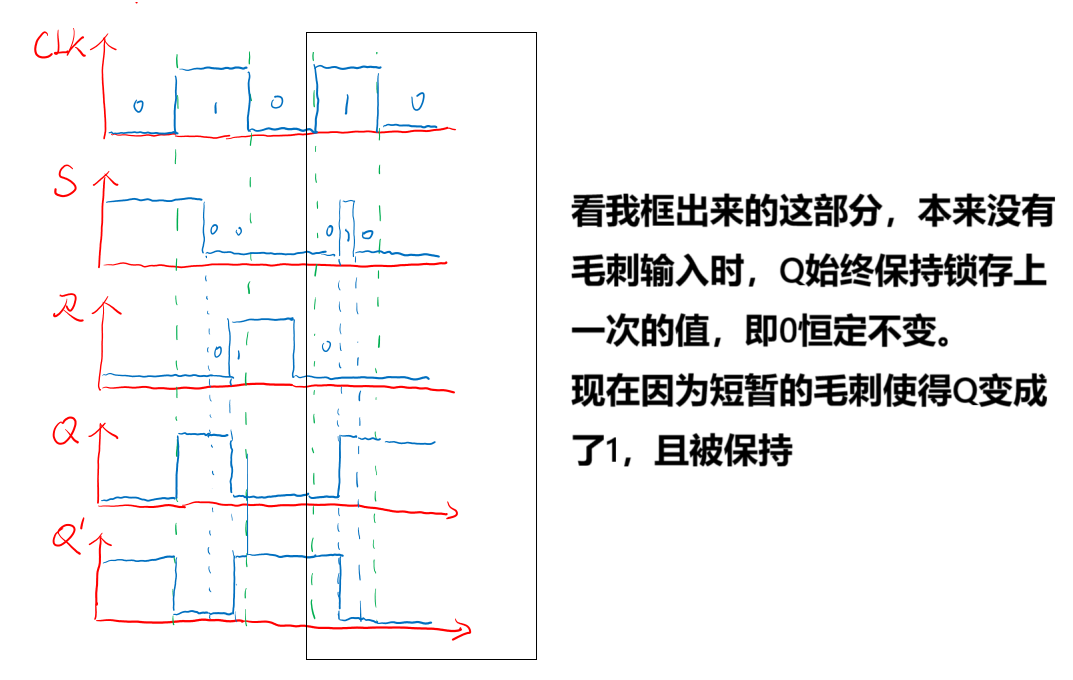

(2)SR锁存器是对输入信号敏感的,只要输入端任意时刻发生改变(比如外界干扰产生微小毛刺),就会影响锁存的数值。这个我们称为抗干扰能力差。

为了解决这些问题,才逐渐发明了后续的电路。

二、水平触发的D触发器

(1)D触发器的原理

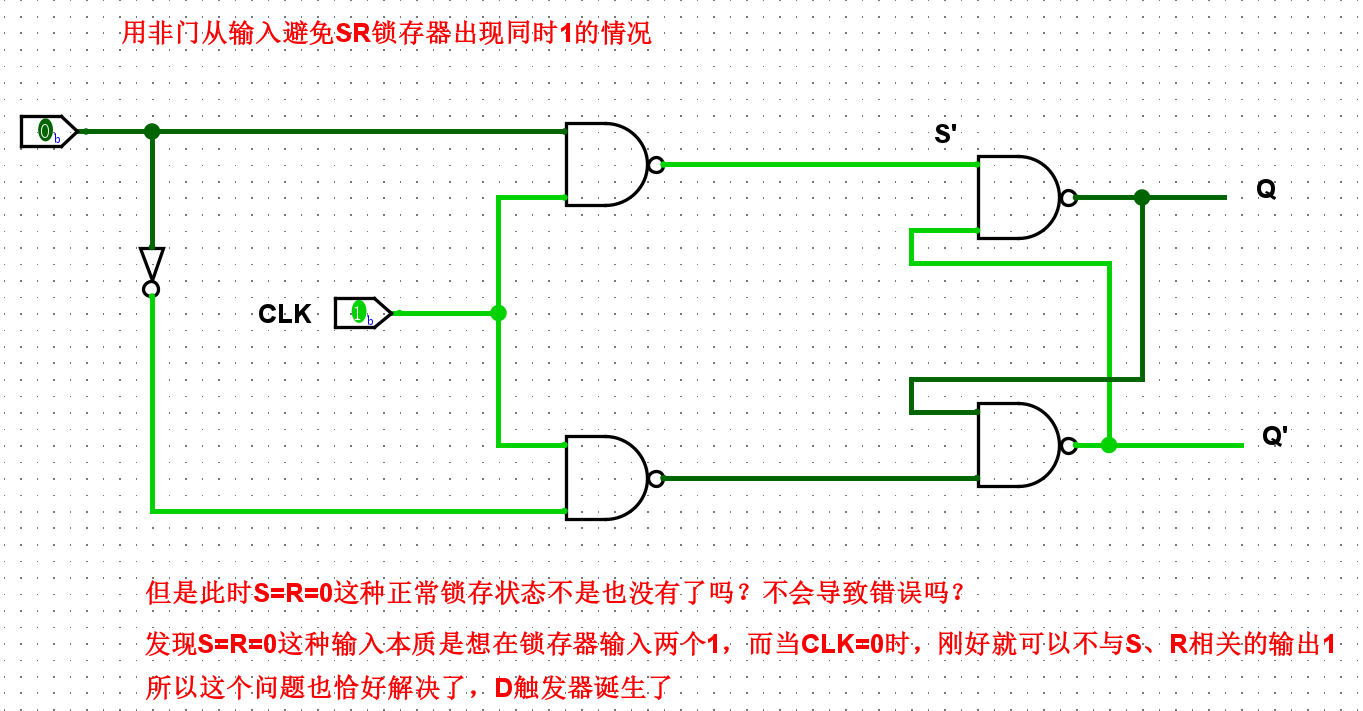

首先我们来解决问题1,即约束输入的麻烦。

我们仅仅需要将输入端用一个非门连接,就能保证输入的S和R永远是相反的值,从根本上避免了约束条件。从下图可以发现所谓的D触发器,特别简单。与SR触发器仅仅多了一个非门。

分析一下:

(1)当CLK=1时,与非门控制器退化成非门。所以D触发器退化成S、R两端不可能相同的SR触发器。假设D接低电平0,则S'=1,锁存器记录0值;当D接高电平,锁存器记录1值。

总的来说D触发器和D端的输入是完全相同、跟随的,输入多少就记录多少。

(2)当CLK=0时,与非门控制器恒定输出1,传递到SR锁存器时呈现保持态,也是正常工作的。

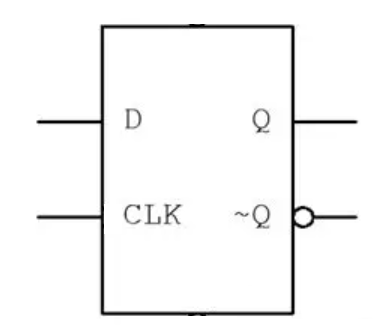

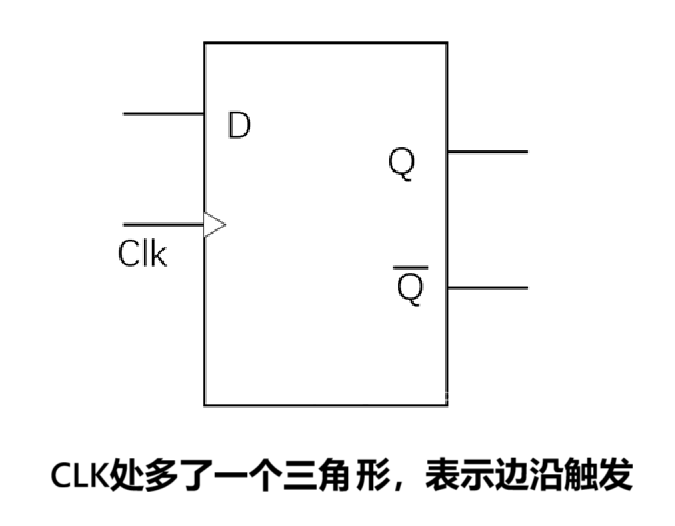

(2)封装图与抗干扰弱的问题

人们对于D触发器封装成一个模块,方便后续使用。

但是D触发器只解决了约束条件。本质上仍然是SR触发器的内核,并没有解决毛刺问题。

我们先来思考一下毛刺是为什么会导致错误信息被锁存。(这里的毛刺并不是从输入端来的,输入端是正常的,而是在被D触发器抓取时受到了外界电磁波干扰抓取到了错误信息)

所以我们得出一个结论:锁存器关心的时间段越多,抓取毛刺的可能性就更大。如果我们能将锁存器抓取数据的时间段缩短,则能大大降低毛刺的概率。最极限的情况是将锁存器抓取数据的时间段变成一个点----上升沿、下降沿捕获数据。即边沿触发的D触发器

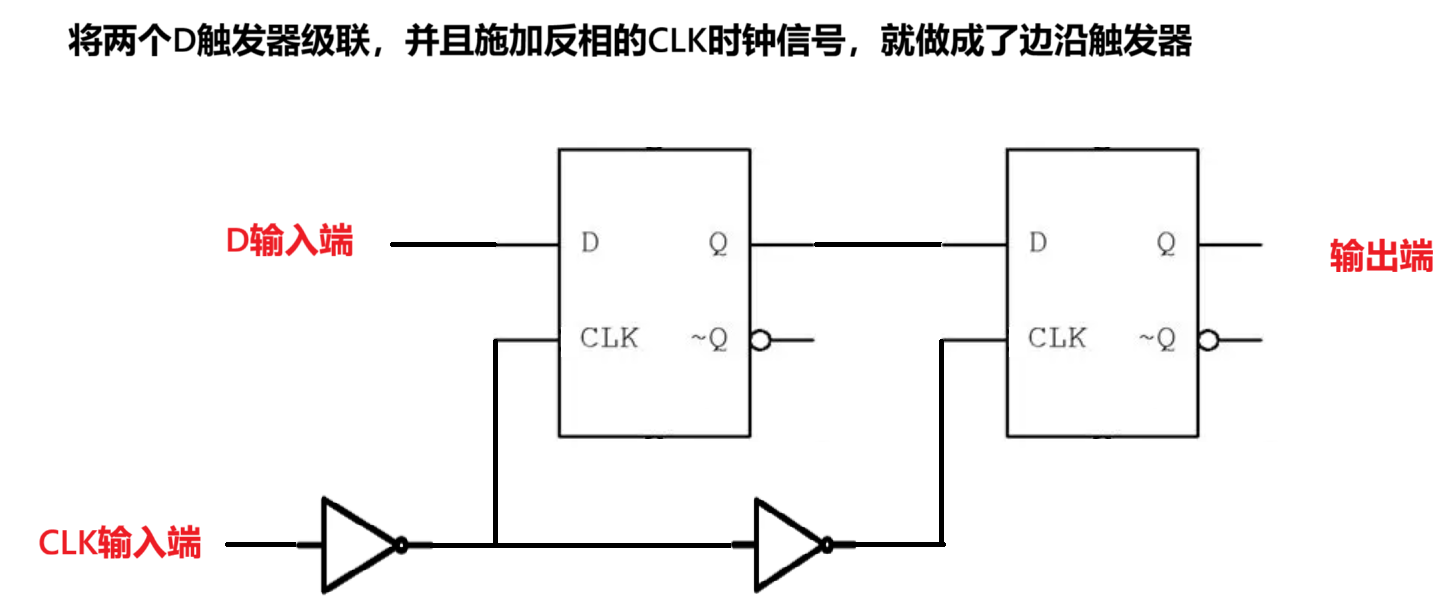

三、上升沿触发的D触发器

分析一下工作原理:

(1)当CLK=0时,经过第一个反相器,使得FF1使能,正常抓取D输入端的信号,并且锁存在第一块锁存器内部。而FF2由于没有使能,无法抓取FF1输出的电平信号。

(2)当CLK=0->CLK=1这个瞬间,FF1使能关闭,FF2使能开启。原本保持在FF1内部的数据被FF2捕获,并且正常输出到外面。

(3)再次当CLK从1变到0时刻,FF1、FF2工作状态又相反。循环往复,

最后的结论是:FF1在上升沿的前一瞬间抓取外部数据线的电平信号并且锁存;FF2在上升沿抓取FF1输出的信号并且输出。

但是仔细观察,似乎第一级在抓取输入信号时,仍然是一个片段,在CLK在=0一定是一个时间片,而不是一瞬间,所以在这个过程中会持续抓取外部输入,如果有毛刺同样可能会修改锁存器记录的值,只要在最后CLK切换前毛刺消失,恢复成原本的电平即不会影响输入的准确性。

而D2触发器会在CLK=1这个片段采集D1输出的数据,由于D1此时使能已经关闭,呈现锁存输出状态,所以是稳定的。

整个过程中相当于D1承担了“容错采样”的角色,而D2是精准采样。虽然我们说这种电路设计是在边沿采集数据,但本质仍然是在一个时间段采集数据。这一点无法改变。

最后补充一点,只要是D触发器,无论是水平触发还是边沿触发,其特性方程都为:Q*=D。

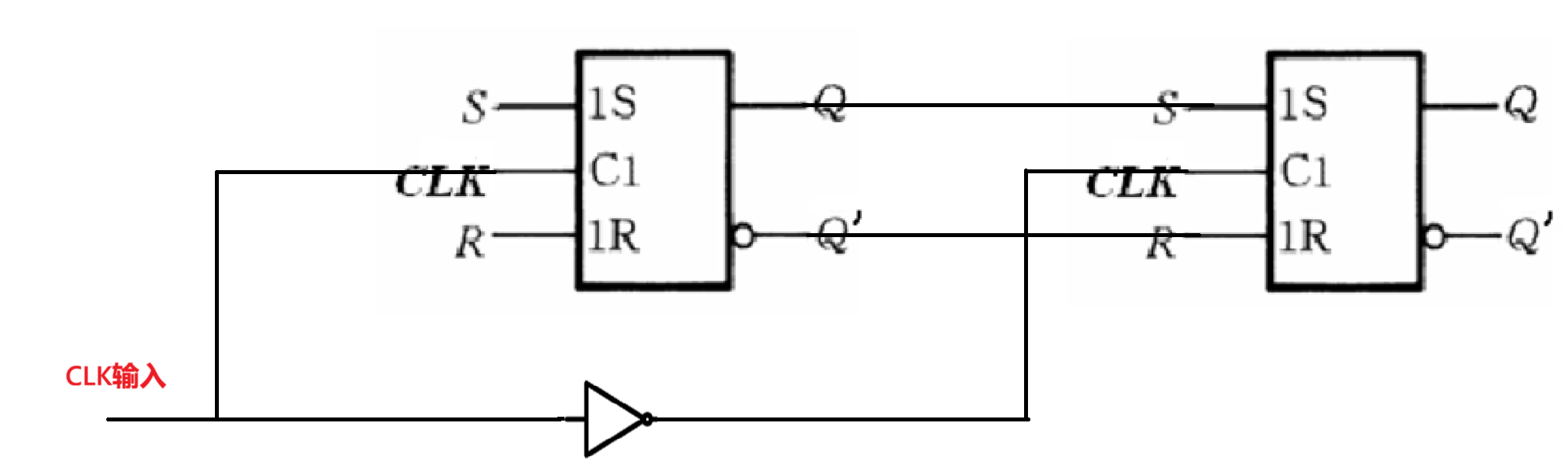

四、脉冲触发的SR触发器

如果将上升沿触发的D触发器的两个非门去掉,则退化成了两个SR触发器。用他们做级联就得到了脉冲触发的SR触发器。

工作原理:

几乎与D触发器相同。只不过在使能期间的扰动会直接干扰主触发器的锁存结果。

(1)当CLK=1时,使得FF1使能,正常抓取D输入端的信号,并且锁存在第一块锁存器内部。而FF2由于没有使能,无法抓取FF1输出的电平信号。

(2)当CLK=1->CLK=0这个下降沿瞬间,FF1使能关闭,FF2使能开启。原本保持在FF1内部的数据被FF2捕获,并且正常输出到外面。

(3)再次当CLK从1变到0时刻,FF1、FF2工作状态又相反。循环往复。

但是由于S、R两端没有直接连在一起,所以是独立的输入,任何一方产生干扰信号都会影响锁存结果。而D触发器由于通过非门将两输入端连接到一起,即使中间发生了改变,只要最后毛刺消失了,就会恢复到正常信息状态。

简单来说,SR脉冲触发器抗干扰能力不如水平触发的D触发器,因为你无法保证S、R受到同步反相的干扰信号。

比如在CLK=1,FF1使能期间,S、R正常都是0,属于保持状态;突然S由于外界干扰产生了一个1电平波动,于是主触发器将直接锁存1。而D触发器由于外界干扰只在一根D线上体现,所以SR同步反相变化,最后D恢复时,SR记录的就是正确的数值。

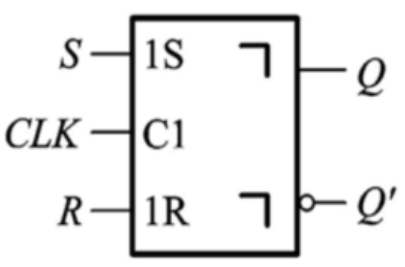

人们在SR触发器的基础上,增加了两个拐角符号,表示该触发器是SR类型的脉冲触发器。而拐角的不同则表示他在什么时候会采样,比如下图就是正脉冲触发:在高电平和下降沿瞬间采样,所以我们需要明白他在高电平期间抗干扰能力弱的特点。

五、脉冲触发的JK触发器

在SR制作成的脉冲触发器中,我们发现他有两大问题:有输入约束条件,可能影响复杂电路设计的便捷;在CLK使能期间,R、S两端不是同步反相变化的,极易受到干扰信号的影响锁存错误的值。

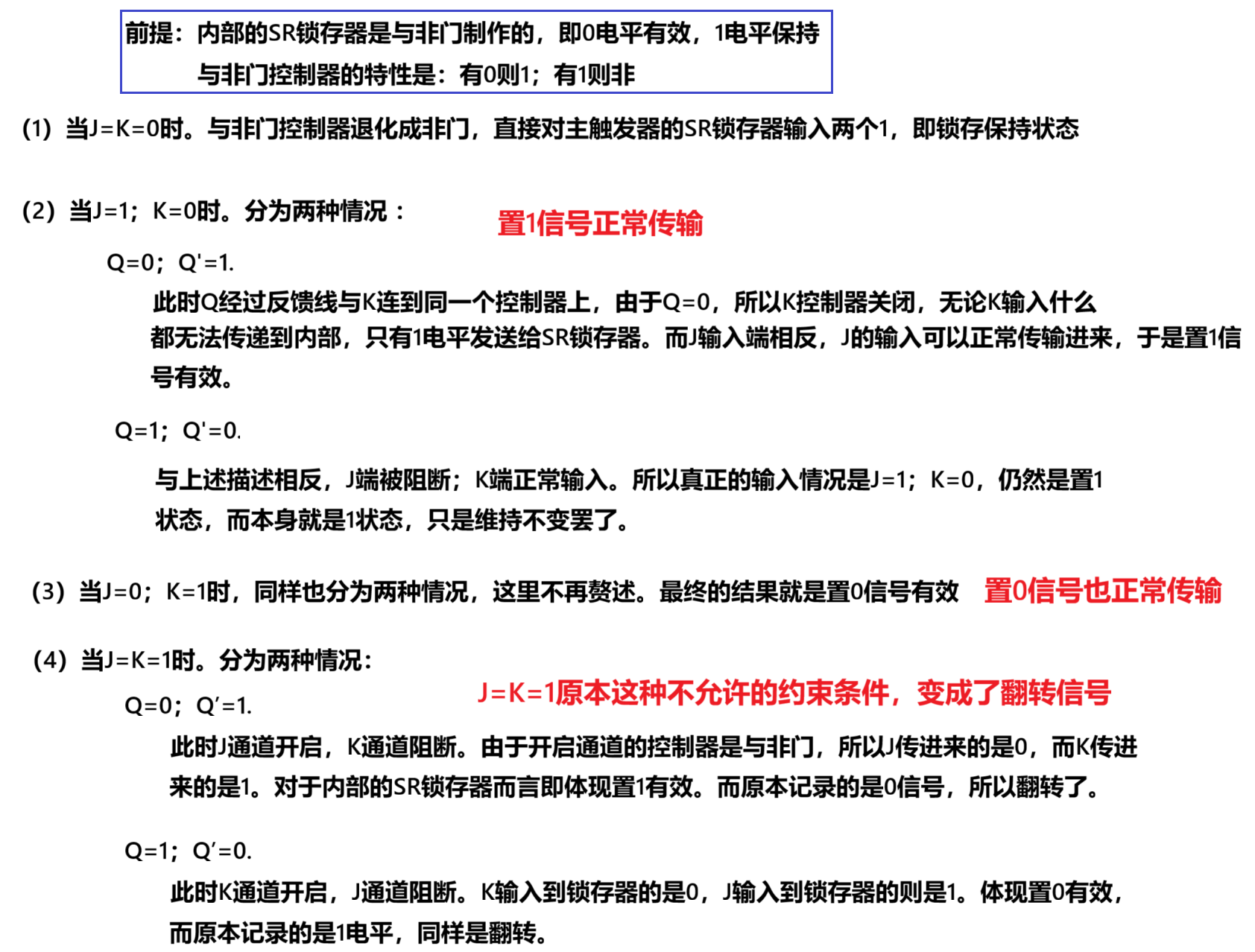

首先来看看JK触发器如何解决约束条件的问题。

(1)JK触发器的原理图与工作原理

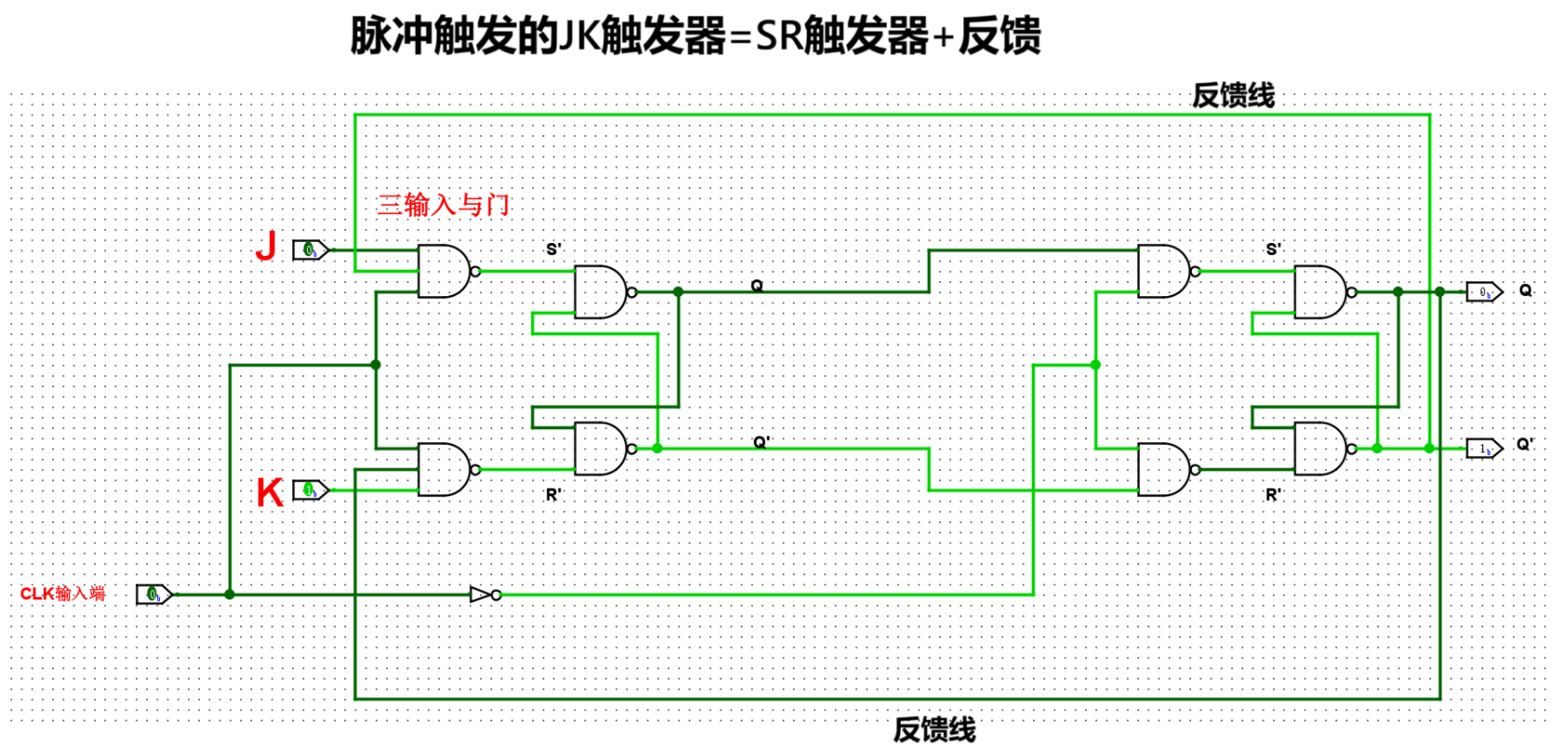

这是我利用logisim画出的原理图,可以帮助我们从更底层的角度理解。

分析CLK=1主触发器使能条件下,无毛刺的工作原理:

简单来说就是置位信号仍然延续SR的规则,但是原本SR锁存器所不允许的S=R=1情况变成了电平翻转。在无毛刺情况下,特性方程可以写成Q*=JQ'+K'Q。这个不需要记忆,但是有时候可能会将J、K两端短接,形成T触发器,直接套用特性方程将很容易判断出T触发器的特性方程:Q*=TQ'+T'Q,呈现异或的形式。如果不记忆的话也要临场会分析。

不过需要注意的是:这个总结是在CLK=1期间,J、K两端无任何毛刺情况下才成立,如果任意一方出现了毛刺,则需要具体到器件原理图分析,上述的规律不再适用。

同时,经过上面的分析可以发现JK触发器和SR触发器有一个共同的缺点:抗干扰能力比D触发器差很多。如果用在精确仪器中,最好选择D触发器。