【FPGA】设计流程——板级验证

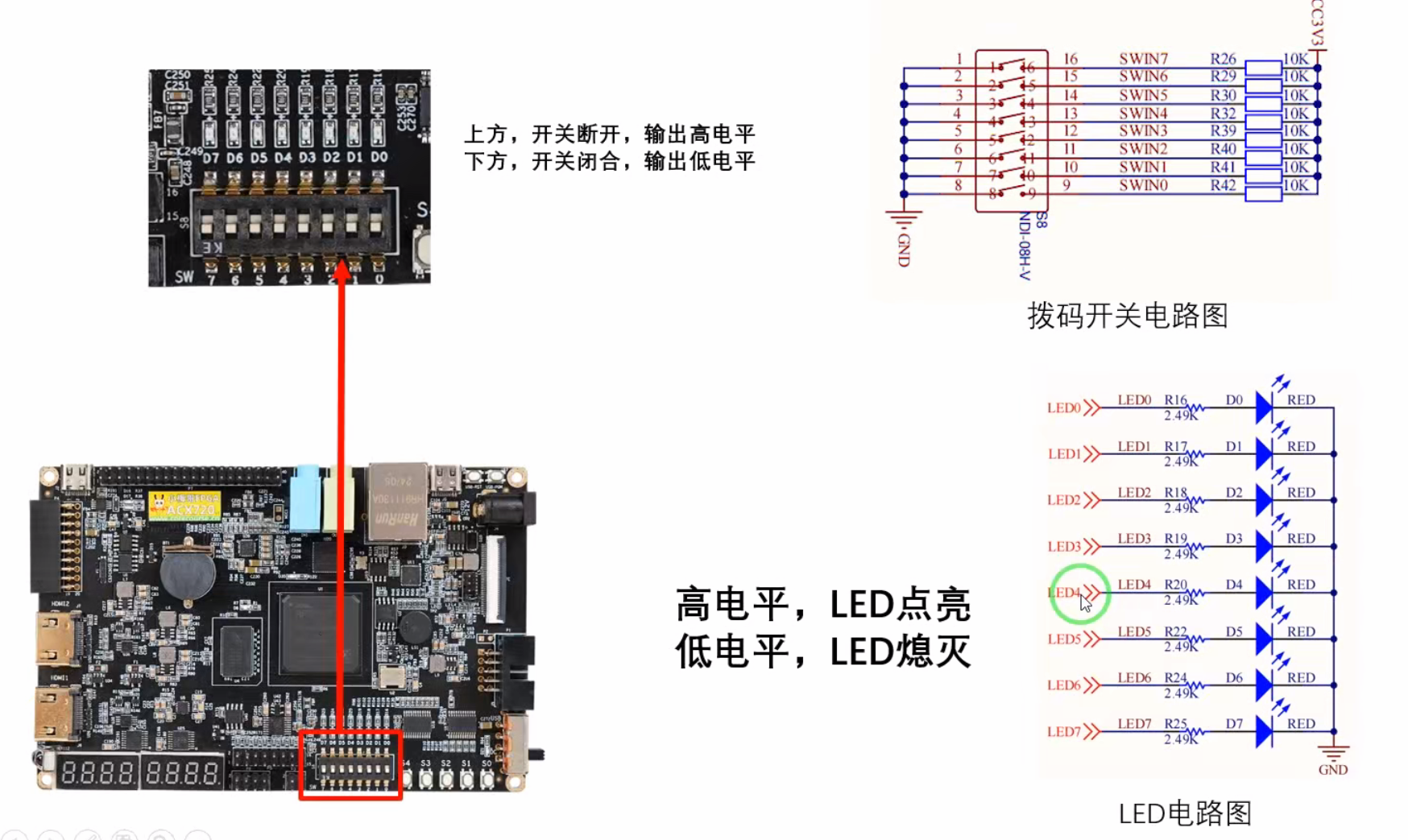

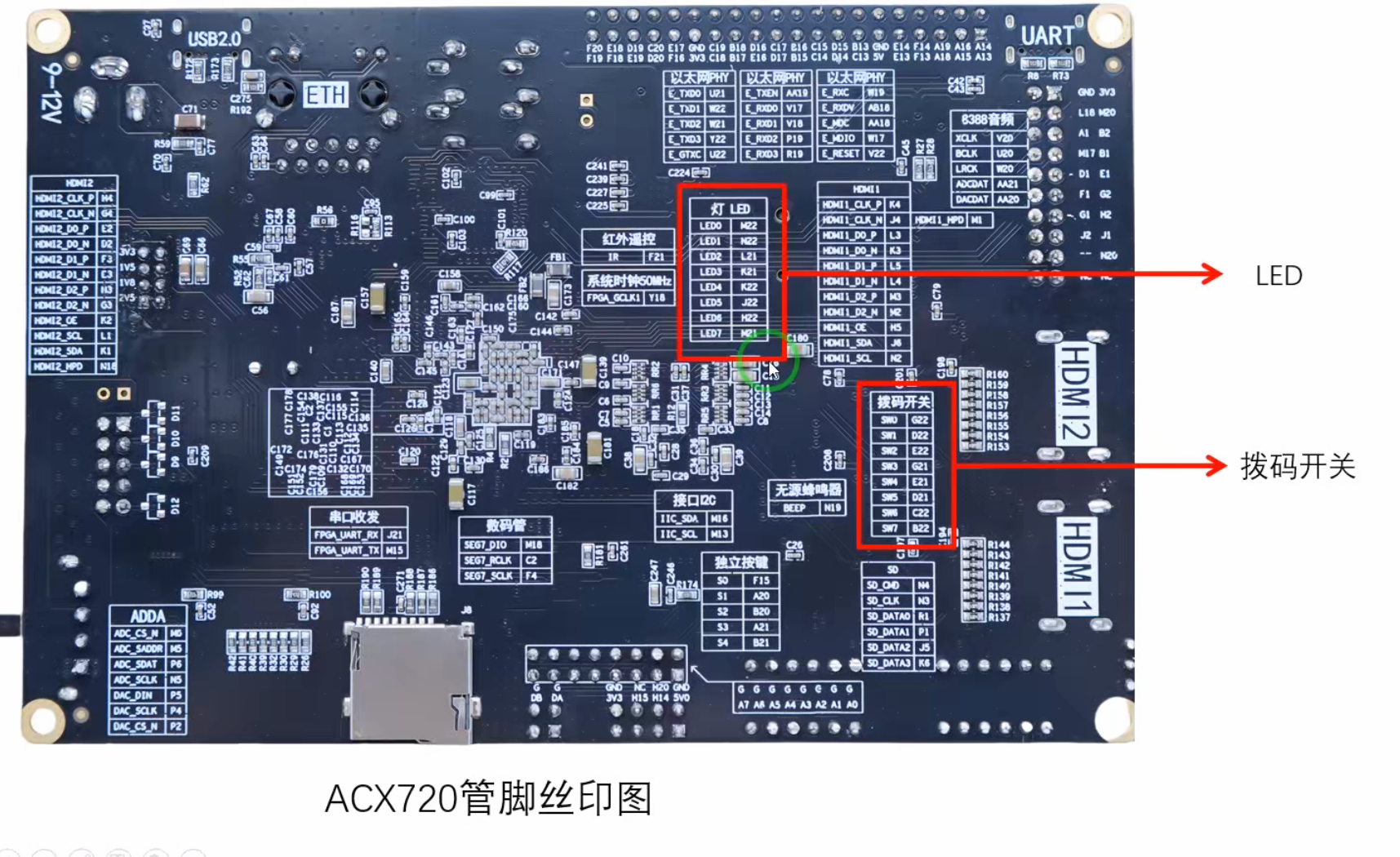

一、开发板介绍

拨码开关上方,开关断开,输出高电平

拨码开关下方,开关闭合,输出低电平

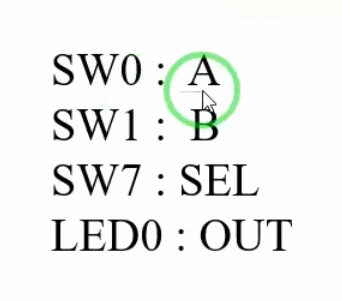

将拨码开关与端口对应

确定好物理硬件和端口的对应关系后,用vivado软件进行关联,称为管脚约束

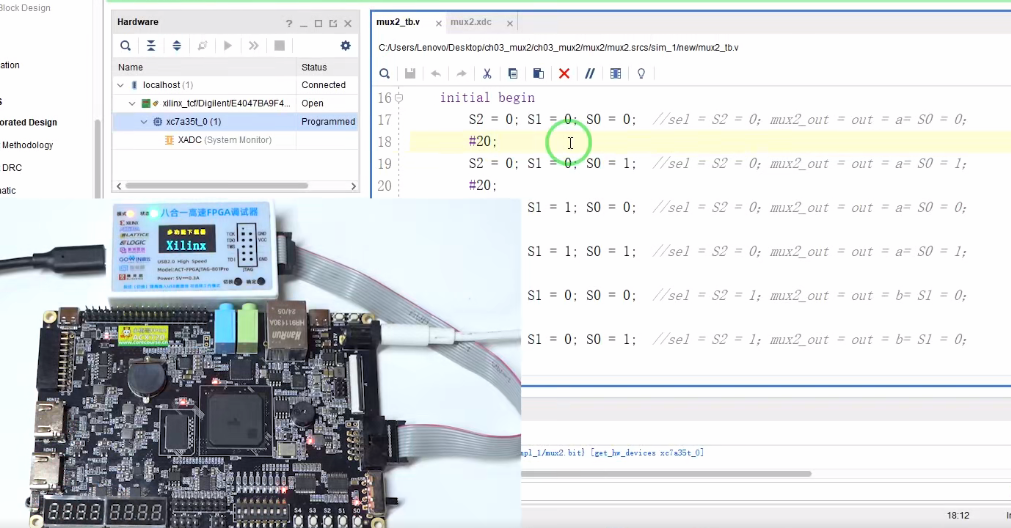

二、软件操作

点击左侧open。。。,点击OK

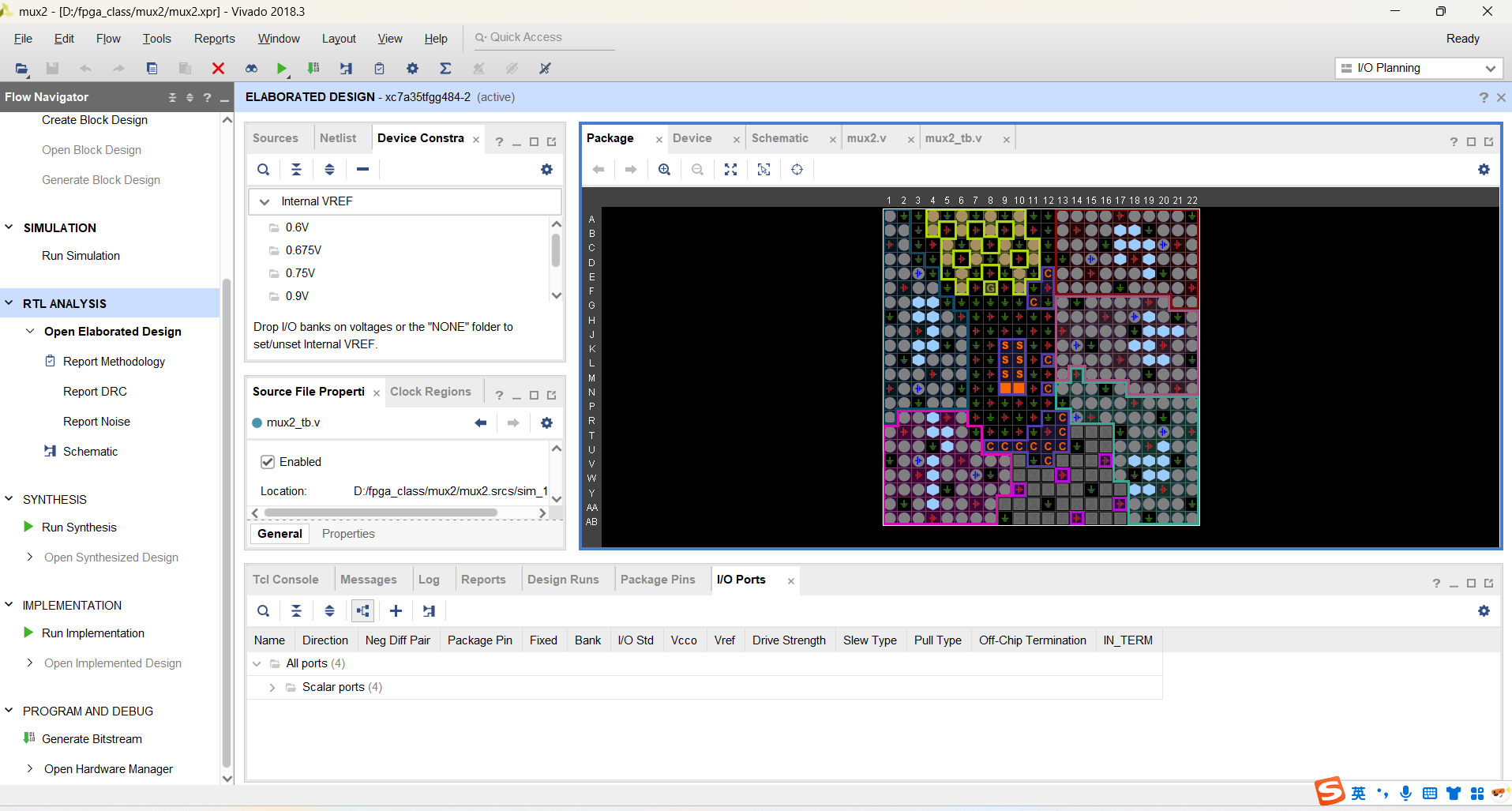

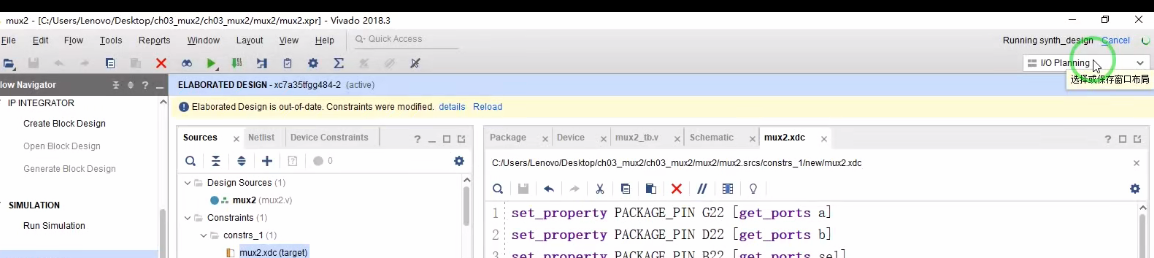

默认是IO planing

默认是IO planing

如果不是需要自己选择

软件就会切到管脚分配的页面

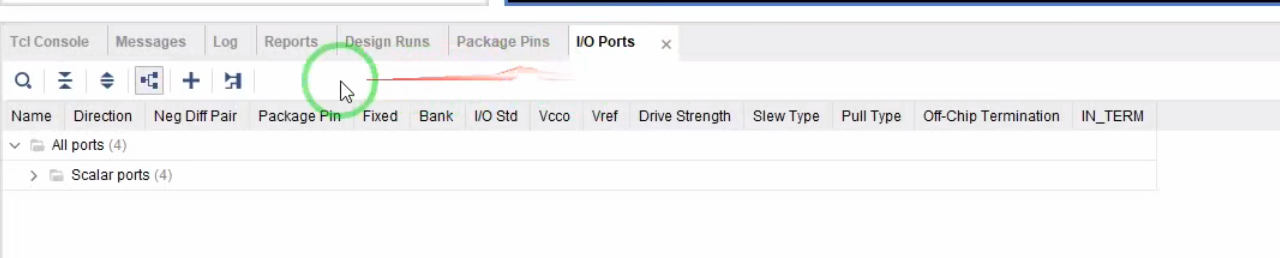

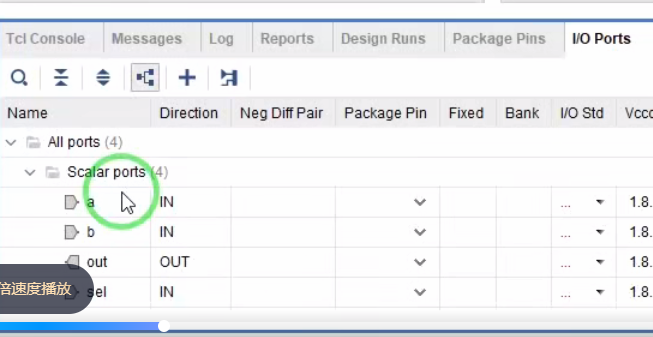

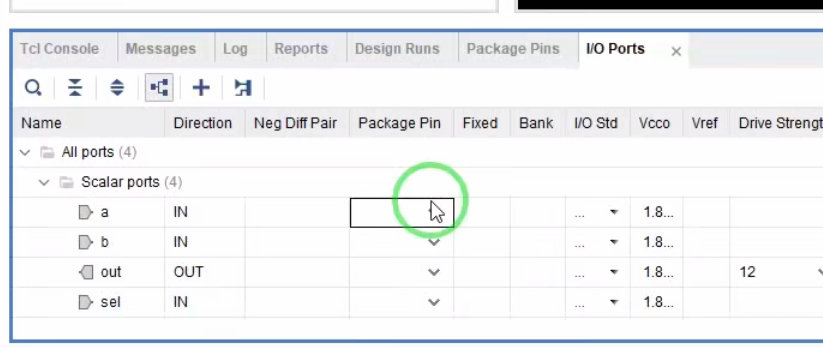

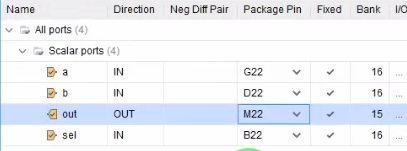

在IO Ports页面可以进行管脚绑定

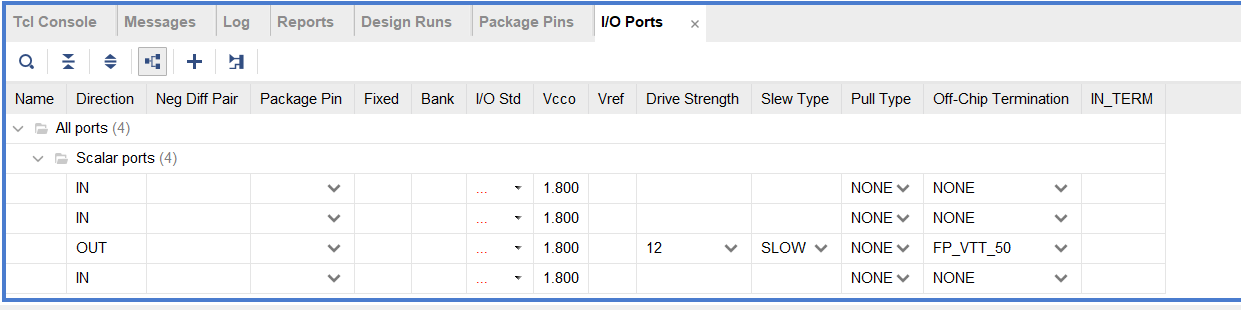

展开可以看到一共有四个端口

右拉name列可以展开名字

在package PIN定义管脚

可以通过开发板的原理图找到对应引脚,也可以通过开发板后面的丝印查找

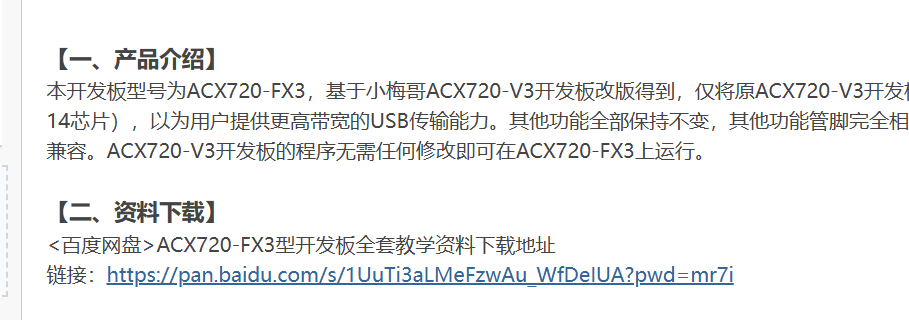

也可进入这个网站,点击红色条幅

找到ACX720链接进入

可以进行相关资料的下载

A盘的04文件夹就是引脚功能信息

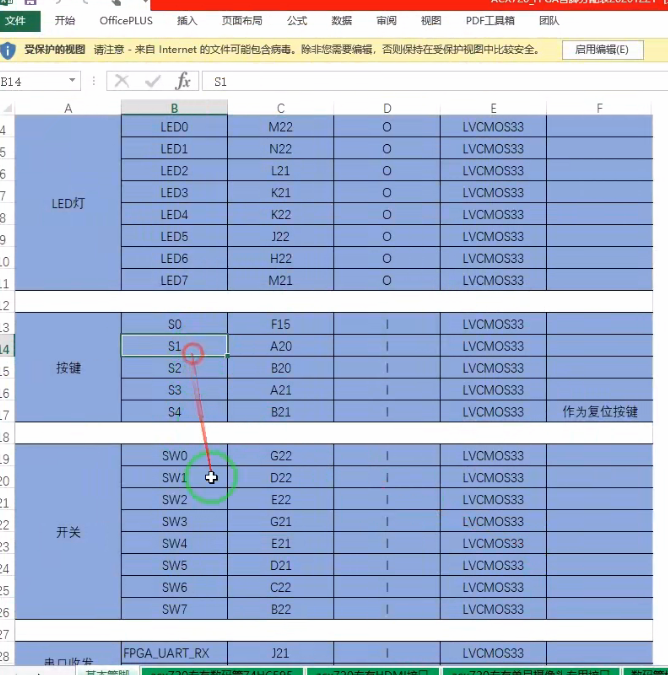

这个表格就会用引脚功能

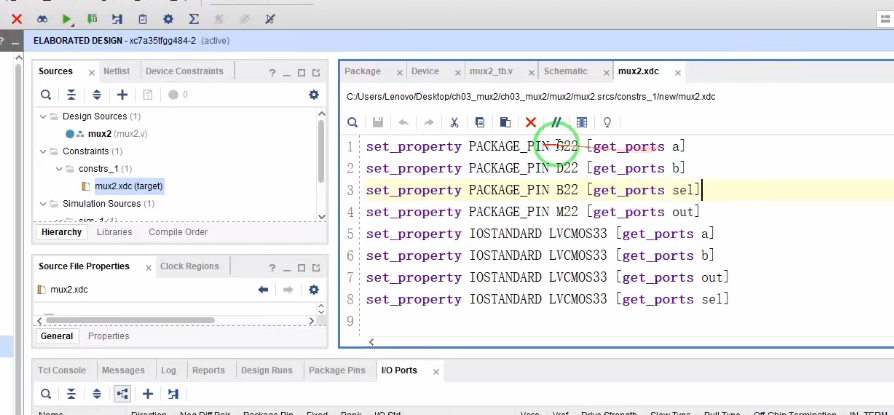

进行管脚分配

A对应的是SW0--G22

B对应的是SW1--D22

SEL对应的是SW7--B22

out对应的是D0--M22

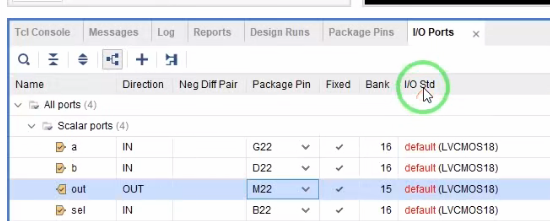

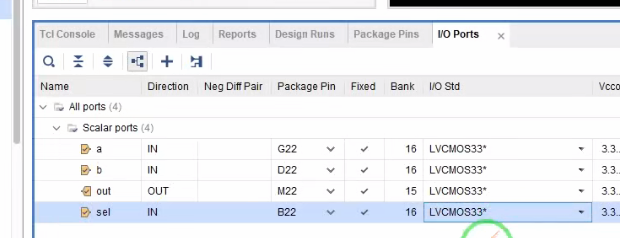

修改管脚电平IO Std

软件默认的是1.8V的LVCmos,要修改为实际的电路板上使用的3.3v

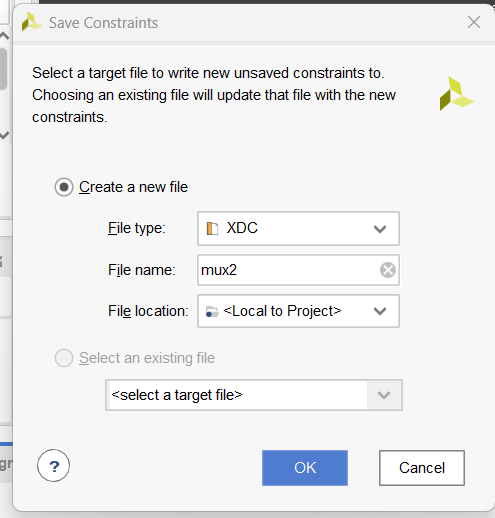

保存文件

ctrl+s

输入名称,点击OK

就会保存到这里

打开的内容是以文本形式描述他所对应的FPGA的管脚以及所使用的电平标准

这就是目前所使用的目标约束文件

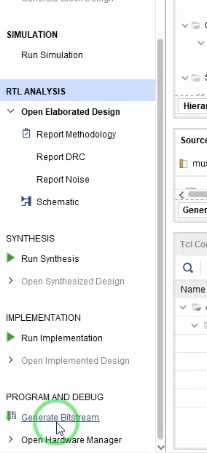

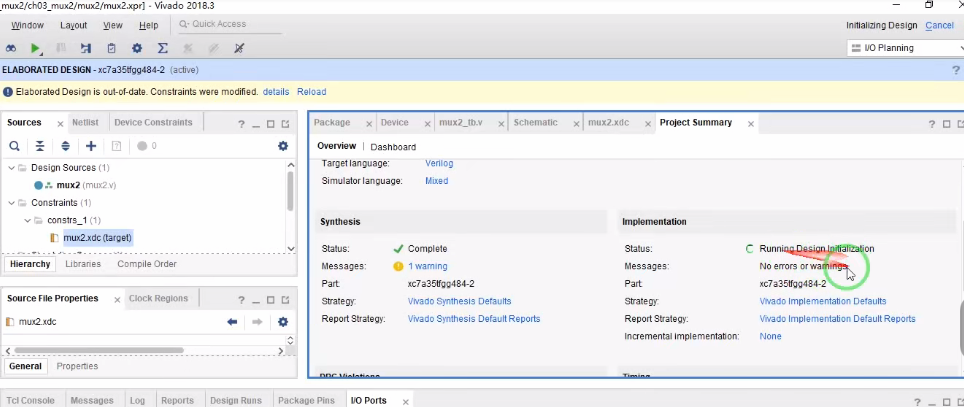

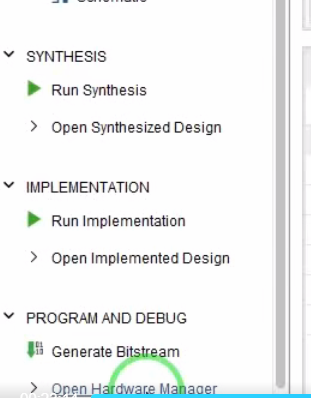

生成编程文件

点击软件generate bitstream

点击保存save,yes

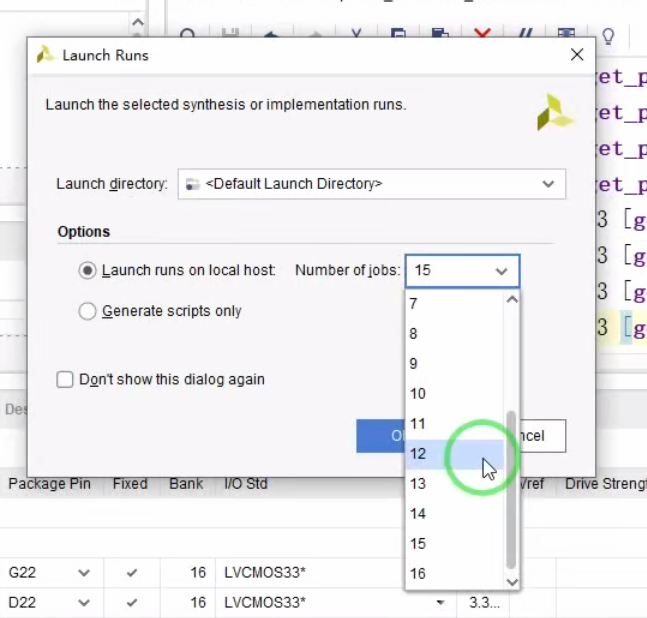

这个的选择会影响编译速度

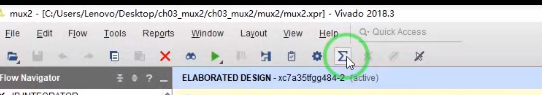

在编译过程中软件右上角会显示编译过程

想要看编译过程也可以点击这个图标

就会跳转到这个界面确定编译的具体过程

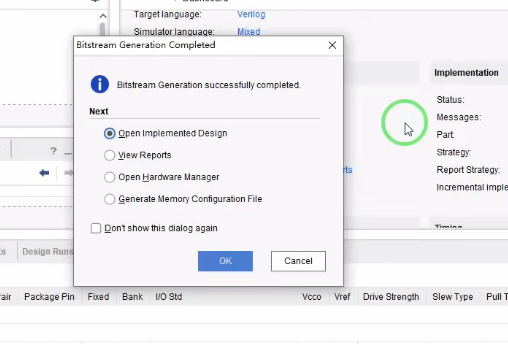

编译完成

第一个选择是打开已经实现完的设计比如看拓扑图,底层的电路图,原理图

第二个是打开设计编译报告的窗口,查看报告

第三个是打开硬件管理器,就可以连接开发板并将下载好的bit文件下载到FPGA里面去

第四个是生成配置内存文件,暂时用不上

实际上不用这些选项,点击cancel

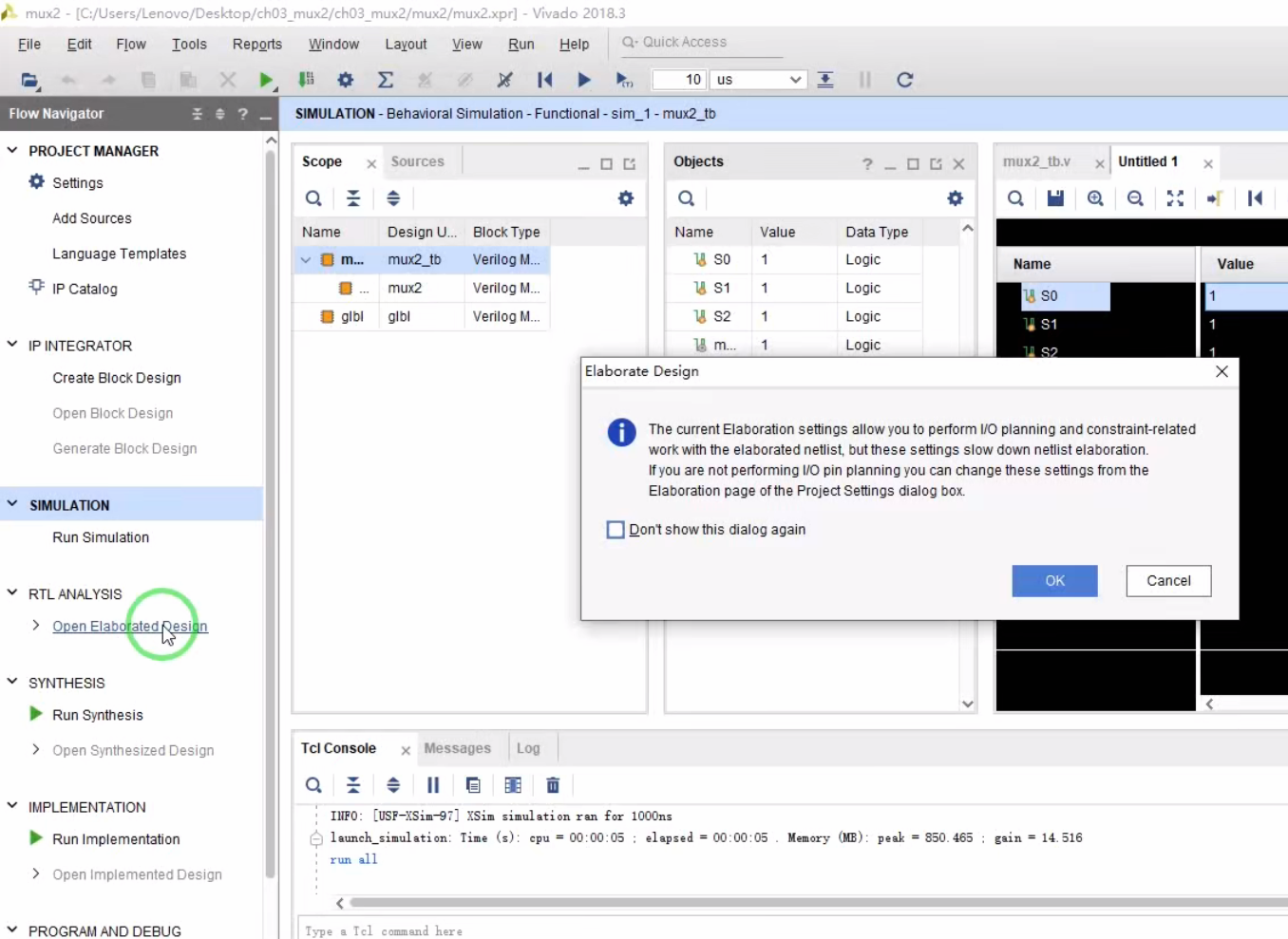

下载编程文件

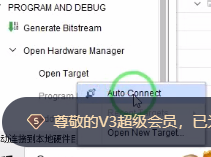

左下角点击open hardware。。。

点击auto connect

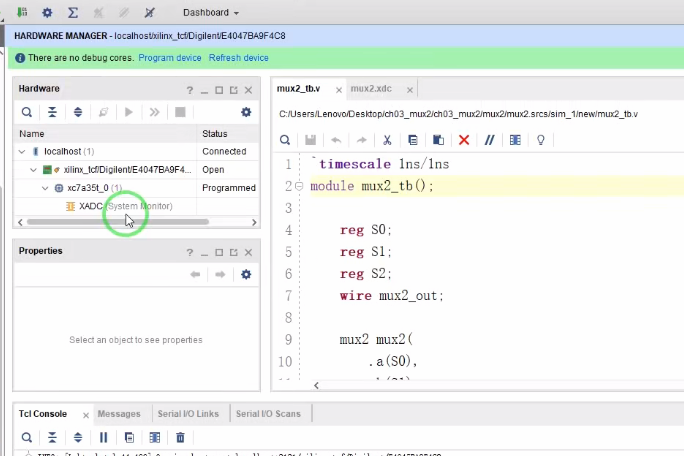

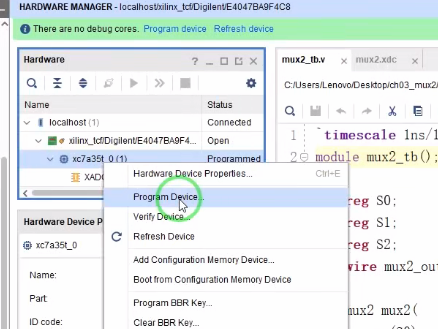

然后就进入了这个页面

检测到了xc7a35t,说明硬件已经连好了

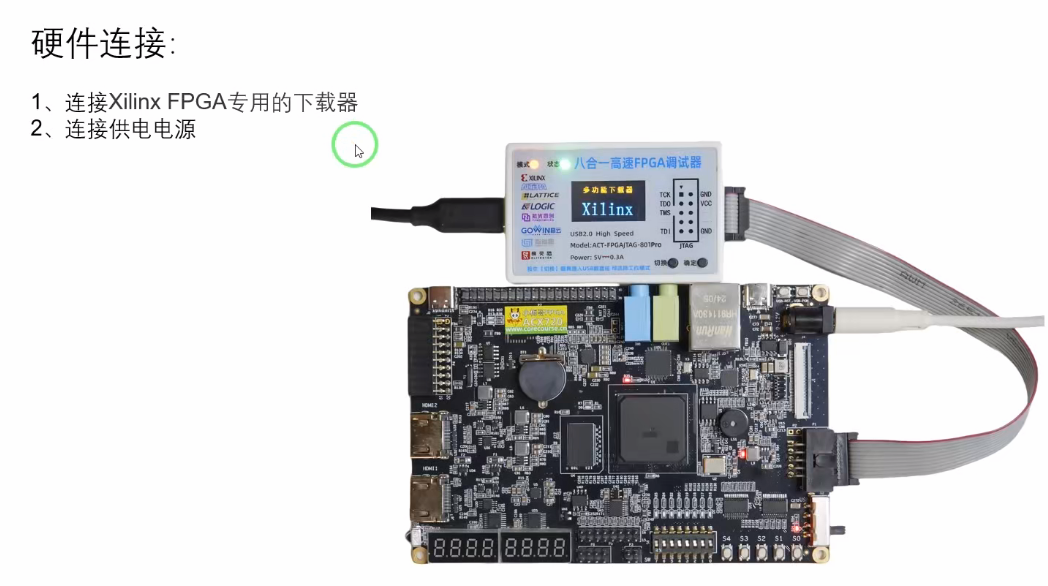

黑线链接到电脑上,经过下载器连接到电脑上

白线是给开发板供电的电源线

开关确保达到最下面,直流供电

中间是关断

上面是使用USB

第四部是确保驱动安装

找到USB serial converter的设备

没有感叹号是正常的

有问题可以去网站查找

进行编程

选中芯片右键点击program device

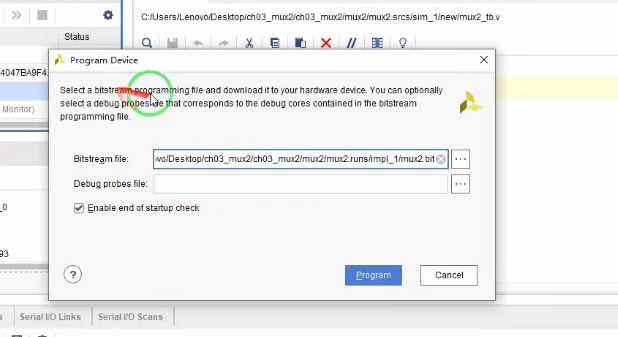

就会弹出对话框

需要留意一下这个路径,后续自己做开发需要手动寻找bit文件,因为他本身不是很好找

第二栏是空的,这个主要是有调试文件时才使用

点击program按钮

观察实验现象