STM32基本定时器

定时器简介

TIM是英文timer的缩写。

定时器最基本的功能就是定时器可以对输入的时钟进行计数,并在计数值达到设定值时触发中断。

综上所述,定时器的核心本质就是一个计数器。

STM32的定时器拥有16位计数器,这个16位计数器和预分频器,16位的自动重装寄存器共同构成了时基单元。

由于这个时基单元的计数器和自动重装寄存器都是16位的,2的16次方为65536。

所以最大定时时间 T_max = (预分频器最大值 + 1) * (计数器最大值) / 时钟频率 = 65536 * 65536 / 72,000,000 ≈ 59.65秒。

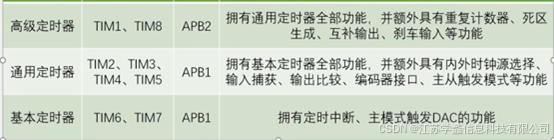

定时器类型

定时器分为基本定时器,通用定时器和高级定时器。

基本定时器的功能最少,他只有基本的定时中断和主模式触发DAC的功能。所以基本定时器还可以和DAC联合使用。

什么是框图

STM32的框图可以看作是它们的内部电路逻辑结构简化示意图。它并非展示每一个晶体管和连线的具体物理电路图,而是一种更侧重于功能模块划分、数据流向和相互连接关系的架构图。

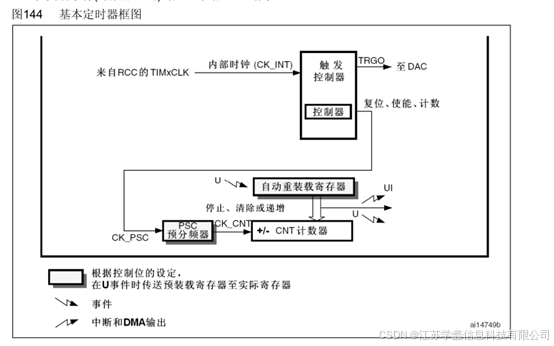

基本定时器框图

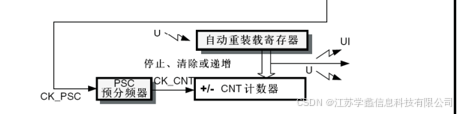

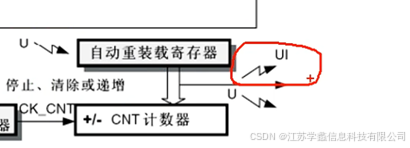

图中的三个是对于定时器最重要的部分,分别是预分频器、计数器和自动重装寄存器。它们构成了最基本的计数计时电路,所以这一块电路就叫做时基单元。

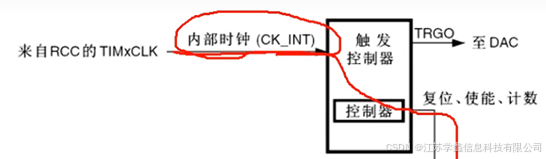

预分频器之前连接的就是基准计数时钟的输入。由于基本定时器只能选择内部时钟,所以你可以直接认为这根线直接连到了输入端的这里,也就是内部时钟CK_INT。内部时钟的来源是RCC的TIMxCLK,这里的频率值一般都是系统的主频72M赫兹,所以通向实际单元的计数基准频率就是72M。

预分频器,它可以对这个72M赫兹的计数时钟进行预分频。比如这个寄存器写0,那就是不分频或者说是1分频。这时候输出频率=输入频率等于72M赫兹。如果预分频器写1,那就是2分频,输出频率=输入频率/2,等于36M赫兹。

如果写2,就是3分频,输出=输入/3,以此类推。所以预分频器的值和实际的分频系数相差了1,即实际分频系数=预分频器的值+1。这个预分频器是16位的,所以最大值可以写65535,也就是65536分频。这就是预分频器,就是对输入的基准频率提前进行一个分频的操作。

![]()

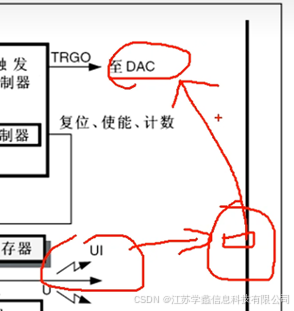

计数器可以对预分频后的计数时钟进行计数。

计数时钟每来一个上升沿,计数器的值就+1。由于这个计数器也是16位的,所以里面的值可以从0一直加到65535。如果再加的话,计数器就会回到0重新开始。所以计数器的值在计时过程中会不断的自增运行。当自增运行到目标值时,产生中断,那就完成了定时的任务。

![]()

所以现在还需要一个存储目标值的寄存器,那就是自动重装寄存器。自动重装寄存器也是16位的,它存的就是我们写入的计数目标。

在运行的过程中,计数值不断自增,自动重装值是固定的目标。当计数值等于自动重装值时,也就是计时时间到了,那它就会产生一个中断信号,并且清零计数器,计数器自动开始下一次的计数计时。

在这里图上画的一个向上的折线箭头,就代表这里会产生中断信号。像这种计数值等于自动重装值产生的中断,我们一般把它叫做”更新中断”。这个更新中断之后就会通往NVIC,我们再配置好NVIC的定时器通道,那定时器的更新中断就能够得到CPU的响应了。

![]()

这里向下的箭头代表的是会产生一个事件,这里对应的事件就叫做”更新事件”,更新事件不会触发中断,但可以触发内部其他电路的工作。

主模式触发DAC

主模式触发DAC,它能让内部的硬件在不受程序的控制下实现自动运行,在某些情况下将会极大的减轻CPU的负担。

主模式触发DAC的用途就是:在我们使用DAC的时候,可能会用DAC输出一段波形。那就需要每隔一段时间来触发一次DAC,让它输出下一个电压点。

通俗的说,就是先设置一个定时器产生中断,每隔一段时间在中断程序最终调用代码手动触发一次DAC转换,然后DAC输出。

但是有个问题,就是这样会使主程序频繁进入中断,这样会影响主程序的运行和其他中断的响应。所以定时器就设计了一个主模式,

这个主模式可以把这个定时器的更新事件映射的这个触发输出TRGO的位置。

然后TRGO直接接到DAC的触发转换引脚上。

这样定时器的更新就不需要再通过中断来触发DAC转换了,仅需要把更新事件通过主模式映射到TRGO,这样,定时器的更新事件通过主模式直接映射到TRGO输出,进而自动触发DAC转换。整个过程无需CPU介入,实现了硬件的自动化,极大地减轻了软件的负担。这就是主模式的核心作用。

这就是我的部分理解,如果有错误或补充,欢迎评论,大家共同进步。