LVDS系列32:Xilinx 7系 ADC LVDS接口参考设计(三)

比特时钟:

比特时钟DCLK的频率由ADC的分辨率、采样率、差分数据通道和转换器的对应关系决定,

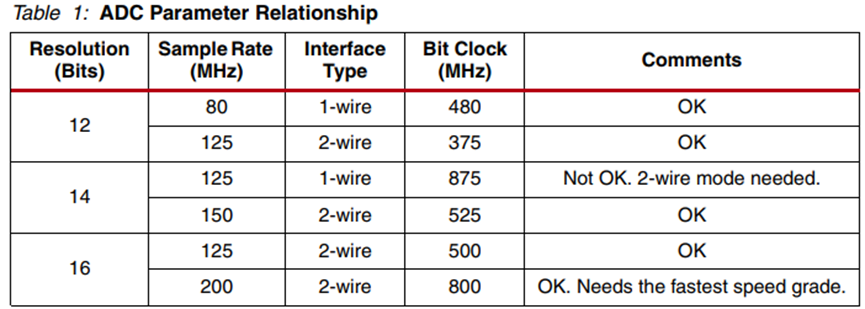

下表列出了简单的关系:

其中14位分辨率通常都是以16位输出模式进行,其他两位用于占位或是指示溢出,计算时钟速率时以16位来进行计算;

ADC提供的位时钟,与ADC输出的数据和帧信号相比,相位滞后90度。

通常情况下,ADC封装引脚处的ADC的LVDS接口的时序是比较理想的,在使用ADC时,需注意绘制PCB时需等长走线,保持一对一对齐一直保持到信号线输入到FPGA;

但是进入FPGA后,内部信号路由和时钟缓冲也会加入延时,这个时候就算ADC输入信号到FPGA输入接口处是对齐的,在FPGA中使用时,也可能会在布线后几根信号线不再对齐,所以FPGA中就需要一些逻辑控制来保证在解析LVDS接口时,LVDS信号能达到正确的时序;

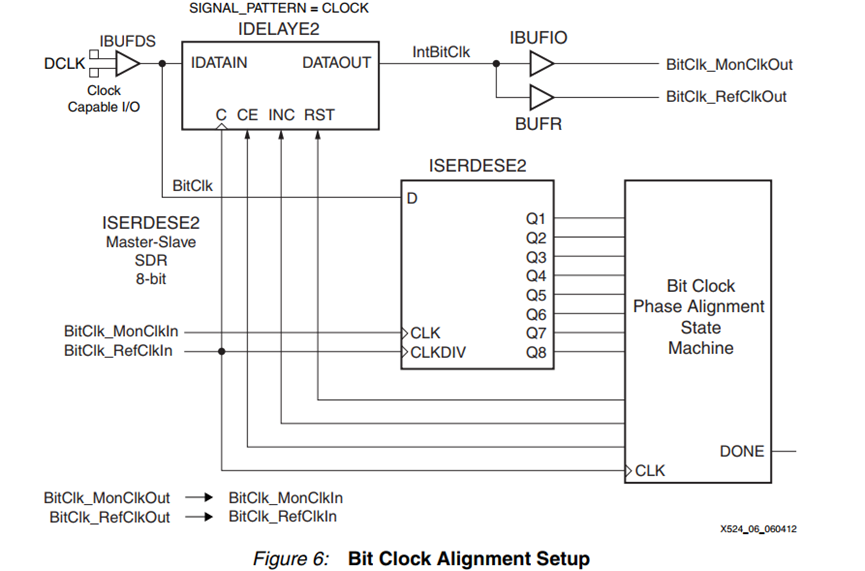

下图是Xilinx提供的比特时钟对齐逻辑:

DCLK来自ADC,从FPGA焊盘输入,为差分信号,通过一个IBUFDS原语,从差分转到单端,这里经过IBUFDS就带有一级IBUFDS延迟,变换到单端的比特时钟信号名为BitClk;

BitClk分两路,一路到IDELAYE2做延时控制,一路到ISERDESE2做串转并操作;

其中BitClk到IDELAYE2这一路,延时后的BitClk信号名为IntBitClk,IntBitClk信号再路由到IBUFIO和BUFR的输入,然后IBUFIO输出的比特时钟信号BitClk_MonClkOut,BUFR输出分频后的BitClk_RefClkOut,BUFR可以选择Bypass或是1、2、3、4、5、6、7、8这几种分频系数,BitClk_MonClkOut为对齐的DCLK,BitClk_RefClkOut为重构的后的FCLK;

然后BitClk到ISERDESE2这一路,则是将DCLK作为数据输入ISERDESE2到做串并转换,然后把输出的并行数据,给到右侧的Bit Clock Phase Alignment State Machine这个用于控制DCLK重对齐的逻辑中;

上图中BitClk_MonClkOut(连接到BitClk_MonClkIn)和BitClk_RefClkOut(连接到BitClk_RefClkIn)分别作为CLK和CLKDIV输入连接到了使用DCLK作为数据输入的这个ISERDESE2组件中,同时BitClk_MonClkOut和BitClk_RefClkOut也作为CLK和CLKDIV输入连接到这个LVDS接口解析逻辑块中的其他ISERDESE2组件中,指的也就是其他LVDS数据线等使用ISERDESE2组件;

这里使用BitClk_MonClkOut其实就是DCLK做一个可控延时后得到的位时钟,这个延时后的时钟BitClk_MonClkOut在对没有经过可控延时的BitClk做ISERDESE2串并采集并经过DCLK对齐逻辑的处理这些操作后,就可以控制并确定此时BitClk_MonClkOut相对于外部输入的原始DCLK的具体上升下降沿的位置;

比特时钟对齐状态机逻辑操作:

比特对齐状态机的逻辑使用BitClk_RefClk(同BitClk_RefClkOut)这个重构的FCLK信号来作为时钟,在其上升沿操作;

在7系FPGA中,使用的是IDELAYE2原语,搭配IDELAYCTRL原语使用,使用200M参考时钟时,单个延时tap为78ps,使用300M参考时钟时,单个延时tap为57ps,原语共32个tap,200M时钟下最大延时2.5ns左右,300M时钟下最大延时1.8ns左右;

关于对齐逻辑的前置信息:

DCLK相对于FCLK和数据信号相位偏移90度;

ADC确保DCLK默认位于有效数据眼的中间;

进入FPGA后,数据和帧经过IBUFDS,路由到ISERDESE2输入,位时钟经过IBUFDS、IDELAYE2、IBUFIO和BUFR,最后到ISERDESE2输入,该路由操作导致DCLK与数据和帧信号产生了不同的偏移,如果PCB设计完美,那么两者到FPGA焊盘时是对齐的,但是经过上述的路由操作后,时钟和数据将产生偏移,所以我们的目的是把DCLK重新定位到其原始位置即可;

IDELAYE2使用200M参考时钟时,总延时可达2.5ns(2.495ns)左右,可以完整采样一个400MHz的时钟;

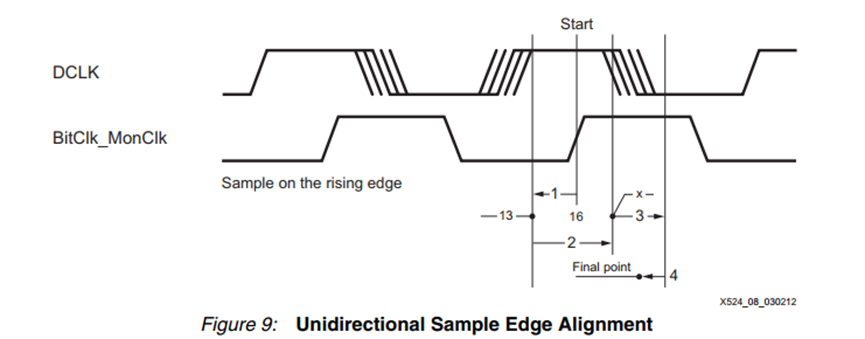

文档中给出了几个对齐逻辑的案例演示:

案例1:

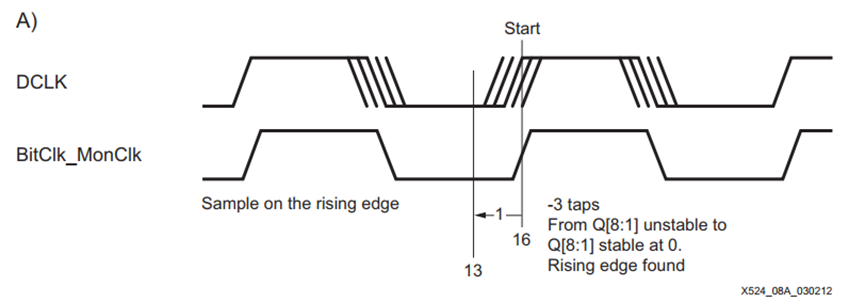

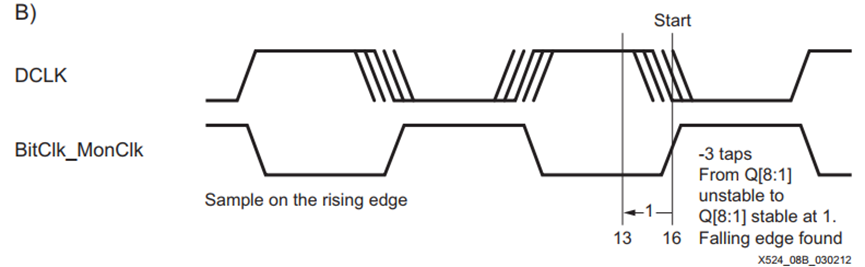

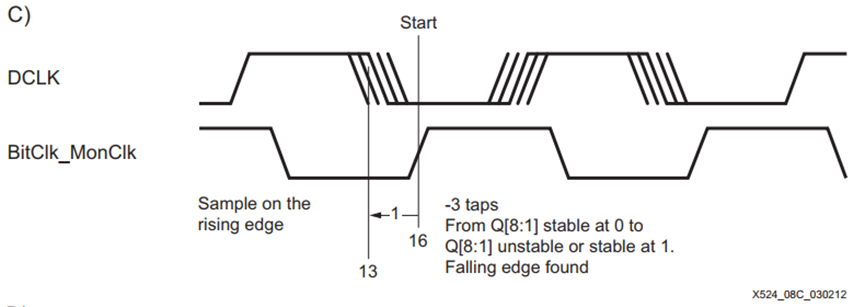

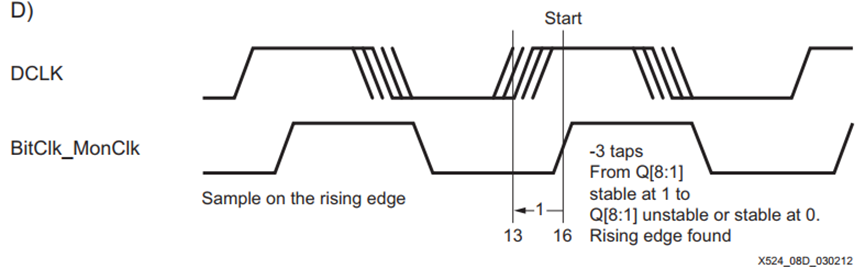

采样开始时刻发生在时钟交叉抖动的区域,且采样DCLK的ISERDESE2使用的是SDR,8bit模式,也就是下面图中,都是BitClk_MonClk的上升沿去采样DCLK,

图A,这里看到,采样值如果不稳定乱跳,说明正采样到DCLK边沿,如果BitClk_MonClk延时减小,BitClk_MonClk上升沿往左移,采样到的是全0,从不稳定到全0,说明找到上升沿;

图B,这里看到,采样值如果不稳定乱跳,说明正采样到DCLK边沿,如果BitClk_MonClk延时减小,BitClk_MonClk上升沿往左移,采样到的是全1,从不稳定到全1,说明找到下降沿;

图C,这里看到,如果BitClk_MonClk延时减小,BitClk_MonClk上升沿往左移,采样到的是从全0变化到不稳定或是全1,说明找到下降沿;

图D,这里看到,如果BitClk_MonClk延时减小,BitClk_MonClk上升沿往左移,采样到的是从全1变化到不稳定或是全0,说明找到上升沿;

案例2:

采样开始时刻发生在输出稳定全0或全1,也就是大概在DCLK稳定中心时刻,

图D,这里看到,如果BitClk_MonClk延时减小,BitClk_MonClk上升沿往左移,采样到的是从全1变化到不稳定或是全0,说明找到上升沿;

案例2:

采样开始时刻发生在输出稳定全0或全1,也就是大概在DCLK稳定中心时刻,

可以看到如上图所示,开始位置是采样稳定的中心位置,当向左或是向右移动,出现从全0变化到不稳定再到全1,或是从全1变化到不稳定再到全0,根据移动方向,就能判断出找到上升或是下降沿;

本文章由威三学社出品

对课程感兴趣可以私信联系