127.XIlinx fpga端的pcie(XDMA)与驱动是如何交换数据的

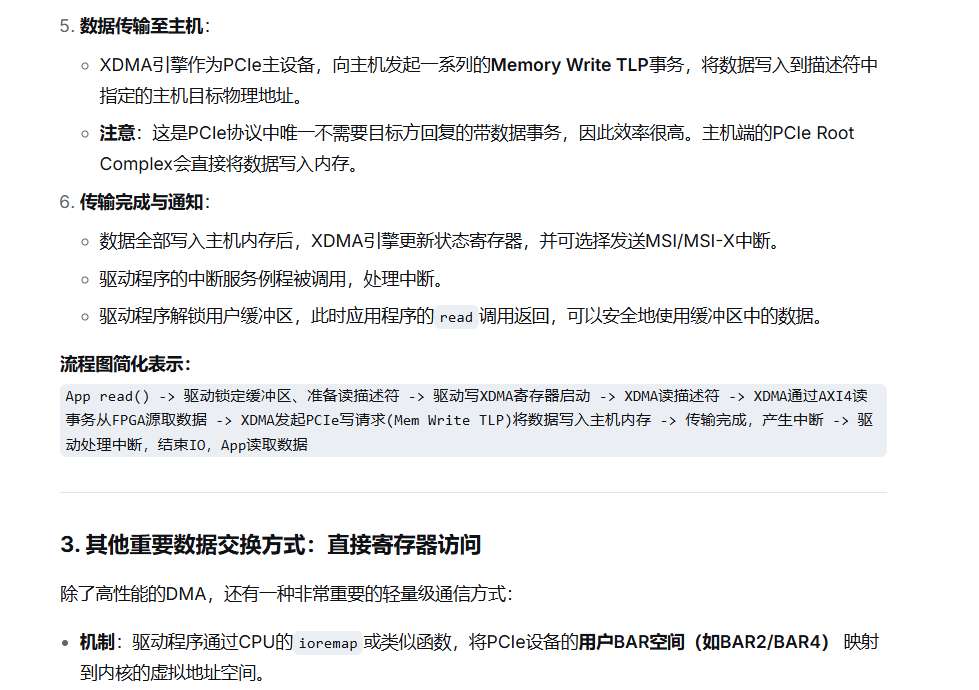

| 特性 | DMA 写(主机到FPGA) | DMA 读(FPGA到主机) | 直接寄存器访问 |

|---|---|---|---|

| 数据流向 | Host Memory → FPGA | FPGA → Host Memory | CPU寄存器 ↔ FPGA寄存器 |

| PCIe事务 | Mem Read (主机是 Completer) | Mem Write (主机是 Completer) | Mem Read/Write |

| AXI事务 | AXI4 Write | AXI4 Read | AXI4-Lite Read/Write |

| 驱动主要动作 | 准备源(主机)和目标(FPGA)描述符 | 准备源(FPGA)和目标(主机)描述符 | ioremap, iowrite/read |

| 性能 | 高带宽 | 高带宽 | 低延迟,低带宽 |

| 用途 | 传输大量数据(如图像、数据流) | 读取大量结果数据 | 配置、控制、状态查询 |

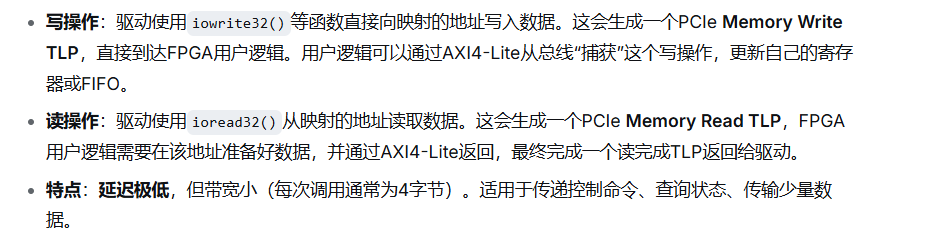

| 特性 | 模式一:与存储器交互 | 模式二:与用户逻辑交互 |

|---|---|---|

| 连接方式 | XDMA <-> AXI Interconnect <-> DDR控制器 | XDMA <-> 你的自定义逻辑(AXI Slave) |

| FPGA逻辑角色 | 被动/旁观者 | 主动参与者 |

| DMA写过程 | 数据自动写入DDR,逻辑无需关心 | 逻辑必须通过AXI-Stream接口实时接收数据,并管理背压 |

| DMA读过程 | 数据自动从DDR读出,逻辑无需关心 | 逻辑必须通过AXI-Stream接口实时提供数据 |

| 优点 | 简单,易于实现,适合大数据块缓存 | 延迟低,适合流式处理,数据可直接送入处理单元 |

| 缺点 | 延迟较高(需要经过DDR) | 逻辑设计复杂,需要正确处理AXI协议 |