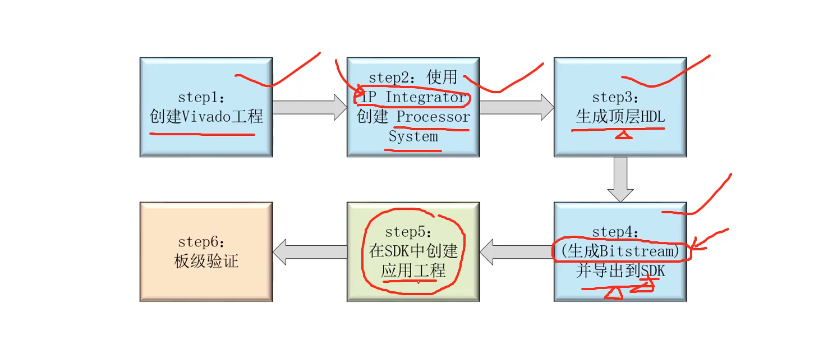

ZYNQ裸机开发指南笔记

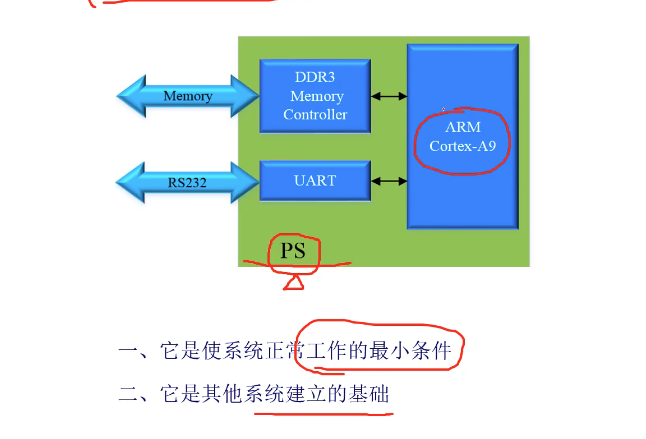

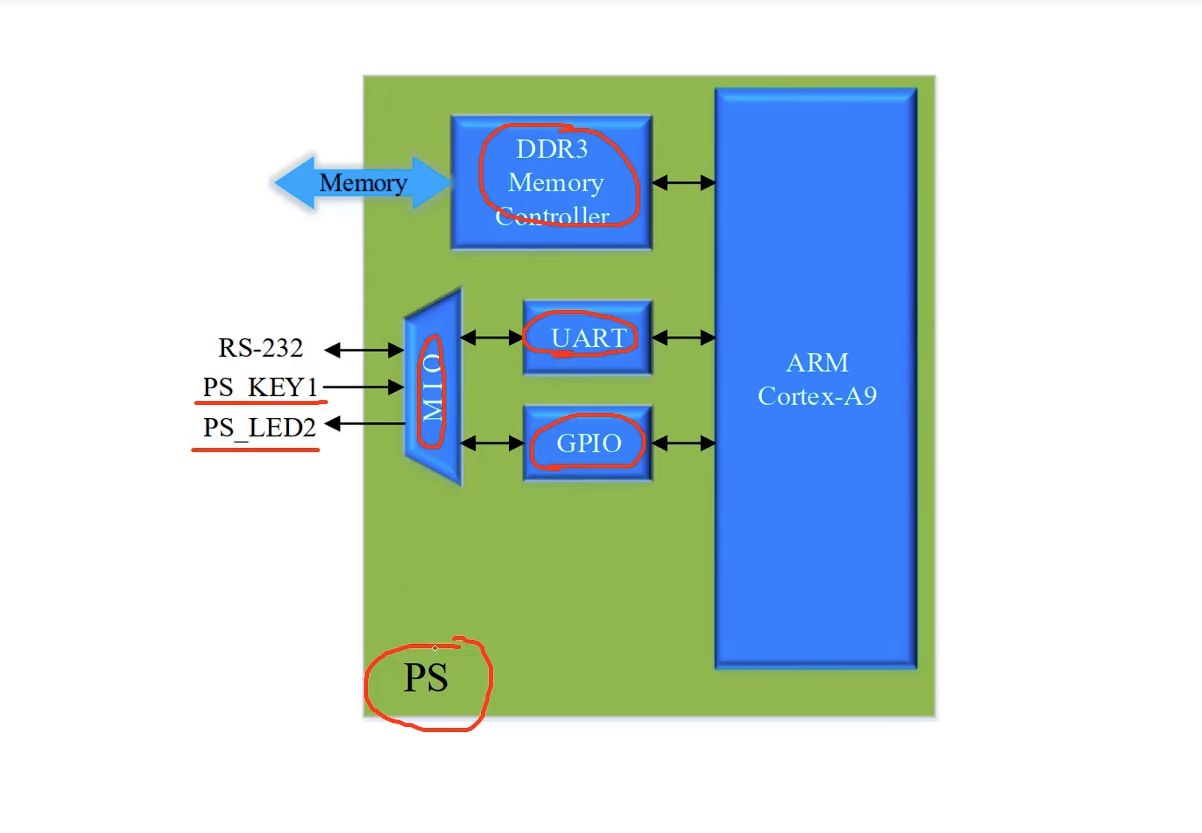

PL只是PS的一个外设,PL可以认为是FPGA。

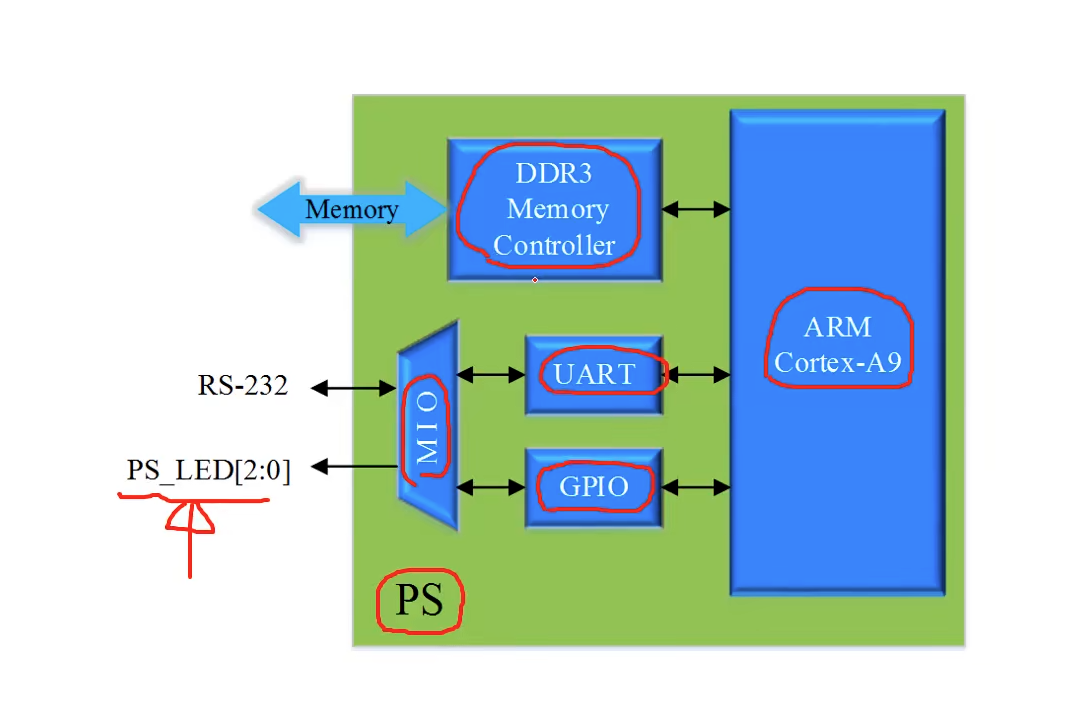

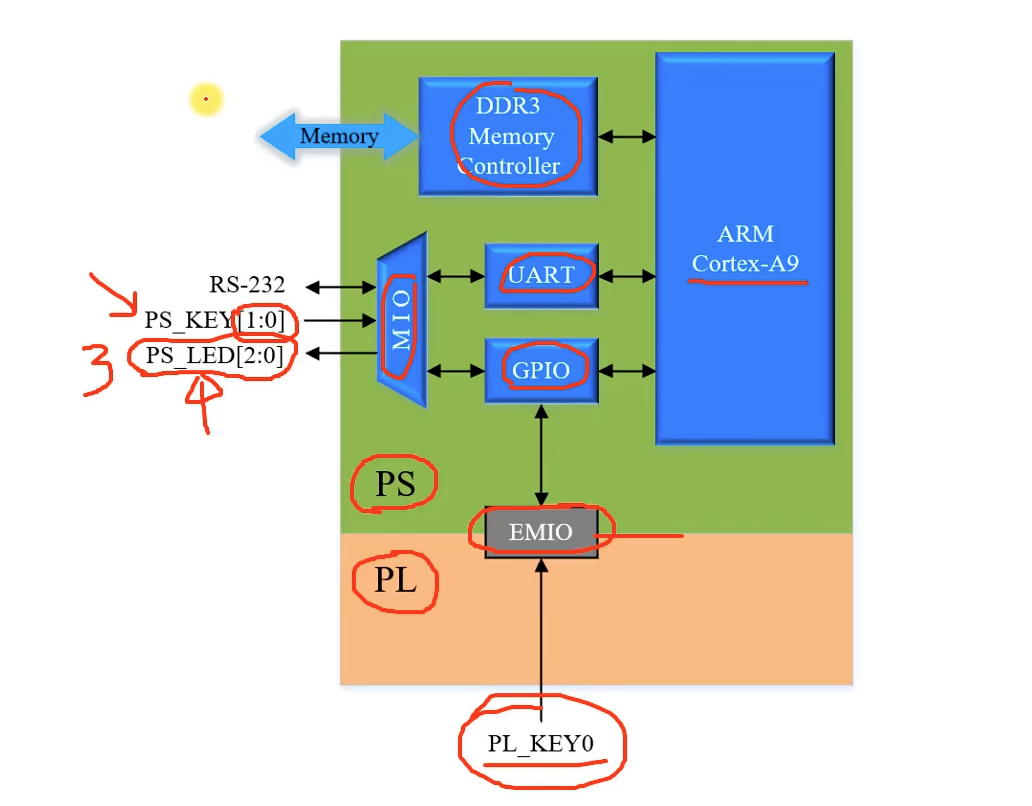

GPIO连接一些通用的设备:按键,蜂鸣器,LED灯等

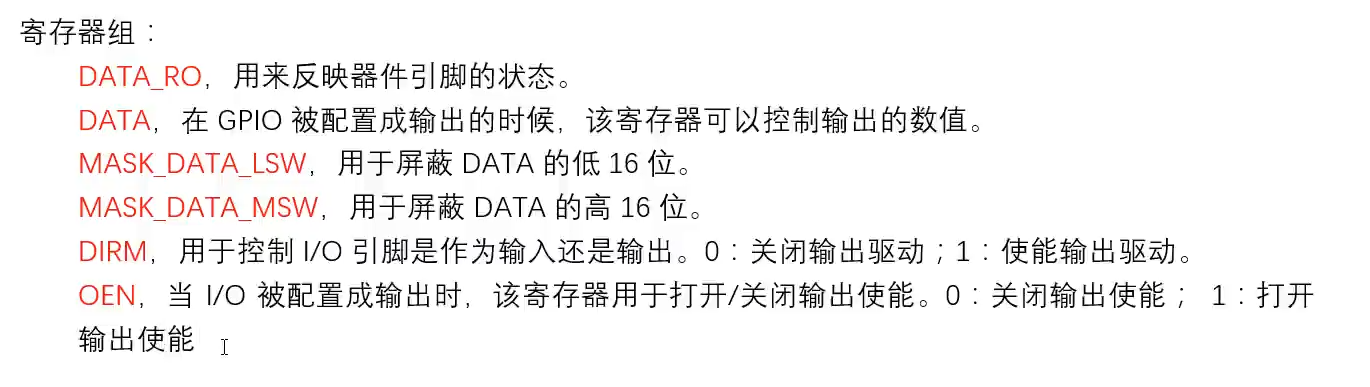

GPIO是一个外设,用来对器件引脚作观测(INPUT)和控制(OUTPUT),中断功能

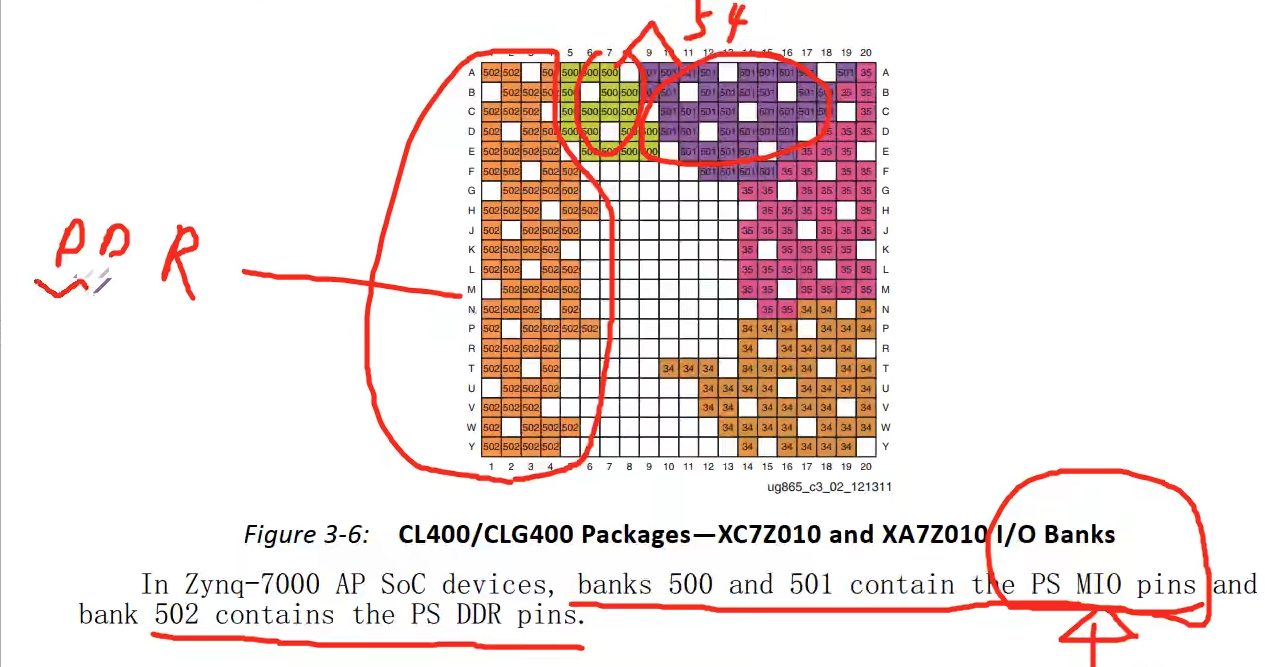

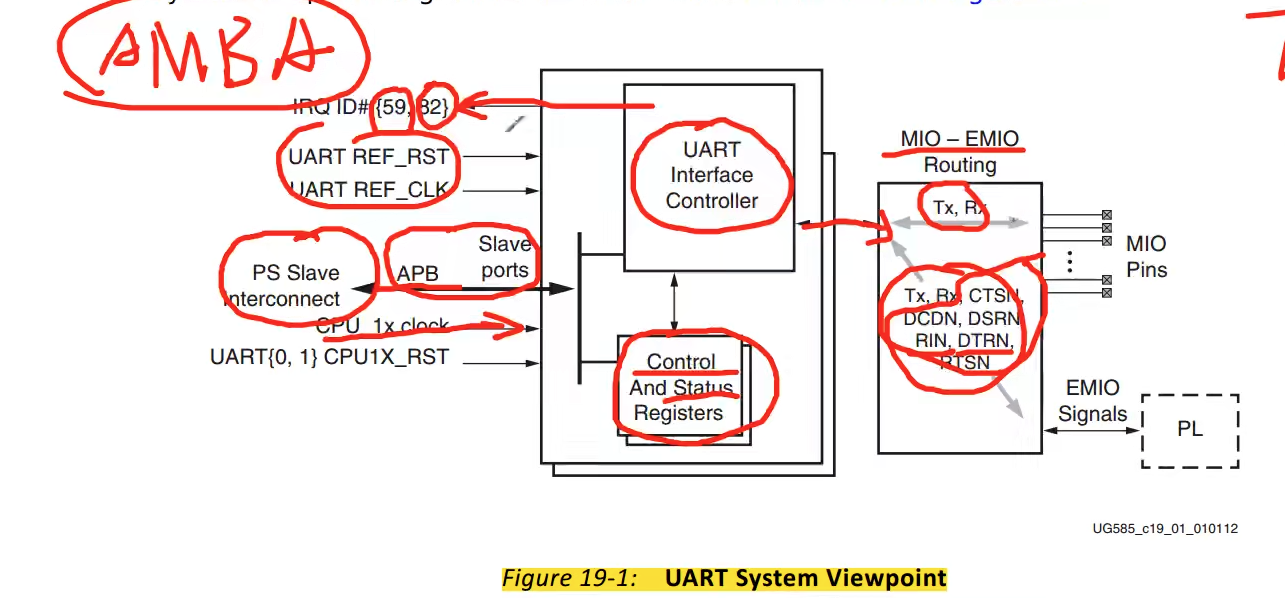

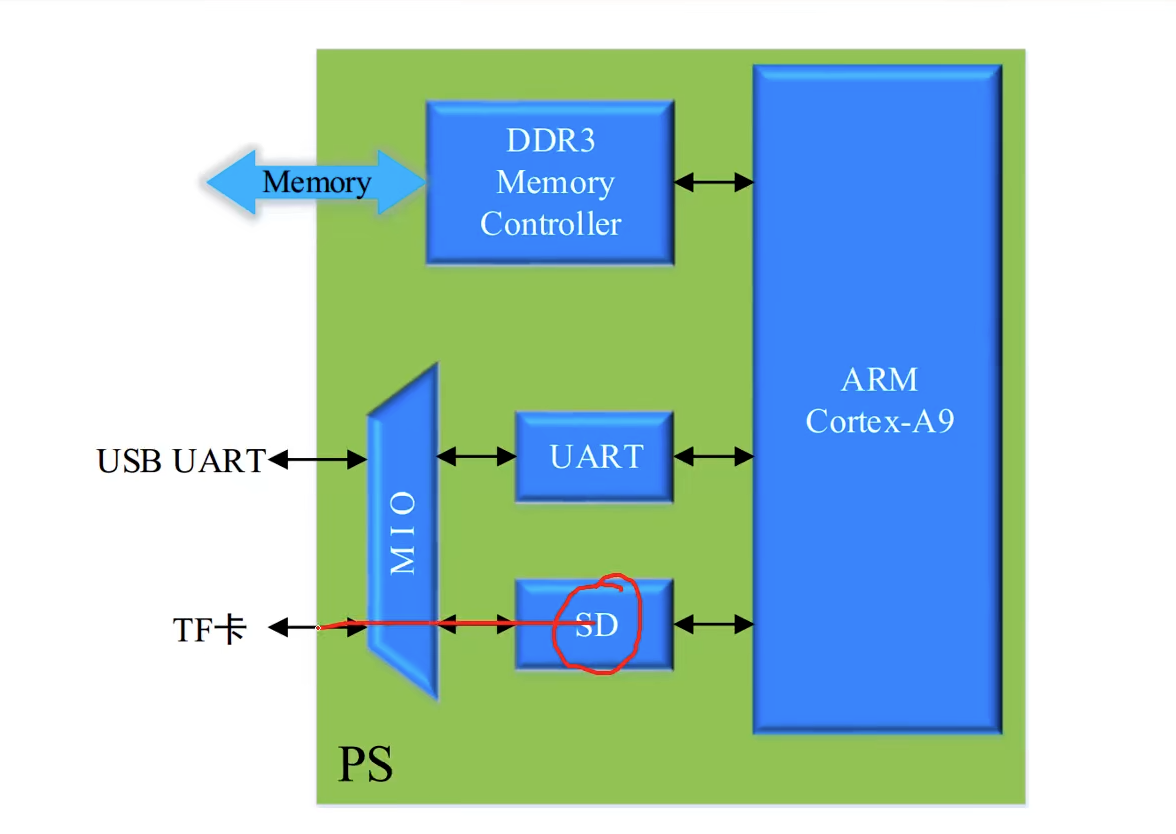

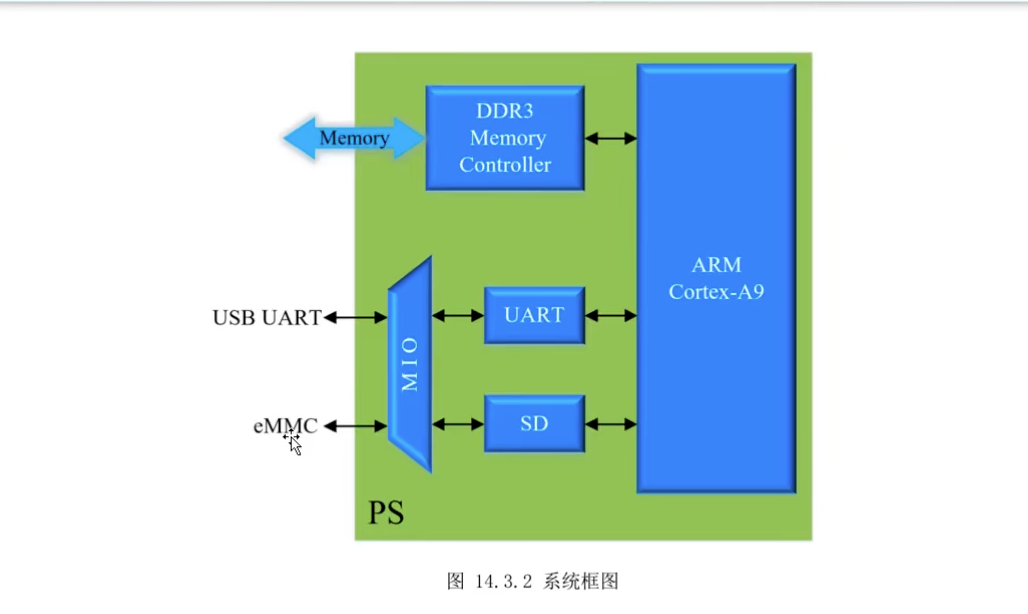

MIO:多路复用,引脚不够用可以先连接MIO(UART,SPI等)。将来自PS外设和静态存储器接口的访问多路复用到PS的引脚上

EMIO:是拓展MI,连接到PL的(连接PL的模块或者使用PL的引脚)

软件通过这一组存储映射的寄存器来控制GPIO(

)

需要注意:MIO也有两个BANK;

LED实验

EMIO设计(用到了PL端口)

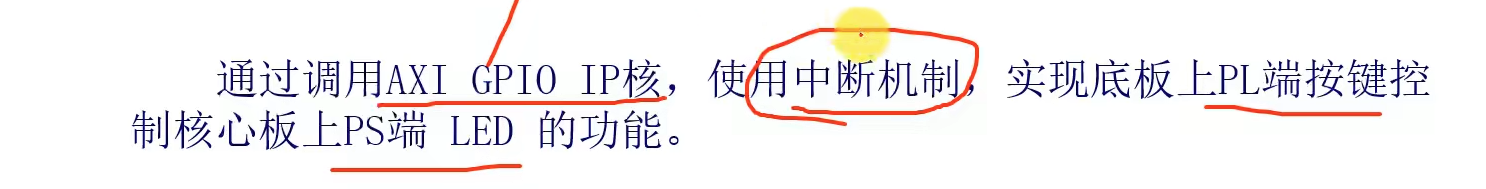

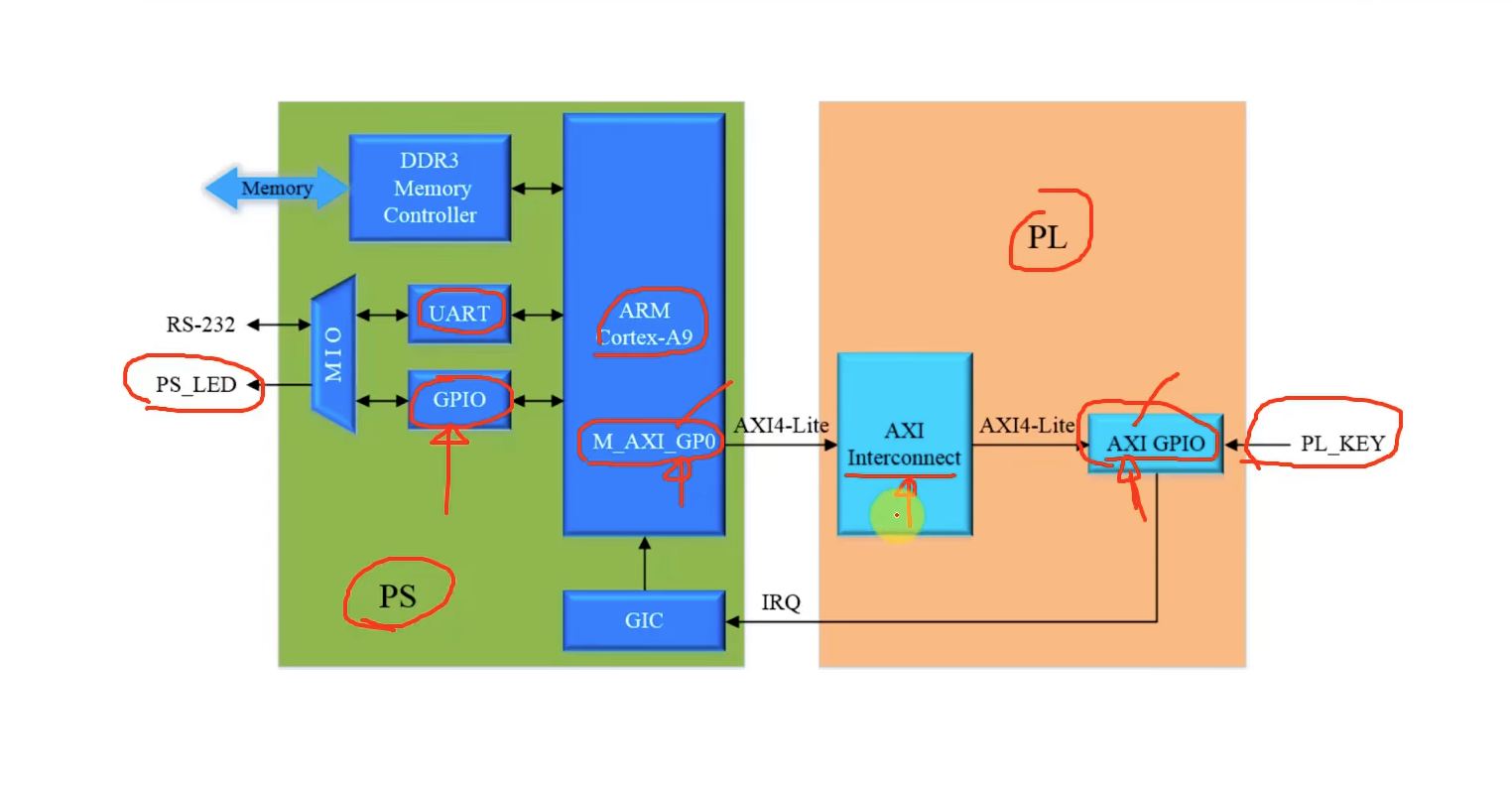

GPIO中断

AXI GPIO

是一个软核,而GPIO是确实存在的硬核

AXI 是连接PS和PL之间的桥梁

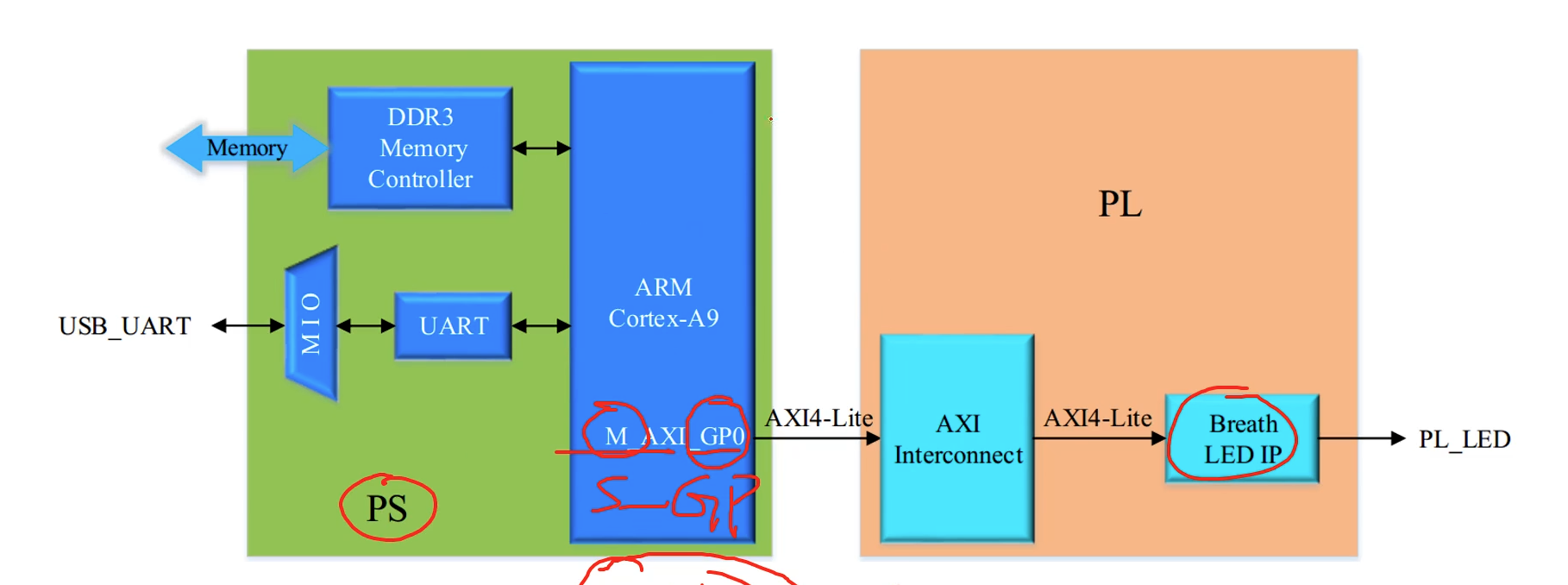

自定义IP核

ZYNQ程序固化

JTAG 一旦断电就丢失数据;

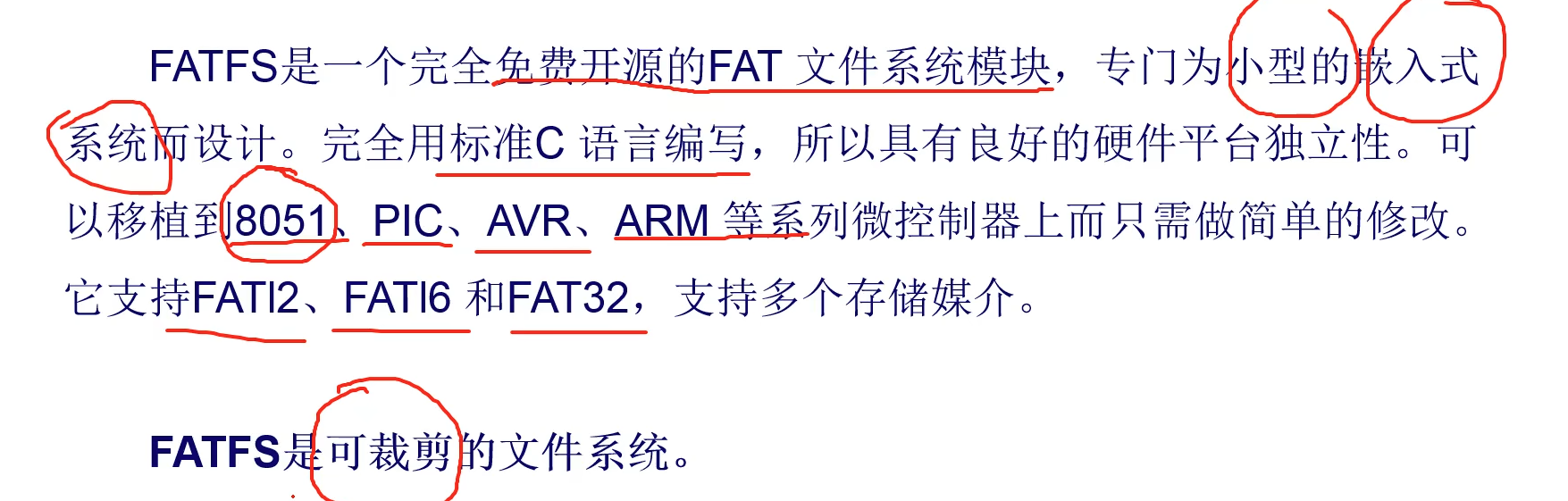

SD/QSPI 这种非易失性存储器就派上用场。(包含FSBL头用于引导配置)

硬复位在复位之后会读取引脚的状态;而软复位并不会(可能还会有些保留模式);

固化关键就是要准备好3个文件:FSBL,比特流,裸机应用程序。

利用UART可以打印出:“hello_world!”

SD卡

eMMC

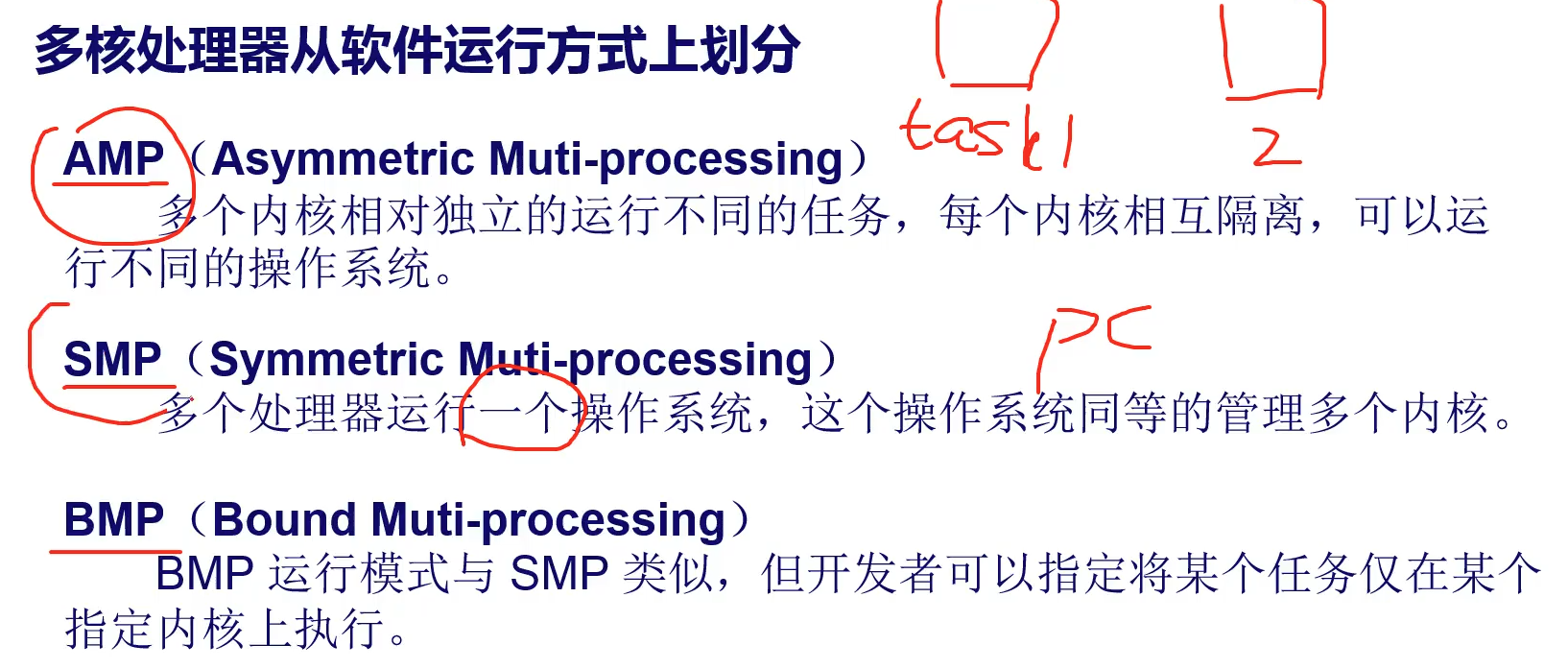

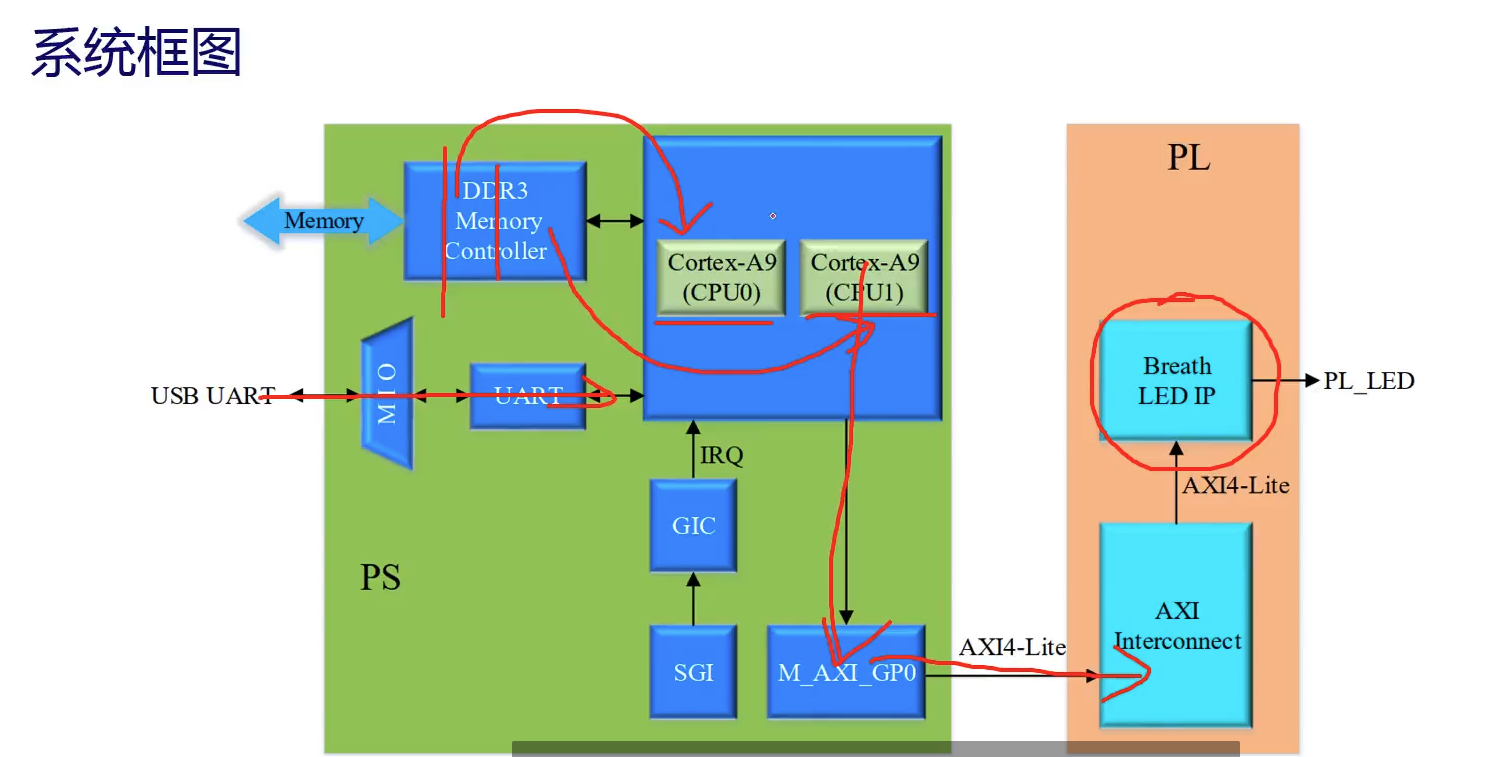

双核通信

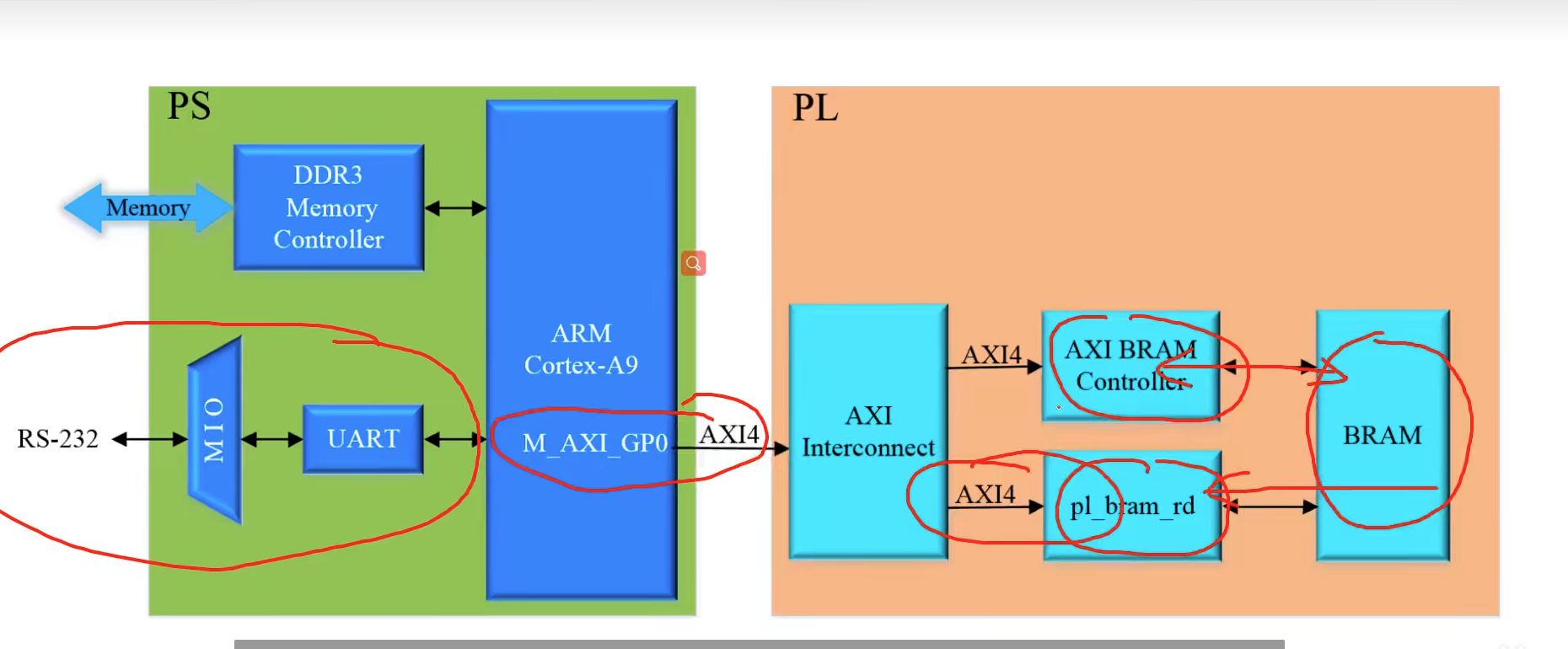

基于BRAM的PL和PS数据交互

7010的BRAM资源是2.1MB; 7020的BRAM则是4.9MB;

ECC:纠错功能按钮

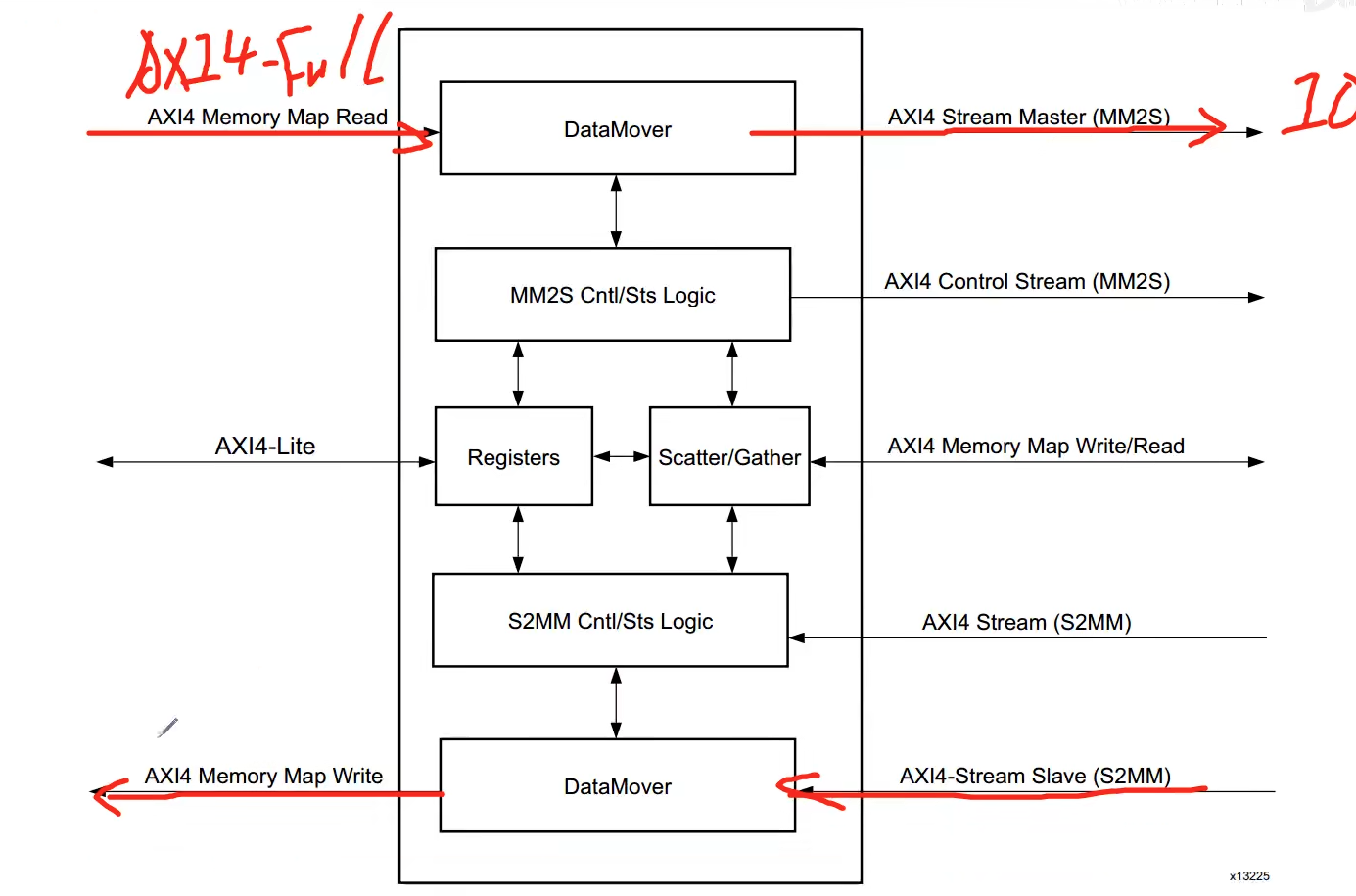

AXI 接口

其中,AXI4_Stream不属于寄存器映射,只是数据流通信

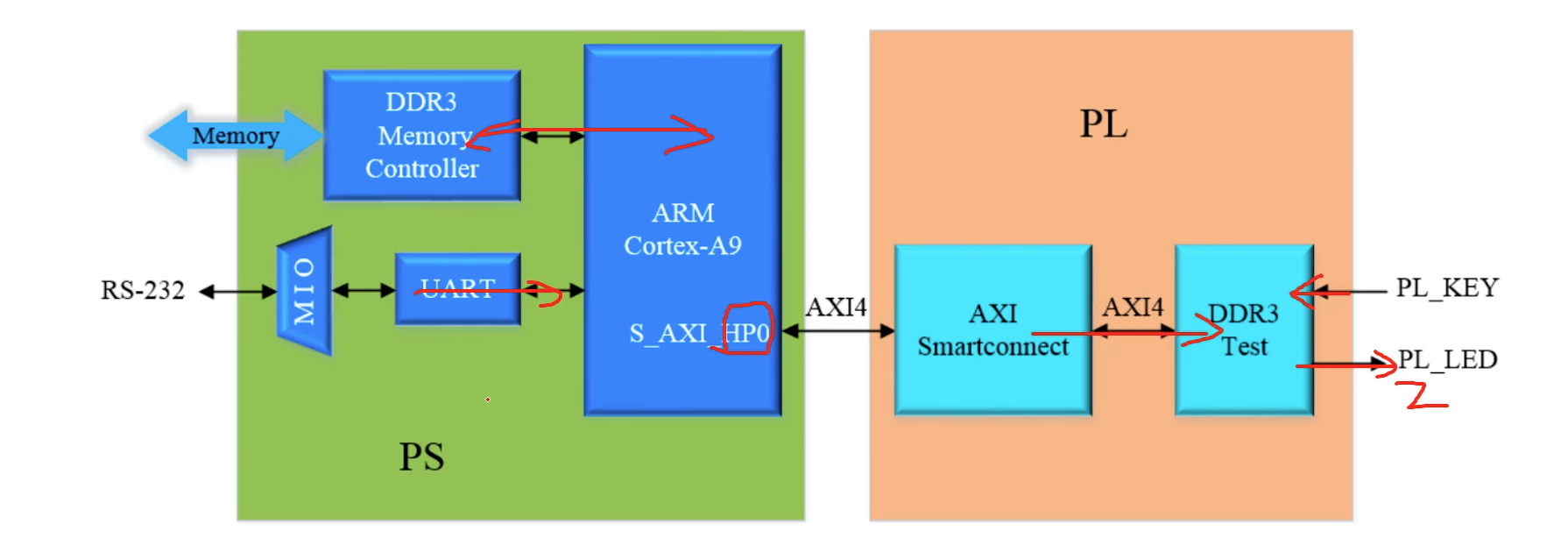

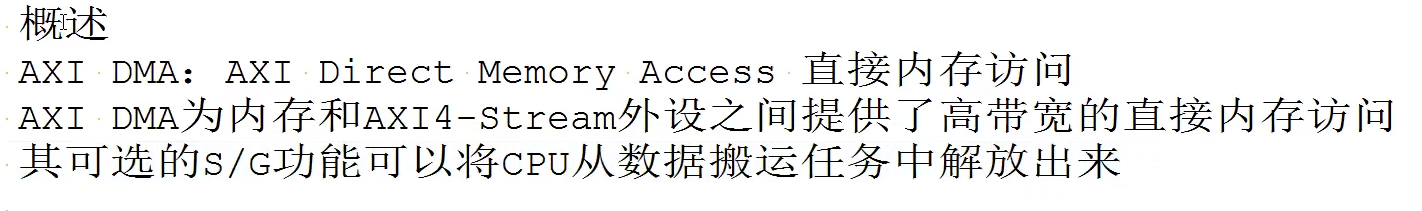

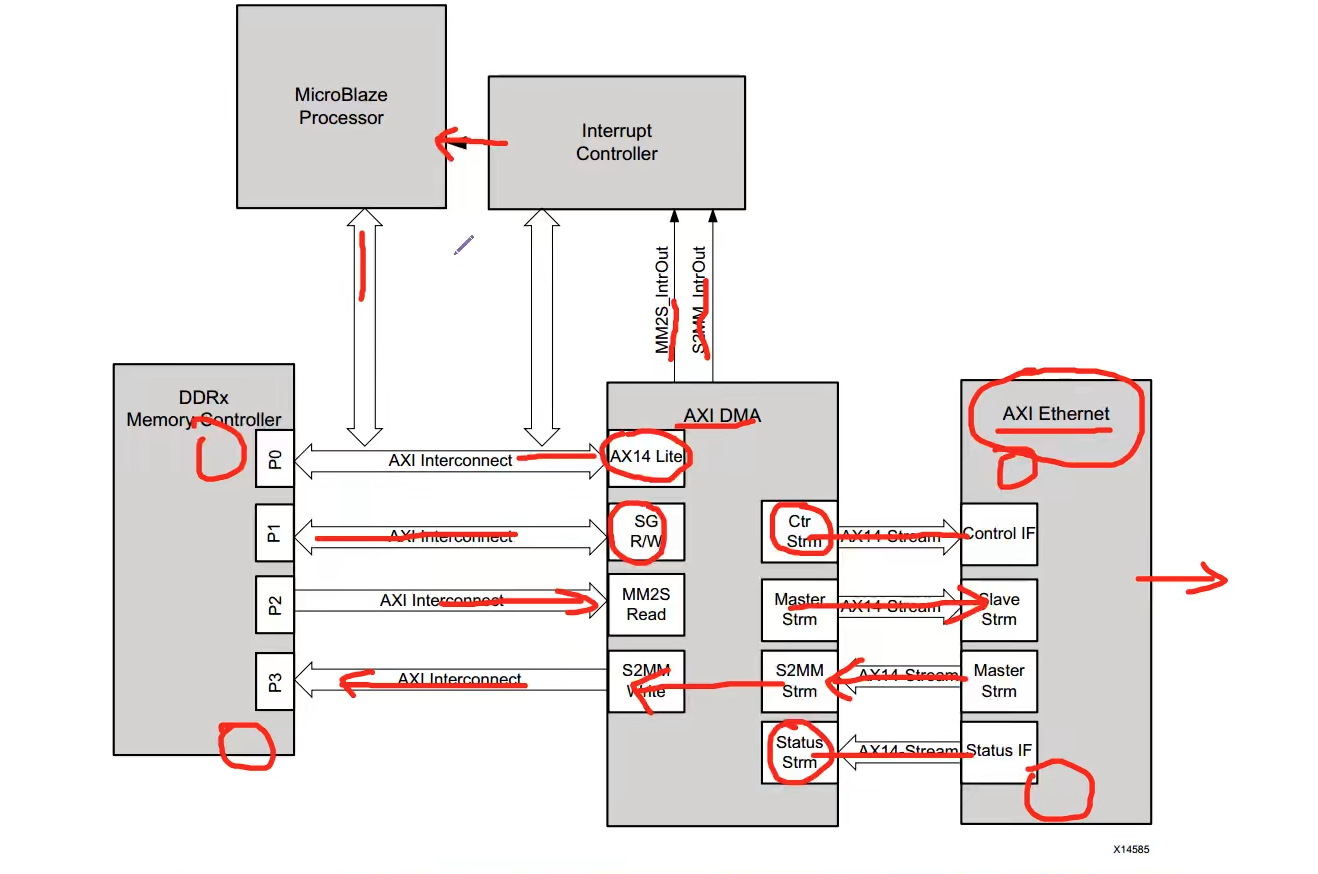

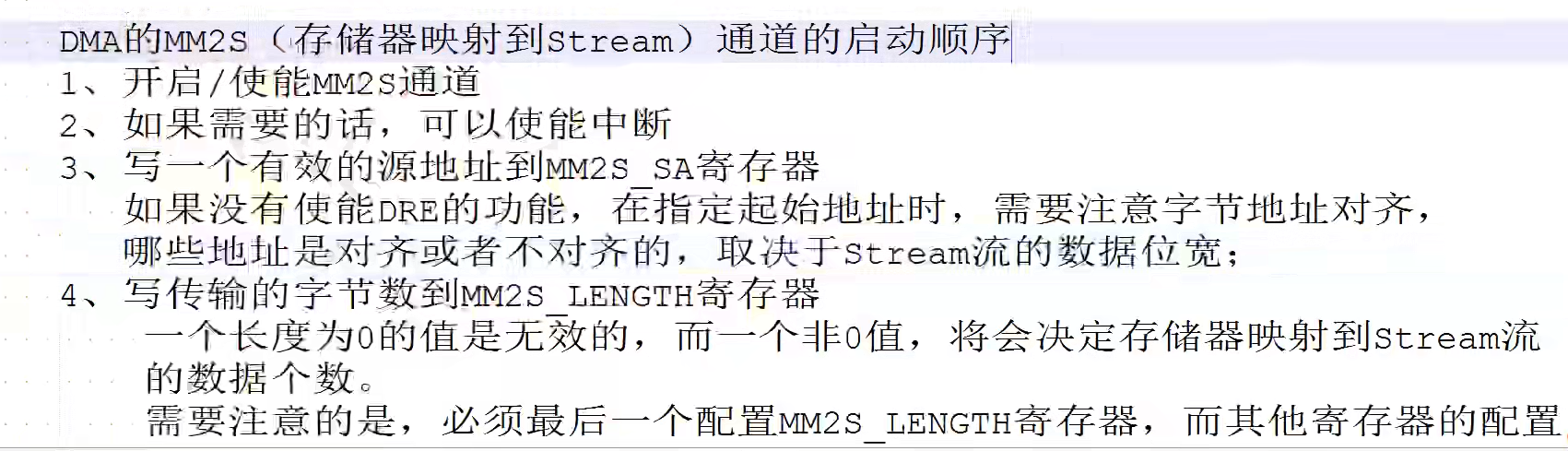

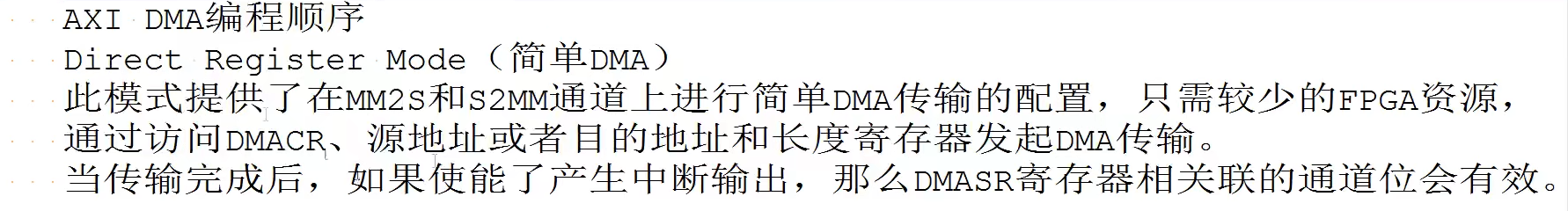

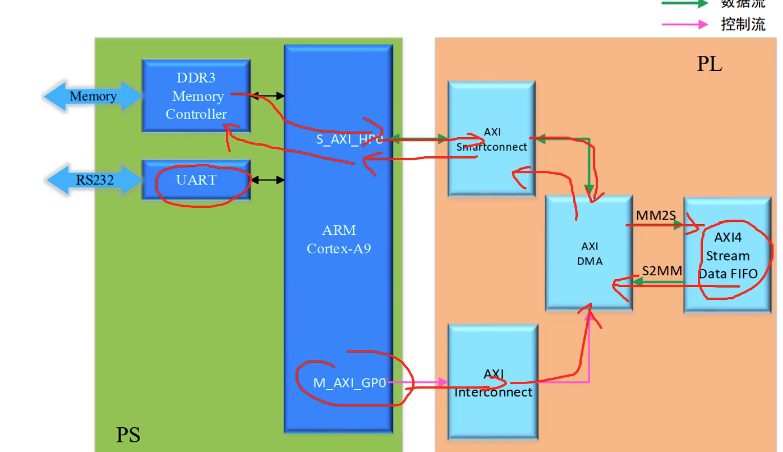

AXI DMA

HP接口可用于传输大量数据;GP接口用于传输少量数据;

smartconnect接口比interconnect接口更高效;

IP核封装和接口定义

包含IP核封装 和 自定义接口用于封装

关键在于:查看文档与开发手册一步步编写,不难的!!!!!!

注:学习自正点原子逻辑开发