NVMe高速传输之摆脱XDMA设计52: 上板资源占用率分析

本文主要交流设计思路,在本博客已给出相关博文九十多篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。若有NVME或RDMA 产品及项目需求,请看B站视频后联系。

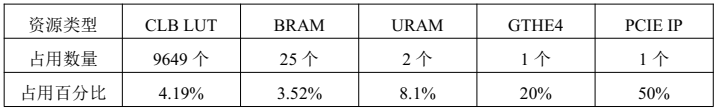

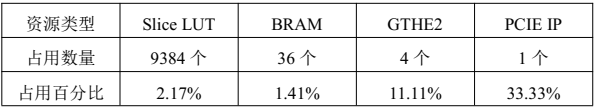

完成 Block Design 设计后进行综合与实现, NoP 逻辑加速引擎的在不同 FPGA 平台中的资源占用率分别如表 1 和表 2 所示。 从表中可以看到, 本课题设计的 NoP逻辑加速引擎资源占用率低, 使其能够更容易的被集成到应用环境中。

表1 基于 ZCU106 开发板的资源占用率

表2 基于 VC709 开发板的资源占用率

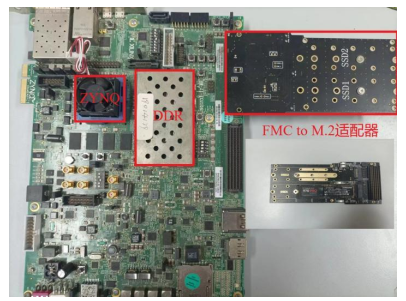

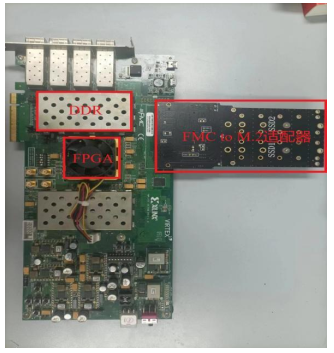

基于 ZCU106 FPGA 和 VC709 FPGA 和硬件测试平台实物连接图分别如图 1 和图 2 所示。 图中 SSD 通过 FMC to M.2 适配器连接到 FPGA 开发板上。

图1 ZCU106 连接实物图

图2 VCU709连接实物图

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click