通信协议总结

文章目录

- 一、IIC(集成电路间总线)

- 1. 核心工作原理

- 通信流程:

- 2. 拓扑结构

- 多主多从总线:

- 硬件需求:

- 3. 核心特性

- 4. 典型应用场景

- 二、UART (通用异步收发传输器)

- 1.工作原理

- 异步传输:

- 帧结构:

- 信号方向:

- 2. 拓扑结构

- 3. 核心特性

- 4. 典型应用场景

- 三、SPI(串行外设接口)

- 1. 核心工作原理

- 通信流程:

- 2. 拓扑结构

- 3. 核心特性

- 4. 典型应用场景

- 总结

提示:以下是本篇文章正文内容,下面案例可供参考

一、IIC(集成电路间总线)

https://blog.csdn.net/qq_39829913/article/details/104718185

I2C 由 NXP(原 Philips)推出,核心特点是 “双线多主多从”—— 仅需 2 根线即可实现多设备(最多 127 个)通信,支持主设备与从设备双向数据传输,适合板内多外设的中速交互(如传感器、存储芯片)。

1. 核心工作原理

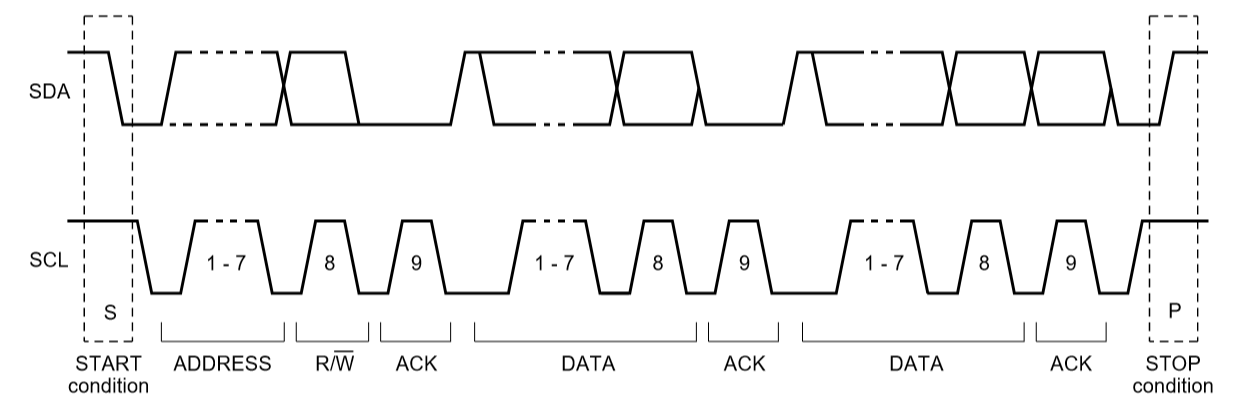

同步传输:需专用时钟线SCL(Serial Clock,主机产生)和数据线SDA(Serial Data,双向传输),所有设备共享 SCL 和 SDA(总线式连接),通过 “从设备地址” 区分不同节点。

通信流程:

主机发送 “起始信号”(SDA 从高变低,SCL 为高时),表示通信开始;

主机发送 “从设备地址”(7 位地址 + 1 位读写位,共 8 位),所有从设备比对地址,匹配的从设备回应 “应答信号(ACK)”;

主机与匹配的从设备进行数据传输(8 位数据 + 1 位 ACK),可读写双向交互;

主机发送 “停止信号”(SDA 从低变高,SCL 为高时),表示通信结束。

地址机制:每个从设备有唯一的 7 位地址(共 127 个地址,0x00~0x7F),主机通过地址选择通信对象,实现 “1 主机 + 多从机” 或 “多主机”(需仲裁机制避免冲突)。

2. 拓扑结构

多主多从总线:

所有设备共享 2 根线(SCL/SDA),每个设备都有唯一地址,支持 1 个或多个主机(如 2 个 MCU 都可作为主机,需仲裁),从设备数量由地址位数决定(7 位地址 127 个,10 位地址 1023 个)。

硬件需求:

2 根线(SCL/SDA),需在两根线上各接一个上拉电阻(通常 4.7kΩ~10kΩ),确保总线空闲时为高电平。

3. 核心特性

速率 中速,分三个等级:标准模式(100kbps)、快速模式(400kbps)、高速模式(3.4Mbps)。

距离 极短,仅支持板内通信(厘米级,如同一 PCB 上的 MCU 与传感器),总线长度通常<1 米。

优缺点 优点:少线多设备、支持双向读写、硬件成本低;

缺点:速率中等、总线长度短、多主机仲裁复杂。

4. 典型应用场景

板内多传感器:如 MCU 同时连接温湿度传感器(SHT30)、光照传感器(BH1750)、加速度传感器(ADXL345),通过 I2C 地址区分,共享 SCL/SDA 线。

存储芯片:如 EEPROM(AT24C02,用于存储配置参数)、实时时钟(RTC,DS3231,用于时间同步)。

外设控制:如 OLED 显示屏(SSD1306)、电源管理芯片(如 TPS65217),通过 I2C 传输控制指令。

二、UART (通用异步收发传输器)

https://blog.csdn.net/weixin_39939185/article/details/134657483

UART 是最基础的串行通信协议,核心特点是 “异步传输”(无需时钟线同步,通过起始位 / 停止位实现帧同步),仅需 2 根线即可实现双向通信,适合短距离、中低速的点对点数据交互

1.工作原理

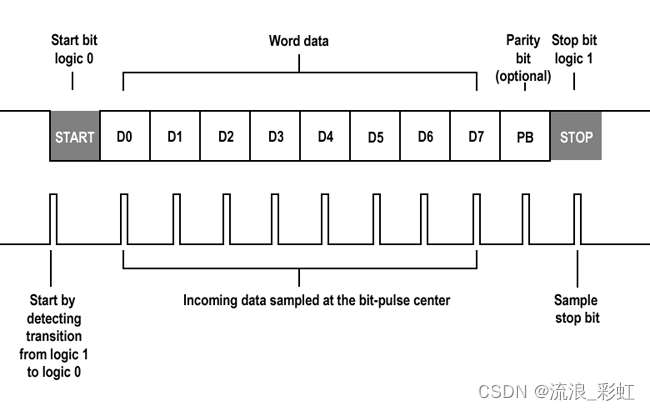

异步传输:

无专用时钟线,发送端和接收端需预先约定相同的波特率(如 9600bps、115200bps、4Mbps)、数据位(通常 8 位)、停止位(通常 1 位)、校验位(可选,如奇校验 / 偶校验),通过 “帧结构” 实现同步。

帧结构:

每帧数据包含 “1 个起始位(低电平)→8 个数据位(有效数据)→0/1 个校验位→1 个停止位(高电平)”,例如 “8N1” 格式(8 数据位 + 无校验 + 1 停止位)是最常用的配置。

信号方向:

双向通信需 2 根线 ——TX(发送端,输出)和RX(接收端,输入),发送端的TX需连接接收端的RX(交叉连接),若需多设备通信需额外扩展(如 RS485 总线基于 UART 扩展为多节点)。

2. 拓扑结构

点对点:默认仅支持 2 个设备通信(1 个主机 + 1 个从机),若需多设备(如 1 主机 + 3 从机),需通过 RS485 等总线扩展(增加差分信号和地址选择),但本质仍是 UART 协议的延伸。

硬件需求:最少 2 根线(TX/RX),无时钟线,硬件成本极低。

3. 核心特性

速率 中低速,常见波特率 1200bps~4Mbps(高速 UART 可达 10Mbps,但受距离限制)。

距离 短距离,板内通信(厘米级)或板间短距离(如 10 米内,RS232),长距离需 RS485(数百米)。

优缺点 优点:结构简单、硬件成本低、无需时钟同步;

缺点:仅支持点对点、速率受限、多设备扩展复杂。

4. 典型应用场景

板内调试:如 MCU 与串口屏、蓝牙模块(HC-05)的通信,用于打印调试信息或传输控制指令。

短距离外设:如 GPS 模块、传感器(如温湿度传感器 SHT30 的 UART 版本)、PC 与开发板的 USB 转串口通信(如 CH340 芯片)。

三、SPI(串行外设接口)

https://blog.csdn.net/as480133937/article/details/105764119

SPI 由 Motorola 推出,核心特点是 “高速同步、主从结构”—— 通过 4 根线实现主机对多从机的高速数据传输,支持全双工(同时收发),适合高速外设(如显示屏、ADC、Flash)的板内通信。

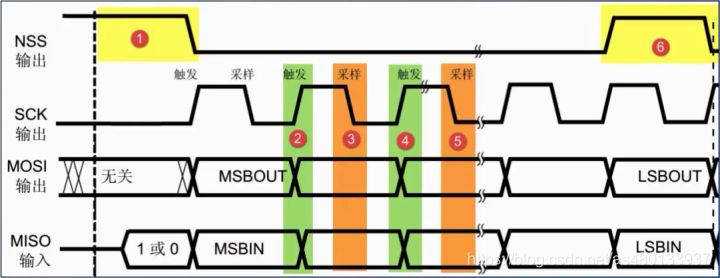

1. 核心工作原理

同步传输:需 4 根线(部分场景可简化为 3 根):

SCLK(Serial Clock,主机产生,同步时钟);

MOSI(Master Out Slave In,主机发送→从机接收);

MISO(Master In Slave Out,从机发送→主机接收);

CS(Chip Select,片选,主机通过拉低某从机的 CS 选择通信对象,多从机时需多根 CS 线)。

通信流程:

主机拉低目标从机的CS(片选有效),其他从机的 CS 保持高电平(不响应);

主机产生SCLK时钟,在时钟的上升沿 / 下降沿(预先约定),通过MOSI向从机发送数据,同时通过MISO从从机接收数据(全双工);

数据传输完成后,主机拉高CS(片选无效),结束通信。

全双工特性:MOSI 和 MISO 独立,主机和从机可同时发送数据(如主机发送控制指令的同时,从机返回传感器数据),效率高于 UART 和 I2C。

2. 拓扑结构

主从结构:1 个主机(如 MCU)可连接多个从机(如 3 个 Flash 芯片),每个从机需独立的CS线(SCLK、MOSI、MISO 共享),通过CS选择当前通信的从机,不支持多主机。

硬件需求:4 根线(SCLK/MOSI/MISO/CS),无需要上拉电阻,硬件结构比 I2C 稍复杂(多 CS 线)。

3. 核心特性

速率 高速,通常可达几 Mbps 到几十 Mbps(如 STM32 的 SPI 最高支持 50Mbps,部分芯片可达 100Mbps 以上)。

距离 短距离,仅支持板内通信(厘米级),总线长度通常<0.5 米(速率越高,距离越短)。

优缺点 优点:高速率、全双工、通信效率高、时序简单;

缺点:线数比 I2C 多(多从机需多 CS 线)、不支持多主机、速率受距离限制大。

4. 典型应用场景

高速存储:如 SPI Flash(W25Q64,用于存储固件或图片数据)、SPI RAM(IS62WV51216,用于临时数据缓存)。

高速外设:如高速 ADC(AD7606,用于数据采集)、TFT 显示屏(ILI9341,用于图像传输)、无线模块(如 LoRa 模块 SX1278)。

工业控制:如 PLC 的高速 IO 扩展模块、运动控制芯片(如步进电机驱动芯片 A4988),通过 SPI 传输高速控制指令。