深入理解AMBA总线(12)AXI突发传输和AXI控制信号

深入理解AMBA总线(十二)AXI突发传输和AXI控制信号

本篇文章给大家讲解AXI协议的读写时序以及AXI的一些控制信号。

重点信号如下:

Learn the architecture - An introduction to AMBA AXI

Write Address (AW) channel signals AXI version

AWVALID AXI3 and AXI4

AWREADY AXI3 and AXI4

AWADDR[31:0] AXI3 and AXI4

AWSIZE[2:0] AXI3 and AXI4

AWBURST[1:0] AXI3 and AXI4

AWCACHE[3:0] AXI3 and AXI4

AWPROT[2:0] AXI3 and AXI4

AWID[x:0] AXI3 and AXI4

AWLEN[3:0]

AWLEN[7:0] AXI3 only

AXI4 only

AWLOCK[1:0]

AWLOCK AXI3 only

AXI4 only

AWQOS[3:0] AXI4 only

AWREGION[3:0] AXI4 only

AWUSER[x:0] AXI4 only

The following table shows the Write Data channel signals:

Write Data (W) channel signals AXI version

WVALID AXI3 and AXI4

WREADY AXI3 and AXI4

WLAST AXI3 and AXI4

WDATA[x:0] AXI3 and AXI4

WSTRB[x:0] AXI3 and AXI4

WID[x:0] ] AXI3 only

WUSER[x:0] AXI4 only

The following table shows the Write Response channel signals:

Write response (B) channel signals AXI version

BWVALID AXI3 and AXI4

BWREADY AXI3 and AXI4

BRESP[1:0] AXI3 and AXI4

BID[x:0] AXI3 and AXI4

BUSER[x:0] AXI4 only

All the signals in each channel have the same prefix:

• AW for the Write Address channel

• W for the Write Data channel

• B for the Write Response channel

There are some differences between the AXI3 protocol and the AXI4 protocol for the write channels:

• For the write address channel, the AWLEN signal is wider for the AXI4 protocol. Therefore, AXI4 is able to generate longer bursts than AXI3.

• AXI4 reduces the AWLOCK signal to a single bit to only accommodate exclusive transfers because locked transfers are not supported.

• AXI4 adds the AWQOS signal to the AW channel. This signal supports the concept of quality of service (QoS) in the AXI4 protocol.

• AXI4 adds the AWREGION signal to the AW channel. This signal supports subordinate regions which allow for multiple logical interfaces from a single physical subordinate interface.

• AXI4 removes the WID signal from the W channel. This is because write data reordering is no longer allowed.

• AXI4 adds user-defined signals to each channel.

Read channel signals

The channels used for a read transaction are:

• Read Address

• Read Data

The following table shows the Read Address channel signals:

Read Address (AR) channel signals AXI version

ARVALID AXI3 and AXI4

AREADY AXI3 and AXI4

ARADDR[31:0] AXI3 and AXI4

ARSIZE[2:0] AXI3 and AXI4

ARBURST[1:0] AXI3 and AXI4

ARCACHE[3:0] AXI3 and AXI4

ARPROT[2:0] AXI3 and AXI4

ARID[x:0] AXI3 and AXI4

ARLEN[3:0]

ARLEN[7:0] AXI3 only

AXI4 only

ARLOCK[1:0]

ARLOCK AXI3 only

AXI4 only

ARQOS[3:0] AXI4 only

ARREGION[3:0] AXI4 only

ARUSER[x:0] AXI4 only

The following table shows the Read Data channel signals:

Read Data ® channel signals AXI version

RVALID |AXI3 and AXI4|

RREADY |AXI3 and AXI4|

RLAST AXI3 and AXI4

RDATA[x:0] AXI3 and AXI4

RRESP[1:0] AXI3 and AXI4

RID[x:0] ] AXI3 and AXI4

RUSER[x:0] AXI4 only

下面是官网的一些说明:

All the signals in each channel have the same prefix:

• AR for the Read Address channel

• R for the Read Data channel

There are some differences between the AXI3 protocol and the AXI4 protocol for the read channels:

• For the AXI4 protocol, the read address length signal ARLEN is wider. Therefore, AXI4 is able to generate longer read bursts than AXI3.

• AXI4 reduces the ARLOCK signal to a single bit to only accommodate exclusive transfers because locked transfers are not supported.

• As with the write channel signals, the concepts of quality of service and subordinate regions apply to read transactions. These use the ARQOS and ARREGION signals in the AR channel.

• AXI4 adds user-defined signals to the two read channels.

Data size, length, and burst type

Each read and write transaction has attributes that specify the data length, size, and the burst signal attributes for that transaction.

In the following list of attributes, x stands for write and read, so they apply to both the Write Address channel and the Read Address channel:

• AxLEN describes the length of the transaction in the number of transfers.

o For AXI3, AxLEN[3:0] has 4 bits, which specifies a range of 1-16 transfers in a transaction.

o For AXI4, AxLEN[7:0] has 8 bits, which specifies a range of 1-256 data transfers in a transaction.

• AxSize[2:0] describes the maximum number of bytes to transfer in each data transfer. Three bits of encoding indicate 1, 2, 4, 8, 16, 32, 64, or 128 bytes per transfer.

• AxBURST[1:0] describes the burst type of the transaction: fixed, incrementing, or wrapping. The following table shows the different properties of these burst types:

Value Burst type Usage notes Length (number of transfers) Alignment

0x00 FIXED Reads the same address repeatedly. Useful for FIFO s. 1-16 Fixed byte lanes only defined by start address and size.

0x01 INCR Incrementing burst.

The subordinate increments the address for each transfer in the burst from the address for the previous transfer.

The incremental value depends on the size of the transfer, as defined by the AxSIZE attribute.

1、AXI突发传输

1.1、AXI突发传输时序图

AXI总线是基于突发传输的,并且AXI的突发是只需要给一次地址信号即可,这样就免去了地址计算的逻辑。对于只存在给一个地址给一个数这样的传输场景,不建议使用AXI总线,APB即可。或者使用AXI-lite。

首先还是解释一下为什么要有突发传输这件事。因为很多时候我们需要的不仅仅是一个地址的32bit数据,而是从这个地址开始的很多很多数据,这非常好理解。比如去写数组或者读数组,你的数组元素往往有很多很多,因此对于这种情况你就需要突发传输,如果没有突发传输就只能够给个地址给个数,非常的浪费资源和功耗。(地址额外的翻转,额外的地址计算逻辑等等)

Adress and Burst Logic

.High latency system(DRAM)

.Burst

.Transfer length

.AxADDR,AxSIZE,AxLEN,AxBURST

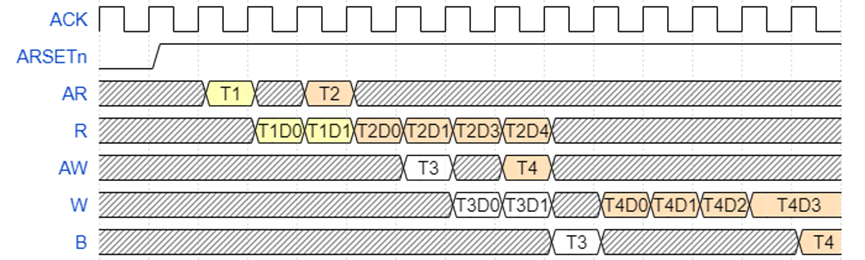

Example of multiple transactions

T1(arlen=1),T2(arlen=3) Read transactions

T3(awlen=1),T4(awlen=3) Write transactions.

以读突发传输为例,可以看到在T2的时刻AR通道握手成功,成功传输了地址信息。然后Slave就可以根据该地址信息返回相应的读数据,每次RVALID和RREADY握手成功的时候,返回了一个数据,称之为一次transfer,握手一次返回一次数,当返回最后一笔数据的时候,相应的RLAST也需要拉高,来表示最后一笔数据已经给出,整个Transaction到此结束。

之前已经说过,AXI支持Outstanding,在Master给出一个地址以后,可以紧接着再给出一个地址。即使第一个地址的数据还没有返回,这种情况的波形如下图所示:

我们再看一下突发写操作,同样的Master给出写地址,握手成功,然后给出写数据,当给出最后一个写数据的时候,WLAST拉高,然后B通道返回BRESP和BVALID,握手成功代表写transaction结束,通信完成。有一点需要注意,AXI3中给出了WLAST即可返回BVALID,但是AXI4中规定了,必须写地址通道握手成功了,也给了WLAST才允许返回BVALID,显然下面这个图满足了AXI4这个要求。这个实际上还是比较能够理解的,因为作为Slave,即便你已经收到了所有的数据,如果你没有收到相应的地址,你是不知道写往何处的,这个时候给出BVALID当然是不太合乎逻辑的。(此外虽然没有硬性规定写数据必须在写地址通道之后,但我建议还是最好这样设计,这样更符合直觉,和读也更加相对称)

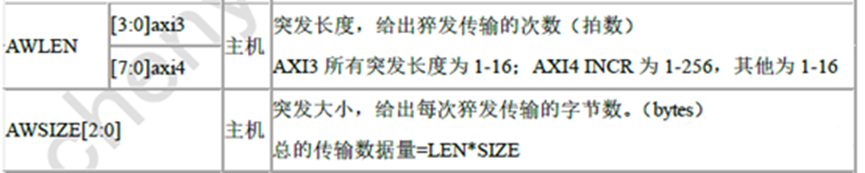

1.2、AXI突发传输信号

看完了AXI的突发读和突发写时序图,我们进一步学习突发传输相关的信号,细心的读者可能发现了,上面的控制信号只给了地址信号,写数据大小,突发长度都没有体现,实际上面只是简化版本的,忽略了控制信号细节,以下为大家梳理一下,跟突发相关的控制信号总共是有以下三个信号,分别是LEN、SIZE和BURST信号。

首先是突发长度,AWLEN和ARLEN两个信号指定了每一笔突发传输有多少笔Data Transfer,对于AXI3,支持116笔transfer,分别对应000111,对于AXI4,支持1256笔transfer,分别对应0000000011111111。

值得注意的是,对于写而言,AWLEN信号很多时候没什么用,因为WLAST才是真正的最后一笔写传输的标志,有些设计AWLEN甚至就是默认值,主机那边控制好WLAST即可,这种方法也可以,但不建议,WLAST按理说要和AWLEN对应好!

然后是突发数据大小,AWSIZE和ARSIZE两个信号,该信号用来标志传输的数据位宽哪些bit是有效的,一般是从低位开始算,比如ARSIZE为’b001的时候,则代表transfer的size为2Bytes。对应ARDATA[15:0]是有效的。

最后讲一下突发传输类型,AWBURST和ARBURST两个信号,AXI中一共支持三种类型,比AHB更简洁。

Burst type:一共有三种类型,分别是FIXED、INCR和WRAP。

o FIXED:该burst中每个transfer的地址是相同的;这种模式被用来重复访问同一个location,比如当加载或清空一个FIFO;

o INCR:该burst中后一个transfer的地址是前一个transfer地址的递增值,递增的大小是Burst size;这种模式用来访问一段连续的内存;

o WRAP:和INCR模式基本一致,唯一的不同是当触及高地址的边界,会回环到低地址,类似于循环buffer;这种模式用来做cache line的访问。

第一种类型为FIXED类型,顾名思义,地址固定,这个时候可能是普通的传输,即Burst length为1。也有可能是重复访问相同的地址,比如加载或者清空FIFO的情况。

我们来看这样的一个场景,你有一个audio的控制器模块,其输入是audio的流数据,我们先不用管流数据哪里来的,可能是外部直接接进来,或者是经过什么转换来的。这个流数据我们需要缓存到内部的FIFO,一旦满了,通知DMA将FIFO的数据搬运到Memory。这个时候我们可以发现,你每次搬运的源头,其都是位于同样的FIFO,同样的地址,因此我们就可以发起一个突发的读,这个突发读的Transcation可能对应16笔Transfer,每一笔Transfer都会将FIFO搬空。

第二种类型为INCR类型,这种情况下地址是递增的,支持非对齐访问。增加的地址大小和AxSIZE相关。这个其实是最常见的,也非常好理解,就不过多解释了。

第三种类型为WRAP类型,Wrap Burst是AXI协议中的一种突发类型,用于处理循环地址空间的读写操作。在这种模式下,地址在达到某个上限(upper boundary)后会自动回卷到下限(lower boundary),从而形成一个循环的地址序列。

第三种的边界计算如下。

WRAP猝发类似于INCR猝发。在WRAP中,地址将根据SiZE递增,但是达到地址上限时,地址将换到地址下限。

在WRAP地址计算过程中有两个注意事项,

- 计算WRAP的地址上限

- 低位地址回旋到WRAP

WRAP突发有限制:

• 起始地址必须与每次传输的大小对齐

• 突发长度必须为2、4、8或16个传输

2、AXI其它的一些控制信号

这些控制信号不是必用的,取决于实际应用的场景,AXI提供这些信号作为额外的功能支持。

2.1、保护功能支持

这些信号主要是AXI作为Master的时候才会使用,其它模块之间的AXI协议传输基本上用不到这些信号。

保护信号分别是AWPROT和ARPORT,该信号为3bit,因此也提供了三种类型的访存保护(其实就是附带一些额外的信息,用来避免非法的transaction操作)。

AXPROT[0]用来区分是普通访存还是特权访存,如下图所示,比如操作系统这一块地址,普通的访存当然是不被允许的,一般是拥有较高的权限,才允许进行访存,体现在硬件上实际就是Normal access还是Privileged Access,这个时候就得借助该信号。

AXPROT[1]用来区分是Secure还是Non-Secure,如下图所示,Secure Region一般是内存中特别机密的信息,同理这也需要处理器的支持,只有Secure的程序才允许访问Secure Region。

AXPROT[2]用来区分是Instruction还是Data,这个用于区分CPU是取指令还是取数据,实际上用的很少,很多时候可能取得是指令,但是标明的是Data,ARM的官方手册也有这么一句话:This indication is provided as a hint and is not accurate in all cases. For example, where a transaction contains a mix of instruction and data items. It is recommended that, by default, an access is marked as a data access unless it is specifically known to be an instruction access。

因此对于该比特,大家选择性的使用即可,一般是用不到的。常用的就上面的[0]和[1]bit。

最后关于保护信号做一个总结,如下所示:

2.2、Cache支持

对于现代的SoC而言,Cache可以存在于SoC的很多地方,比如有以下场景:

挨着处理器核(L1 Cache)

在Interconnect内部(L2 Cache)

靠近Memory控制器(L3 Cache)

正是因为系统中有了这些Cache,相应的也需要Cache相关的信号(总线信号的设计是为了SoC系统服务的),来帮助我们存放数据到想要的位置或者从想要的位置取数据。(看懂这小节需要基本的Cache相关的知识,如果没有请去看计算机组成与设计第五章或同样类型的参考资料)

AXI对于Cache支持使用了AWCache和ARCache这两个信号,分别都是4bit,每个比特的含义如下所示。

AXCACHE[0]用来区分是Bufferable还是Non-bufferable,Bufferable即这笔Transaction是否可以存在于Buffer中,比如我要往某个地址写个数据,我是否必须真正的写在了那个地址,然后收到了response才算传输结束,还是写到Buffer中,收到了Response就算结束。

对于写外设操作而言,一般是不允许Bufferable的,因为你没有写入外设的寄存器,外设没有按照你的预期产生工作状态的改变,你就认为传输结束了,是不符合预期的。只有写一些数据的时候,比如计算的中间结果,这个时候对你写在哪里不太敏感,是允许Bufferable的。一般该信号只用在写上,因为读的时候该Buffer可能已经被覆盖掉了,不是想要的值了,当然也不绝对,看你的设计和替换方式是怎样了。

AXCACHE[1]用来区分是Cacheable还是Non-Cacheable,在AXI4中更改为Modifiable,这个Modifiable实际上更加好理解,并且更加准确。官方手册的说法是该比特用于决定实际的传输事务和你原本的传输事务必须是否相等,这么听起来可能有点抽象,以下是具体的实例。

以写为例子,比如你第一次是往地址0写,第二次是往地址1写,如果是Cacheable的,系统检查这两个地址的内存属性又是一样的,那么它就可以把你的写Merge到一起。

以读为例子,也就是可以进行指令预取(读一片指令),也可以进行多个transaction合并(比如连续几个连续的DDR空间)。该比特需要和AXCACHE的[2][3]bit一起使用。如果不是Cacheable的,那么代表不能分配Cache,那么[2][3]bit是没有任何意义的。所以严格来说其既是Cacheable信号又是Modifiable信号。

AXCACHE[2]和[3]用来分别表示读分配和写分配,所谓的分配指的是我们什么情况下应该为数据分配cache line。cache分配策略分为读和写两种情况。当AXCACHE[2]为高的时候,代表需要读分配。如果读分配为高的话,AXCACHE[1]必须为高,因为你都不准Cacheable了,那自然不存在分配了。写分配也是同理。

读分配的含义是,如果是一次读传输,发生了miss,那么应该在cache中给它分配相关的Cacheline,这个过程叫做Cacheline fill,如下图所示。

当写Cache Miss的时候,才会考虑写分配策略。当我们不支持写分配的情况下,写指令只会更新主存数据,然后就结束了。当支持写分配的时候,我们首先从主存中加载数据到cache line中(相当于先做个读分配动作),然后会更新cache line中的数据,如下图所示,当出现写Cache Miss的时候,会先从主存加载数据到Cacheline,然后将要写的那一部分更新到Cacheline相应的位置(图中先Cacheline fill,然后写那个蓝色长方形的灰色格子)。

以下是该4bit可能的编码组合:

AXI还有信号和原理,我们慢慢讲,多学习,2025年国庆节快乐。