Giants Shoulder - Hyrix: LPDDR5 Commands New Features

带你看巨人视角下的LPDDR!

本期文档是来自海力士的: LPDDR5 Commands & New Features

2019年的文档,回顾下LPDDR5诞生之初时的技术更新,对比如今的LPDDR6可以看到一些技术发展的侧重点。

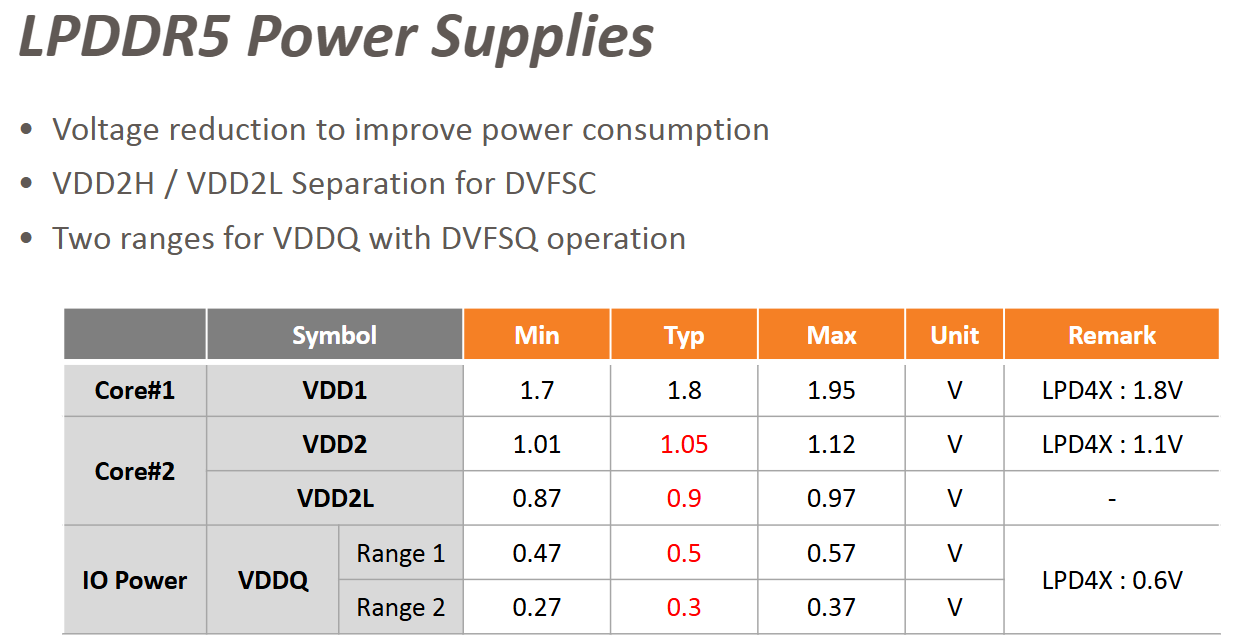

首先是供电:

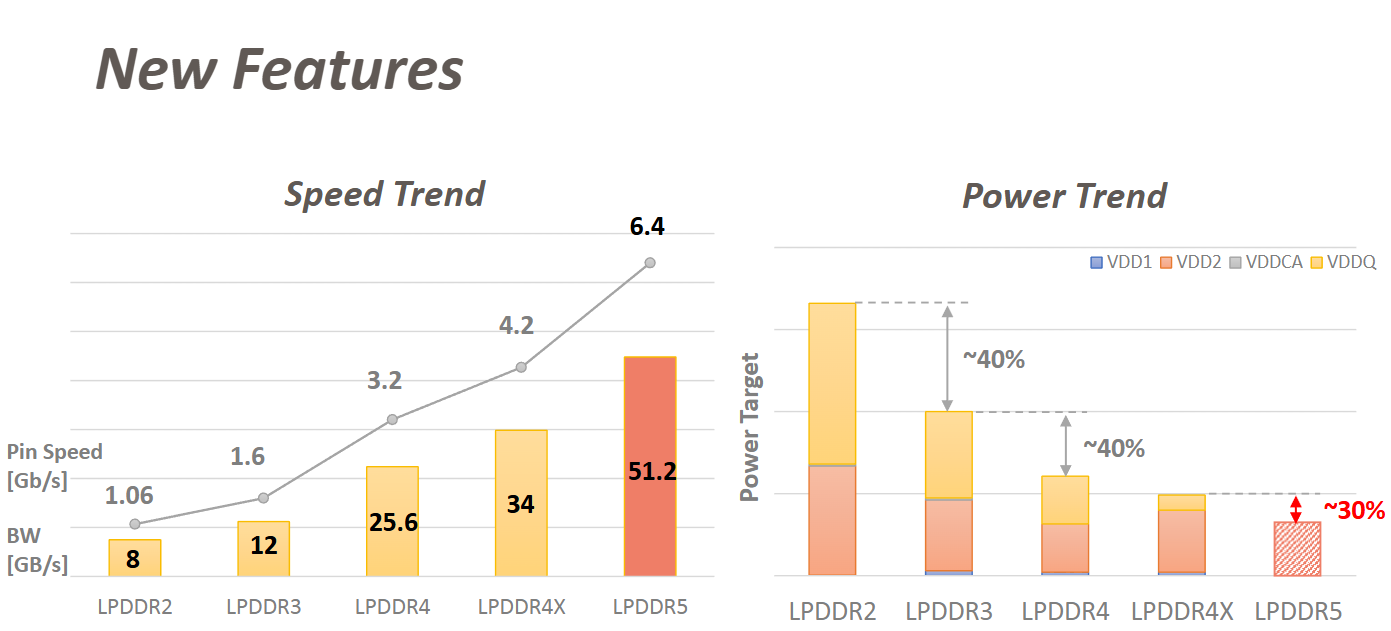

可以看到LPDDR新一代迭代的时候,最重要的就是LP。相比上一代如何降低功耗一直是LPDDR技术的重中之重。

对比LPDDR4,LPDDR5首次采取了VDD2的Dual Power Rail Supply技术,而这种双轨供电也在LPDDR6上得到了延续。

这里再次解释下为什么只有VDD2做了双轨供电,首先需要知道的是LPDDR4以及之前的规范上VDD1, VDD2, VDDQ的供电对象不相同。

VDD1是面向DRAM内部核心Core的供电,类似控制逻辑、地址解码、状态机等核心逻辑功能,都通过VDD1供电。

VDD2是面向 Periphery + CA供电,所有外围电路以及CA信号线,都通过VDD2供电。

VDDQ是面向命令数据I/O供电,类似DQ, DQS等信号线,都通过VDDQ供电。

所以我们可以分析出来,VDD1电压如果增加多轨供电来切换,这种核心逻辑频繁切换电压会增加设计复杂度和稳定性风险。

如果频繁切换VDDQ电压,可能导致DQ信号完整性问题和 PHY 设计复杂度大幅增加。数据通道对时序和抖动敏感,保持固定电压更可靠。

Dual Power Rail 只用于 VDD2,是因为VDD2L的设计只面向部分外围电路以及CA接口,切换电压对性能影响小、功耗收益大。

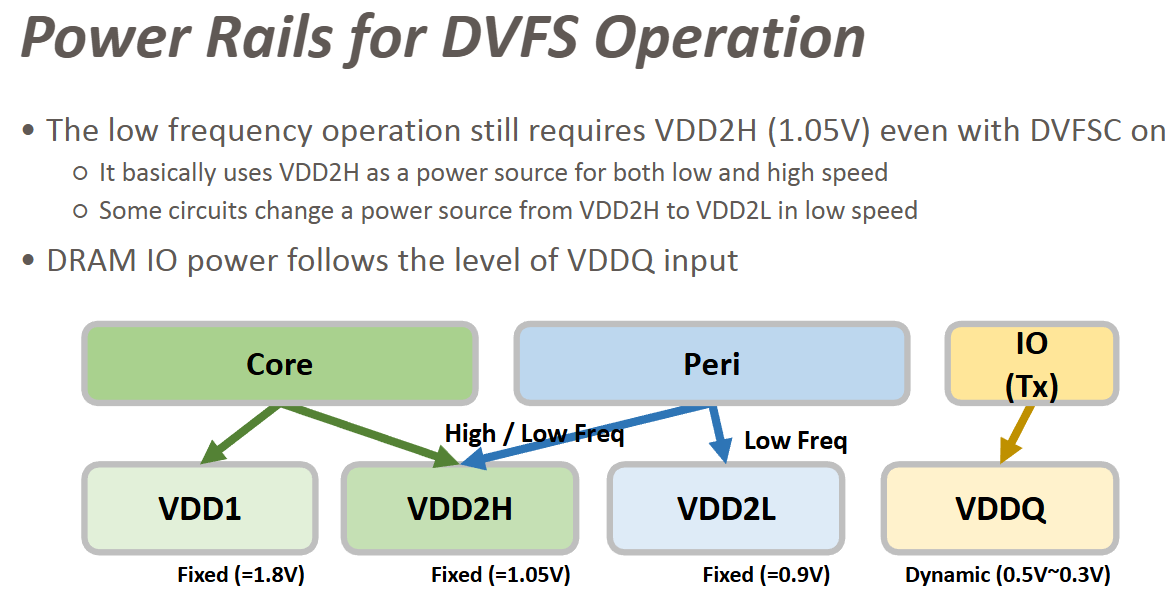

提到了双轨道供电,就不得不提到LPDDR5提出的DVFS技术:

可以看到在供电方案上,对比LPDDR4,除了VDD1和VDDQ依旧给Core和I/O供电之外, VDD2拆分出:

VDD2H不论高低频都给Core和外围电路供电。

VDD2L则是在低频下给部分外围电路供电。

这里除了VDD2L能够在低频模式下节省外围电路的功耗之外,还有Core的供电变成了VDD1+VDD2H的模式,部分内部核心供电功耗可以有效降低。

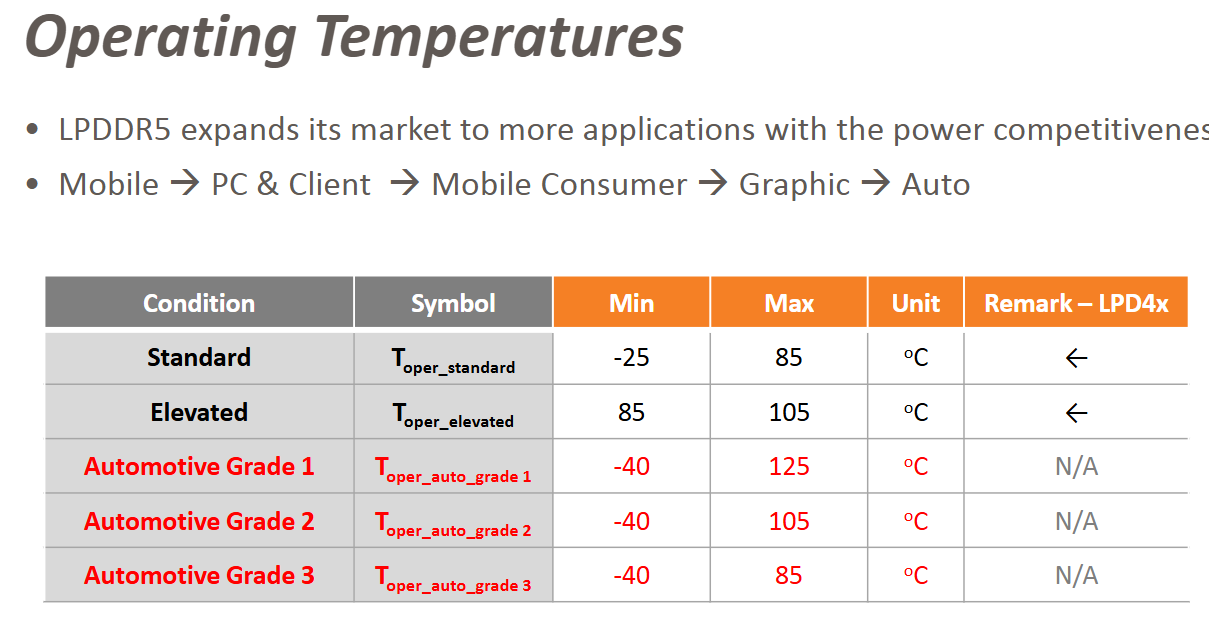

再就是LPDDR5相比LPDDR4的工作温度范围变化:

可以看到随着AI/大数据/电车行业的兴起,LPDDR在PC/图形/汽车相关的领域开始扩大了市场。

这里的表格也表明了相比LPDDR4,5代技术需要配合车载的需求,扩大工作温度范围,最低零下40度,最高125度。

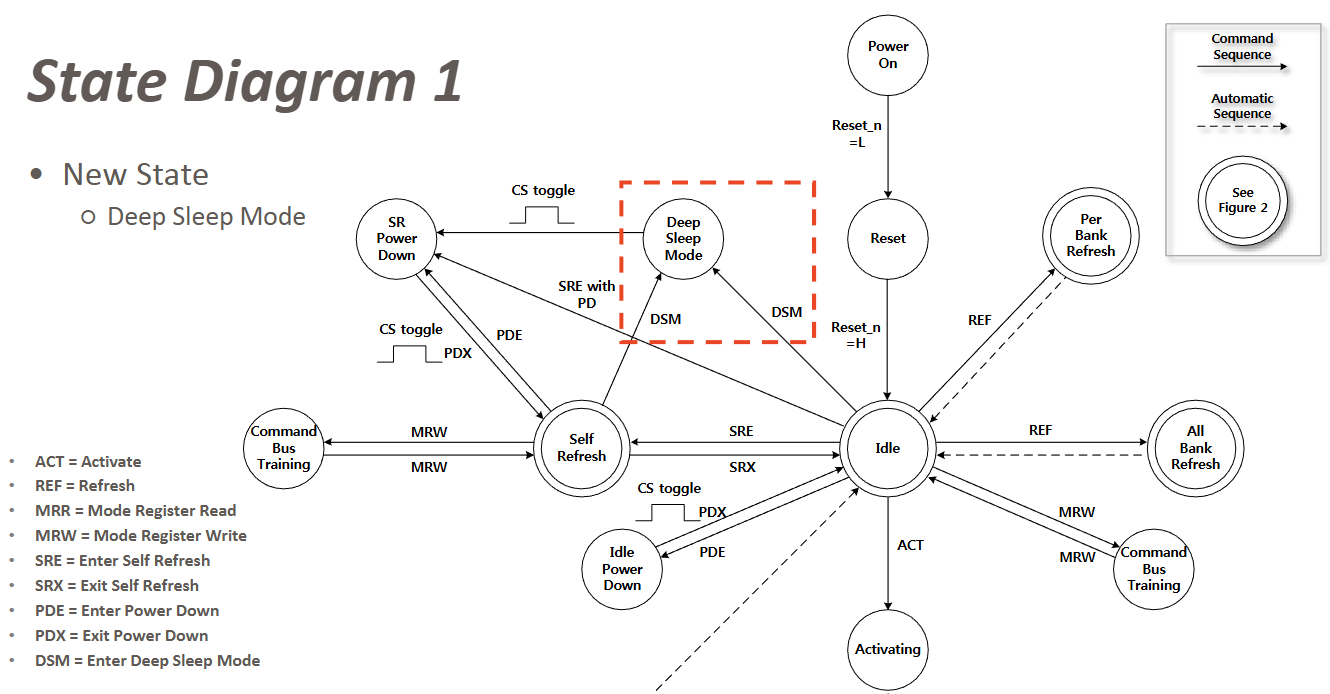

接下来是状态机的更新:

依旧围绕低功耗功能,提出了Deep Sleep Mode,可以从SR状态或者IDLE状态切换,适用于长时间没有来自外部访问时的场景。

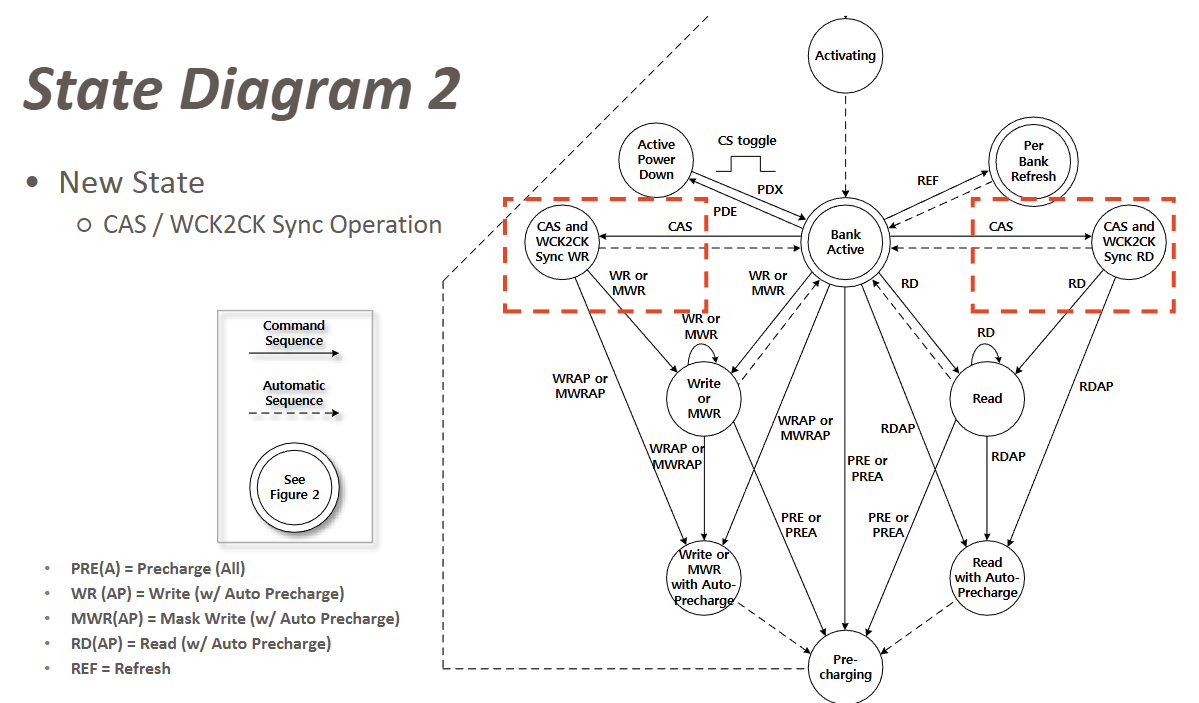

再就是CAS/WCK2CK的Sync:

因为取消了LPDDR4的DQS,Read和Write在LPDDR5上各自更换为RDQS和WCK的独立Strobe信号,所以这部分肯定是需要作Sync的。

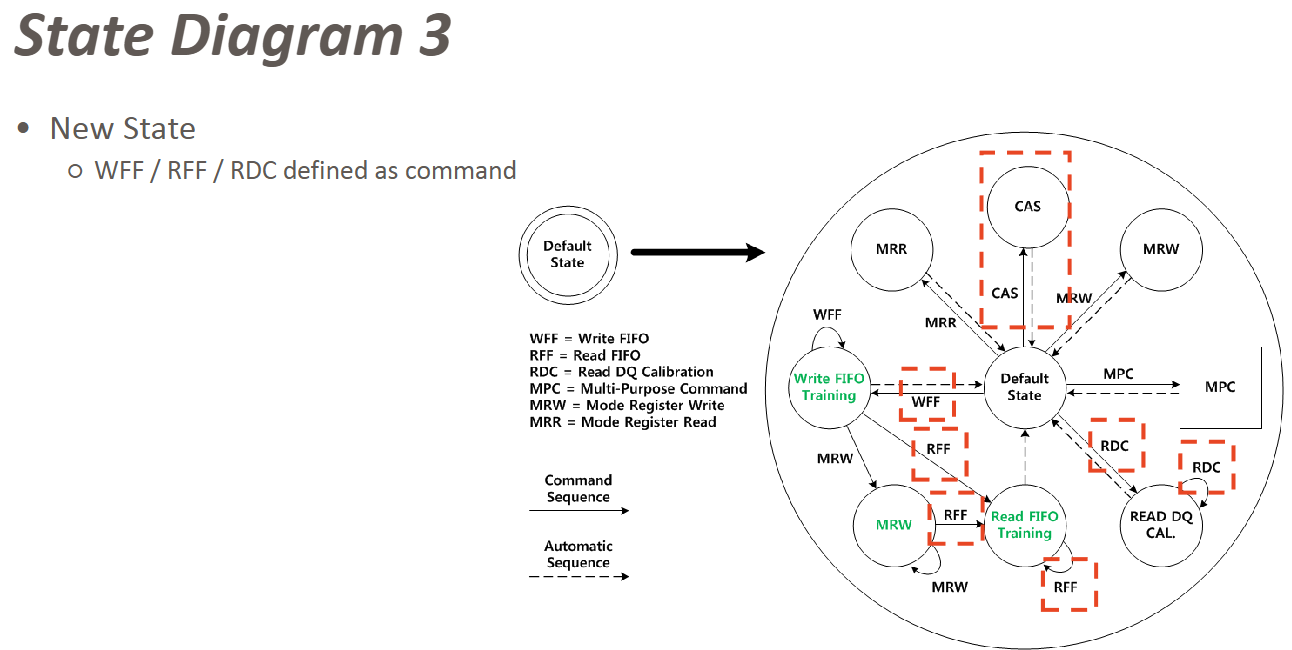

下一页是WFF/RFF/RDC命令的出现:

解释一下,WFF - WRITE FIFO,RFF - READ FIFO,RDC - Read DQ Calibration,这些都是LPDDR4通过MPC命令实现的。

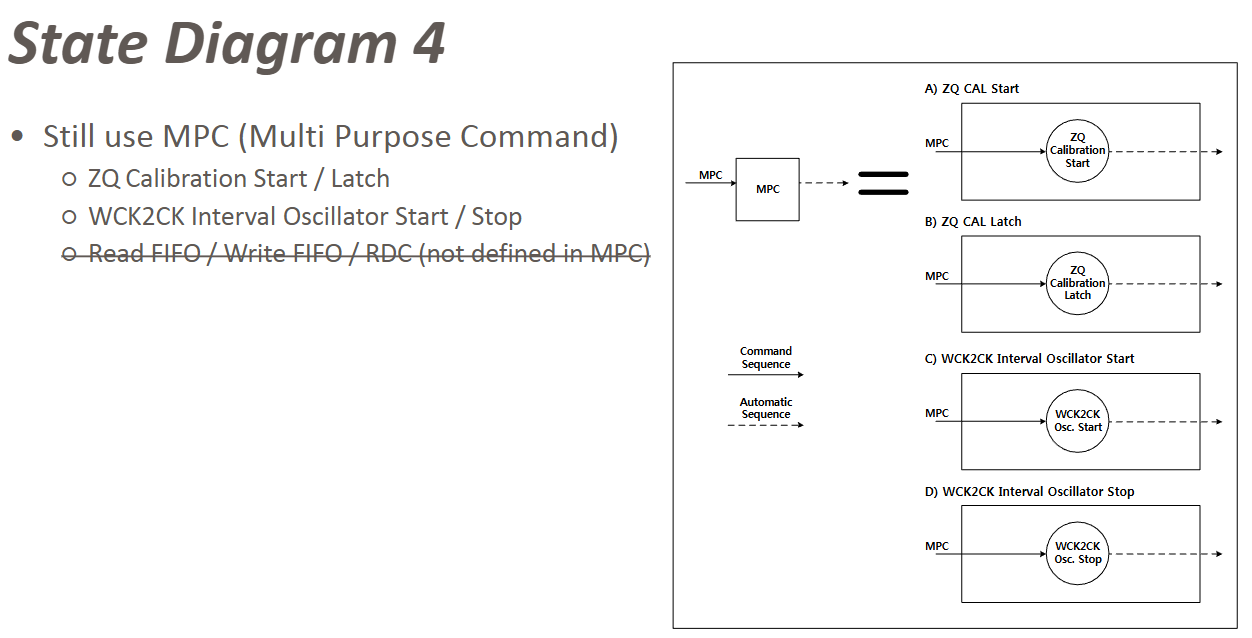

在LPDDR5都有了各自专属的Truth Command。而LPDDR5的MPC则是有了如下的更新:

为了服务WCK2CK,增加了WCK2CK的内部振荡器开关命令,取消了LPDDR4的Read DQ Cali和FIFO命令,由LPDDR5专属的命令替代实现。

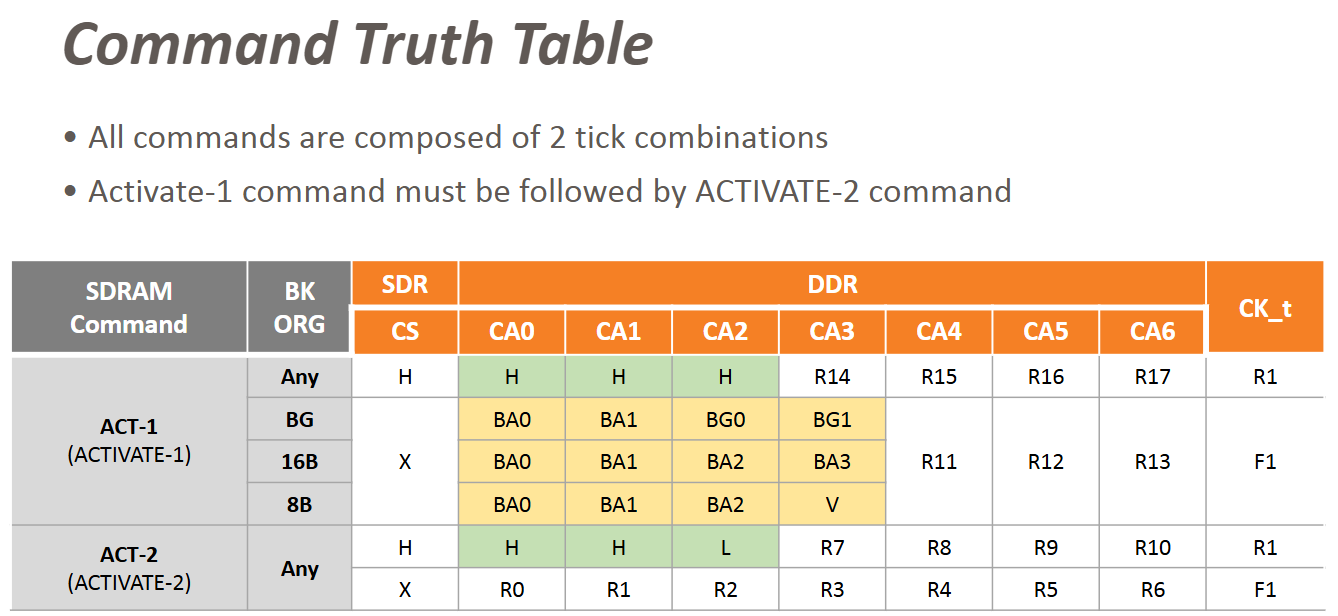

接下来的内容是围绕Command Truth Table展开,主要就是LPDDR5因为支持了8B/16B/BG这三种不同的Bank架构,导致不同架构下的部分命令组成是不同的:

主要是因为在不同Bank架构下,可以访问的DRAM空间深度是不同的,像BG模式下必须指定Bank Group,8B模式下只需要提供Bank Address信息。

看这一页就可以明白同一个ACT-1命令,CA0/CA1/CA2/CA3在CK下降沿所代表的意义是不同的。

其他类似受到Bank架构影响的命令还有很多,可以自行参考JESD标准中的Command Truth Table信息。

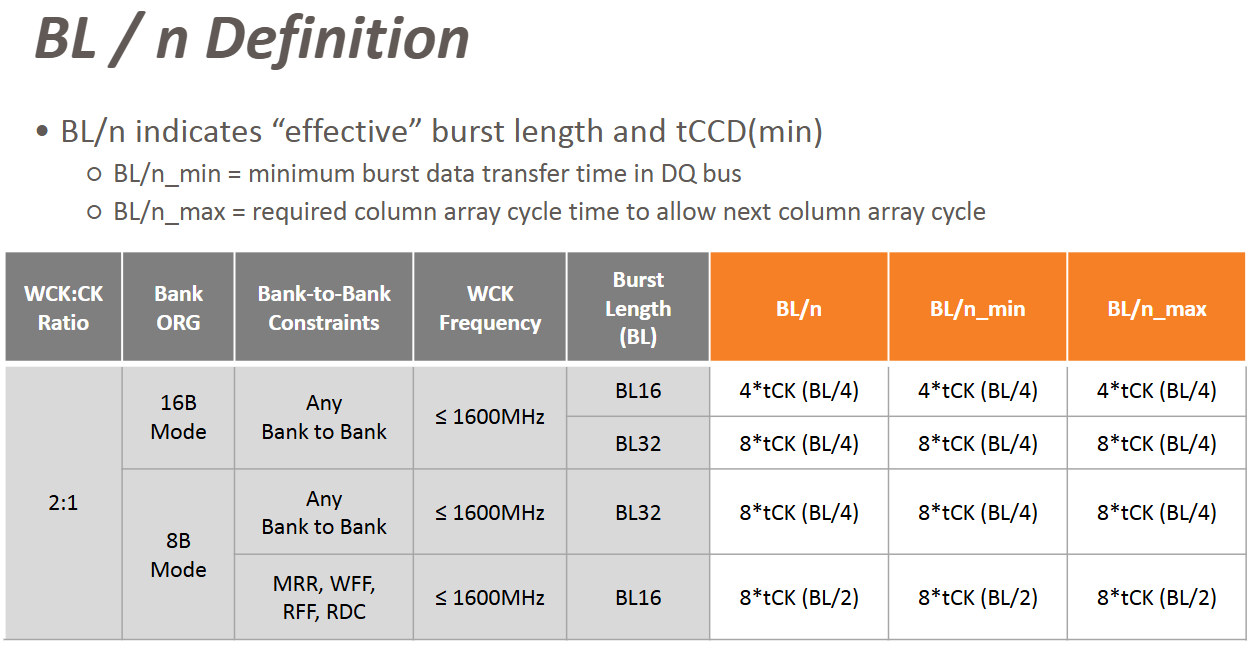

下一页是BL/n的定义:

这里解释一下,BL/n 表示“有效突发长度”(Effective Burst Length),它不仅代表了DQ数据传输的最小时间,也限制了column之间切换的最大时间。

除了BL的信息,还包括了tCCD(min):Column-to-Column Delay,即两次列访问之间的最小间隔时间。

对于应用层面来说,BL/n也就决定了当前的R/W数据传输命令通过Burst发送后,最少需要等待多久,才能发送下一个BL命令。

突发长度越大,两个命令之间的最小间隔也越长,从而影响总线的利用率和命令调度。

BL/n这里的n参数就是不同速率下,单次Burst传输中每个CK周期传输的数据量。

以上图为例:在16B模式下,2:1 CK ratio,BL为BL16并且WCK频率在1600MHz以下时;

每个CK周期内,有2个WCK,也就有4个WCK上下边沿来一共传输4个数据单位,所以n为4;

因为BL16是Burst Length为16Bits的数据长度,每个CK传输量为4,所以BL/n = 16/4 = 4*tCK;

因为不涉及Bank Group切换,所以BL/n_min和BL/n_max同是相同的。

需要注意的是,8B模式并不支持BL16的Data数据传输,这里的BL16只是给MRR/WFF/RFF/RDC这类命令提供了BL16的低数据量传输方案。

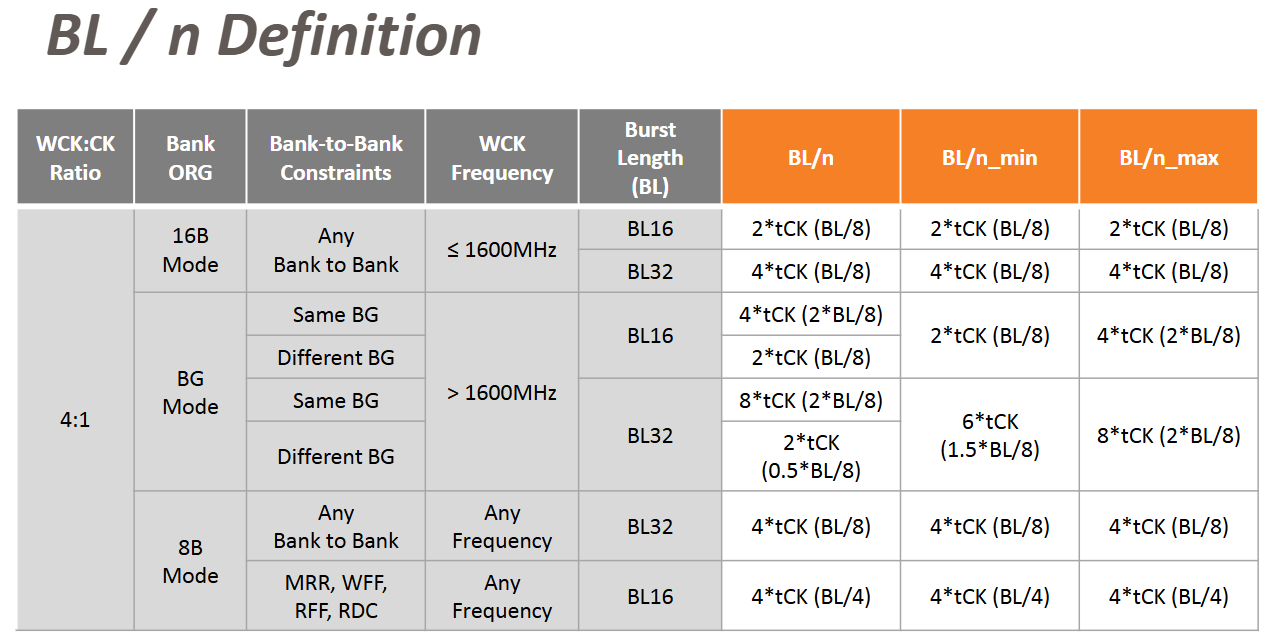

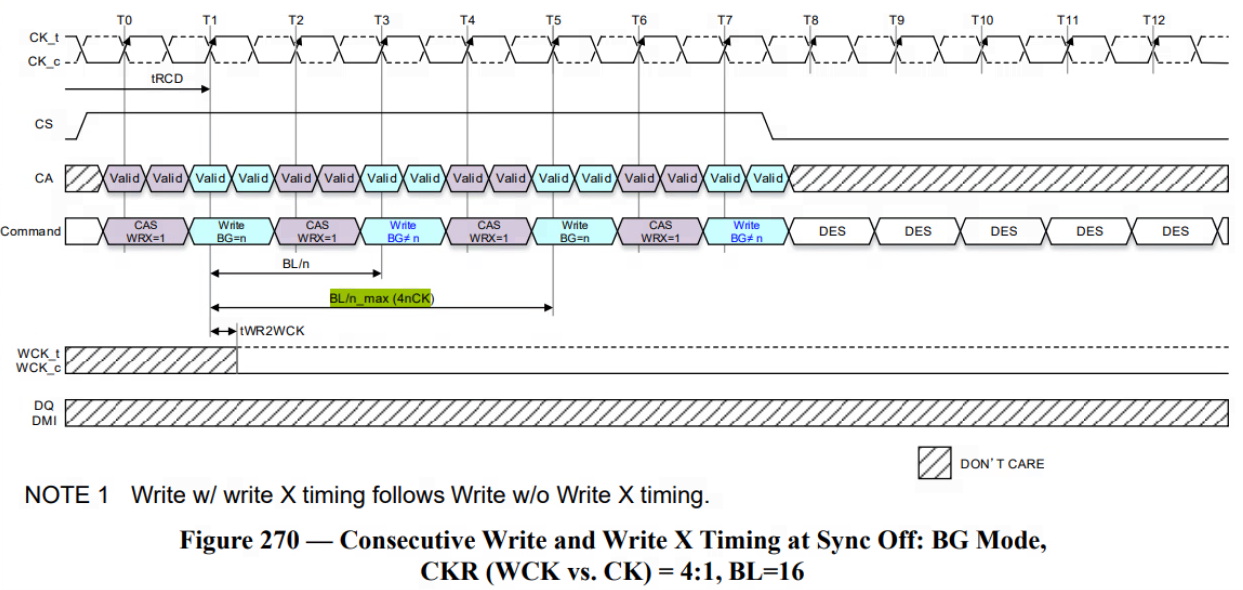

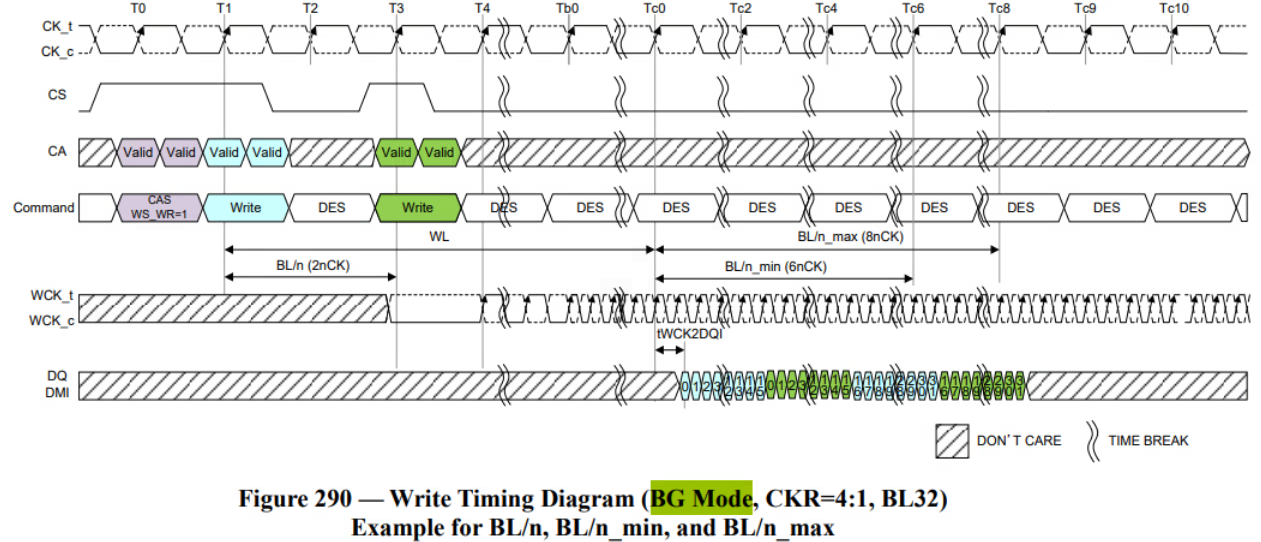

倘若考虑BG mode下切换Bank Group的开销,可以参考下面这一页:

如下图所示,BG模式下BL16会出现(2 * BL/8), 是因为在BG模式下,如果是不同BG,BL/n就可以参考16B模式,类似于独立访问。

BL/n如果面向同一个Bank Group,最坏情况可能中间插了一个其他BG的,所以同一BG之间需要预留4nCK的周期。

BG模式的BL32会出现(0.5/1.5/2* BL/8), 是因为BG模式的BL32是通过两个BL16交织实现。

如下图所示,BL32模式下,Command需要给两次Write,DQ Pin上是交替传输4次BL16的数据。

结合上图就可以比较清晰的看出来,如果是淡蓝色的Write数据通过BL32传输,那么只需要6nCK (1.5BL/8)的时间,不需要等待另外一笔16bit数据传输结束。

但如果是绿色的Write数据,就必须先等淡蓝色的第一笔16Bits数据传输完毕,导致最终整个周期是8nCK (2BL/8)的时间。

那为什么BG模式下,BL32的BL/n是2tCK (0.5BL/8)而不是6tCK (1.5BL/8)?

我的理解是,这里的BL/n这一列参数指向的就是最少需要等待多久才能发送下一个Command的限制,而BG mode的BL32还是由BL16构成,所以这里的Different Bank的BL/n和BL16场景下的一样。

而BL/n_min和BL/n_max更偏向于是一笔完整的数据发送完需要的最短/最多时间。

下一页宏观地介绍了历代LPDDR最为注重的速率和功耗的变化趋势:

再往后就是Low-Power和Channel相关的技术更新,包括了Data Copy/Write X/Link ECC/RDQS Toggle

大部分内容在之前的文章中都提及过,可以点击跳转浏览 LPDDR5 Updates

这里主要分享下之前没有提过的RDQS相关内容:

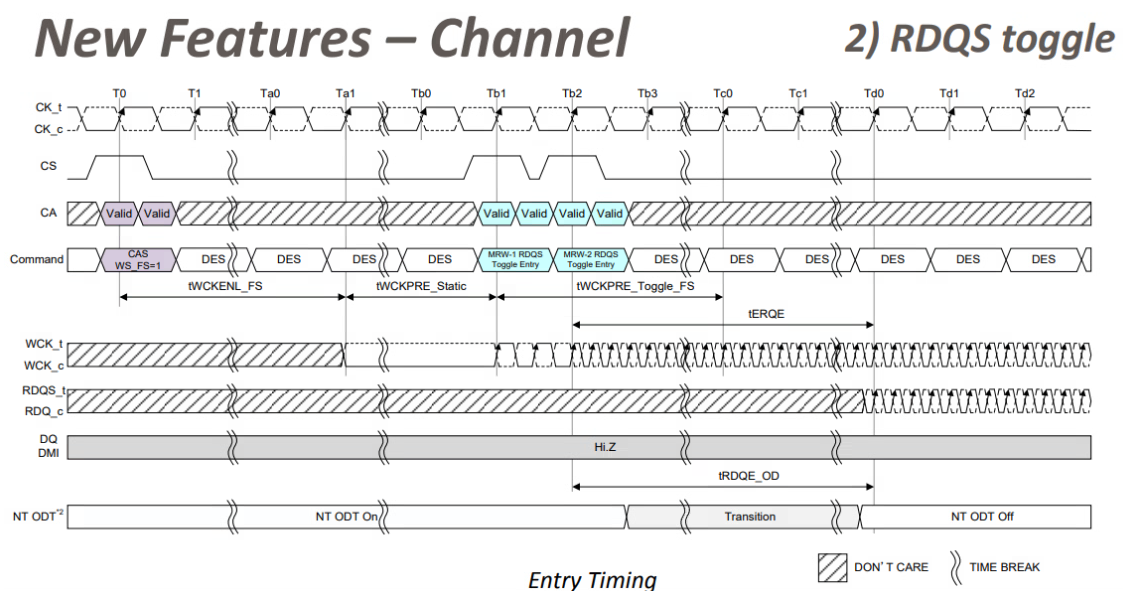

先是RDQS Toggle,由MR46 OP[1]控制这项功能开关。

目的也就是为了在高频下,通过反复调整delay,让PHY能够采样到和CK/WCK边沿对齐的RQDS信号。

至于RDQS信号本身是单端还是差分,还是根据MR20 OP[1:0]决定。并且在RDQS Toggle期间WCK也必须先于RDQS维持Toggle。

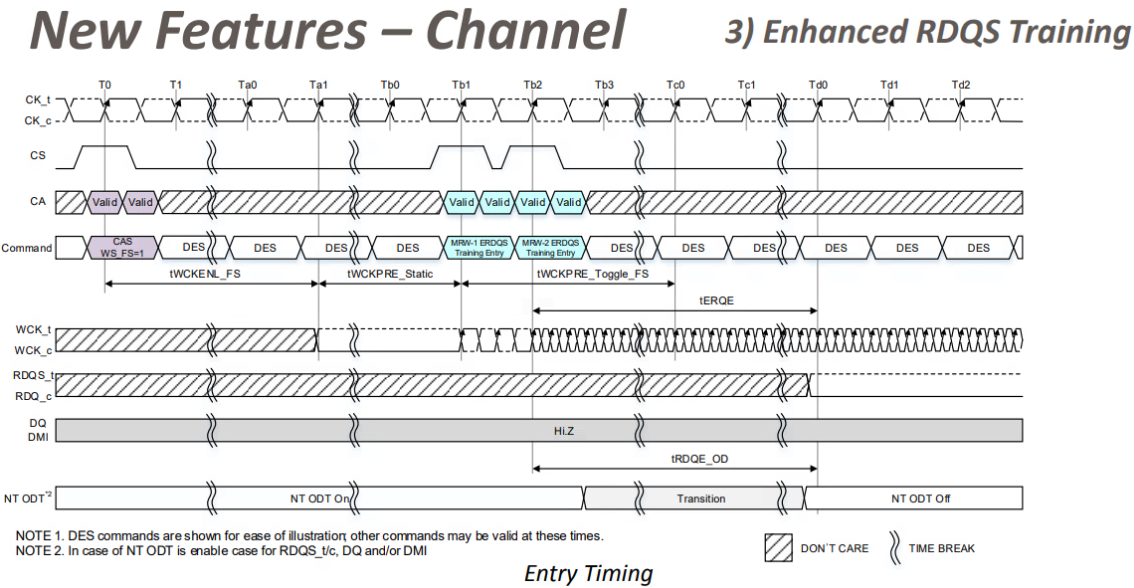

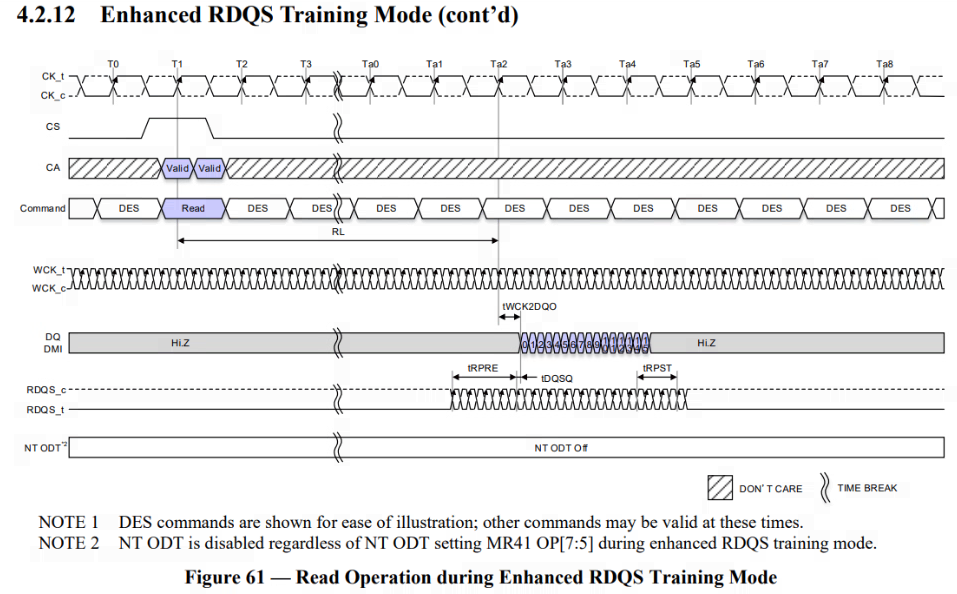

再是RDQS的Enhanced Training:

由MR46 OP[0]控制这项功能开关。

和RDQS Toggle的目的类似,都是为了PHY能够有一个合适的Read Gate Timing,读到稳定的RDQS。

不同的是这里不再需要RDQS一直Toggle,并且中间还能穿插Read命令,更加灵活。

上面两个RDQS的内容也可以参考此篇文章DDR Study - LPDDR5 Read Gate Training

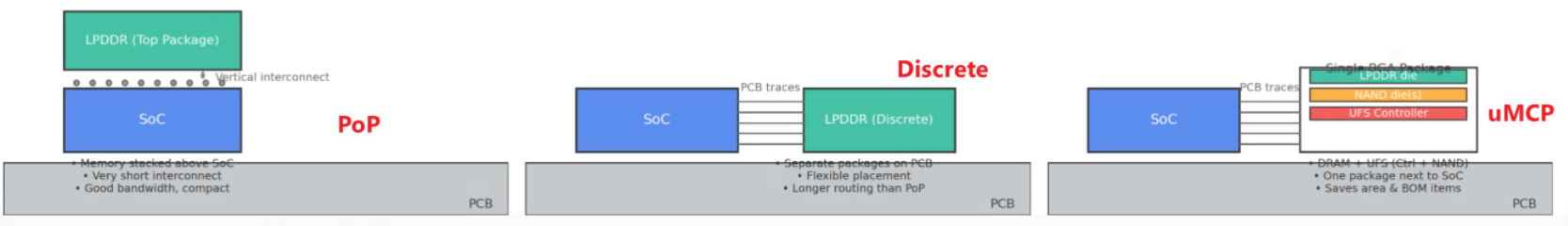

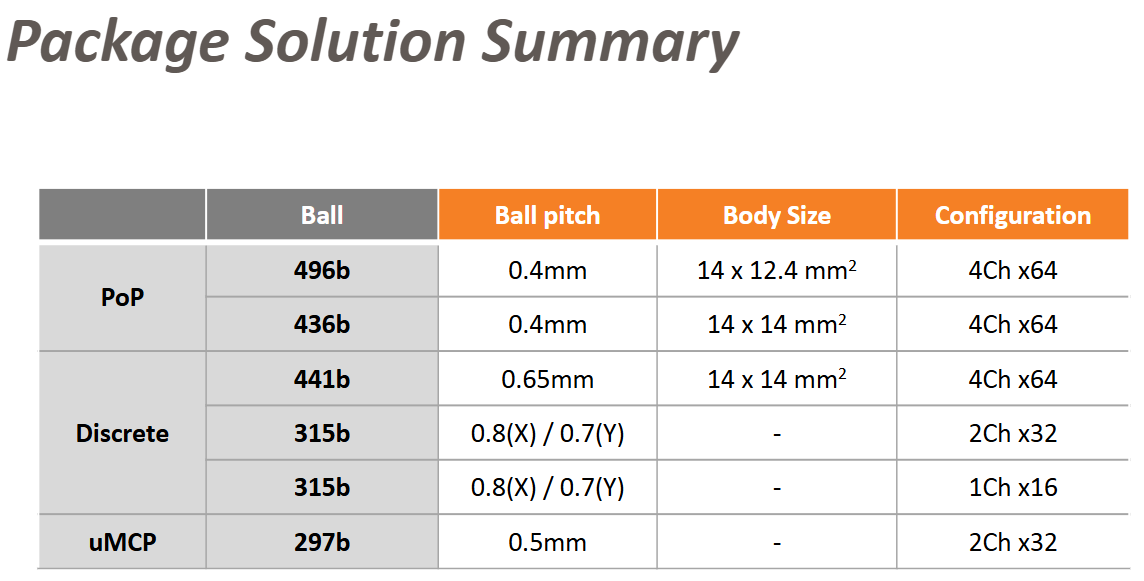

最后是Package相关的更新,从PoP,Discrete和uMCP三个封装的布局介绍:

这里也简单介绍下这三种封装的区别: