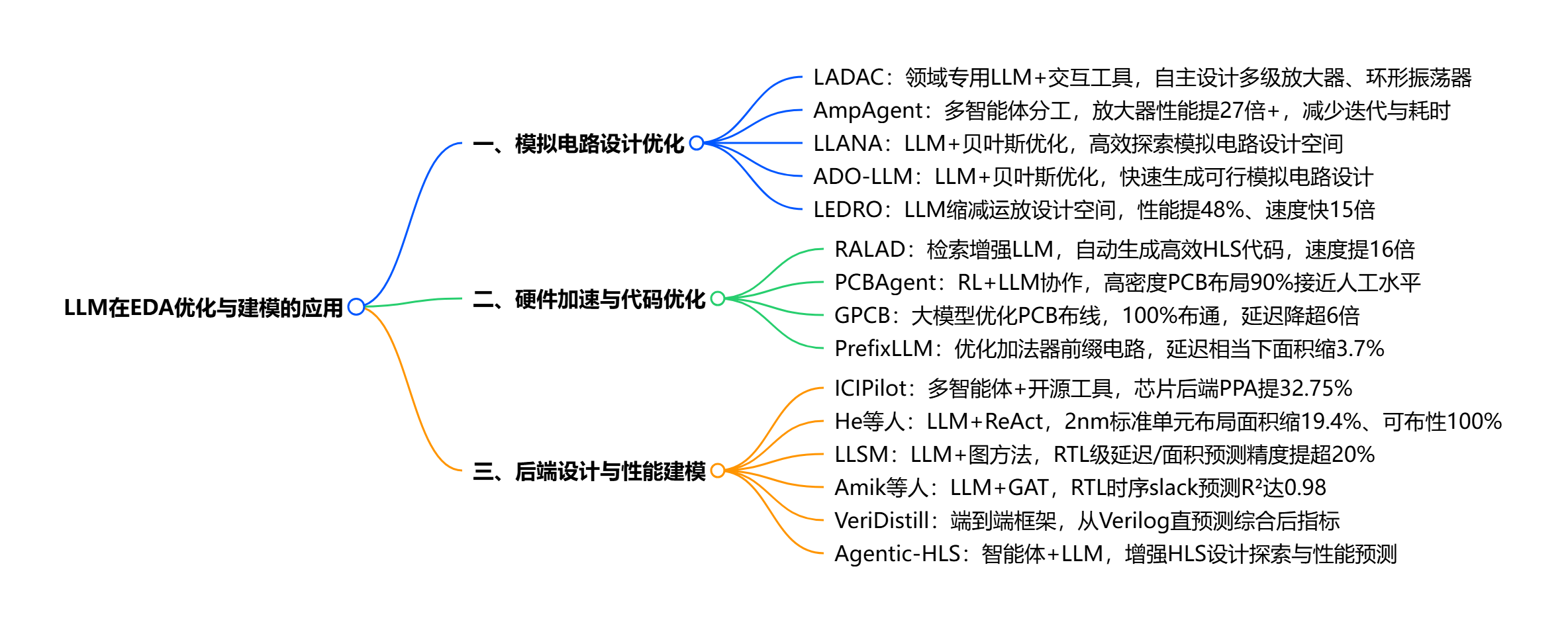

【LLM4EDA】: Part 9--LLM4EDA的优化与建模

在上一篇文章中,我们了解到了LLM4EDA在领域基础模型、规范生成和评审、问答系统和BUG分析四个方面的部分工作。接下来我们将从LLM4EDA的优化与建模相关研究。

本文内容

介绍部分LLM4EDA研究在优化与建模方面的工作、突破、挑战和机遇。

LLM4EDA的优化与建模

优化和建模利用LLMs的高级推理和生成能力来增强传统的EDA工作流程。这些任务包括使用LLMs来帮助控制电路参数、探索设计取舍,以及生成预测系统行为的有效模型。例如,LLMs可以通过分析设计约束、生成优化策略或自动执行迭代过程来帮助优化功耗、性能和面积(PPA)指标。此外,它们还可以帮助创建高级抽象或代理模型来表示复杂系统,从而实现更快的模拟和评估。通过将LLM集成到优化和建模工作流中,工程师可以在应对现代EDA挑战的过程中受益于改进的自动化、可扩展性和决策。

一、模拟电路设计优化

这类研究聚焦模拟电路(如放大器、振荡器等)的自动化设计与参数优化,利用 LLM 的推理、生成能力突破传统方法的效率瓶颈。

-

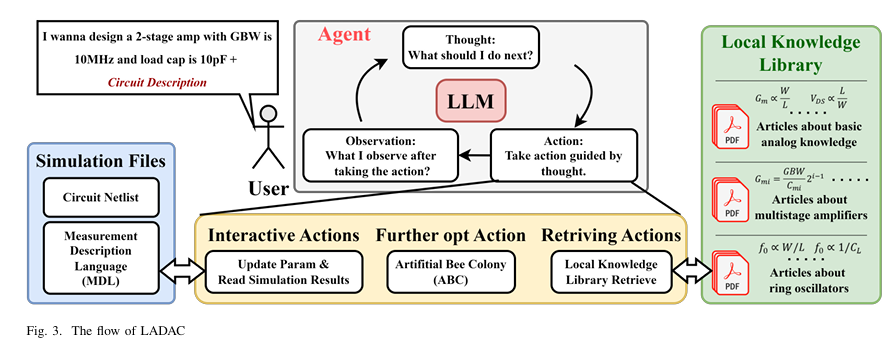

LADAC 给 LLM 配备 “模拟电路领域专属知识库 + 交互工具”,让它像资深工程师一样,根据设计需求自动调整晶体管尺寸,还能完成 “两级放大器、多级特殊放大器、环形振荡器” 等模拟电路的设计。

-

AmpAgent 用 “文献分析、数学推理、器件尺寸调整” 三个智能体分工协作,一起设计复杂的多级放大器。比如 “文献分析智能体” 找资料里的关键信息,“数学推理智能体” 推导公式拆分设计难题,“器件尺寸智能体” 结合仿真工具确定放大器的参数,最终让电路性能提升 27 倍多,还减少了设计迭代次数。

-

LLANA 把 LLM 和 “贝叶斯优化(一种智能找最优解的方法)” 结合,利用 LLM “学东西快” 的特点,让贝叶斯优化更高效地探索模拟电路的设计空间,生成或优化模拟版图的约束条件(比如元件怎么摆才合理)。

-

ADO-LLM 同样是 LLM + 贝叶斯优化,但更强调 “快速生成靠谱的设计方案”。先让 LLM 根据电路定义、需求生成初始设计点,用仿真工具评估后,再把结果反馈给 LLM 优化,让整个贝叶斯优化过程更聪明。

-

LEDRO 让 LLM 帮着缩小模拟电路的 “设计范围”(因为模拟电路设计变量太多,直接找最优解很慢),再用优化算法高效探索。在 22 种运放拓扑、4 种先进工艺下,电路的 “品质因数”(综合性能指标)提升了 48%,设计速度也快了 15 倍。

二、硬件加速与代码优化

这类工作围绕 “高级综合(HLS)代码生成”“印刷电路板(PCB)布局 / 布线” 等任务,用 LLM 提升硬件设计的自动化与效率。

-

RALAD 给 LLM “外挂知识库”(检索外部 HLS 代码示例),让它生成更优的高级综合(HLS)代码。比如要做矩阵乘法,LLM 能参考知识库的优秀代码,自动写出效率更高的 HLS 代码,让任务速度提升 16 倍,代码编译成功率也高了 50%。

-

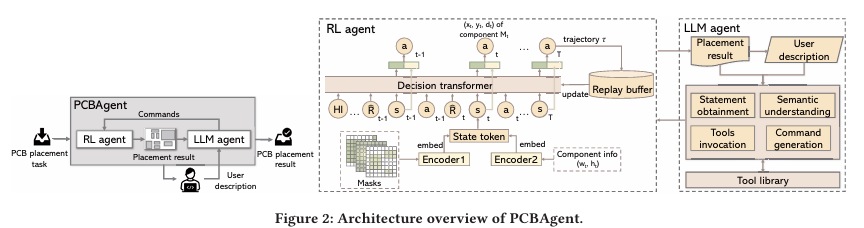

PCBAgent 用 “强化学习智能体(像玩游戏一样找最优布局) + LLM 智能体(理解人类需求、翻译反馈)”,自动优化高密度印刷电路板(PCB)的元件布局。在 17 个工业级 PCB 案例里,布局的 “线长”“表层线利用率” 等指标,90% 能接近人工布局的高质量水平,比传统方法做得好。

-

GPCB 用大模型(类似 ChatGPT 的预训练 Transformer)自动优化 PCB 布线。支持 “多线并行布”,能保证 100% 布通,还让布线延迟降低 6 倍多,速度比现有方法快 6 倍以上。

-

PrefixLLM 专门优化数字加法器里的 “前缀电路”(加法器高效运算的关键部分)。通过 LLM 生成更优的电路结构,在延迟差不多的情况下,电路面积能缩小 3.7%,比经典的 Kogge-Stone、Brent-Kung 等电路设计更省面积。

三、后端设计与性能建模

点击链接【LLM4EDA】: Part 9--LLM4EDA的优化与建模阅读原文