Day05_ARM裸机

ARM裸机

1.存储器

SOC存储器术语

RAM:随机访问存储器

掉电擦除

ROM:只读存储器

掉电不擦除,norfalsh(电擦写)是rom(不可改写)的升级版

SROM:ROM的早期版本

SROM是ROM的静态实现:采用类似SRAM的电路,但牺牲写入能力换取非易失性,已基本被淘汰

IRAM:集成在SoC内部的RAM

IROM:集成在SoC内部的ROM

SRAM:(Static RAM)静态RAM,SRAM只要通电,里边存储的数据就可以恒常保持。(掉电即消失),应用于CPU中的高速缓存Cache中

集成度低(单位面积存储单元稀疏),耗电高,读写极快,成本高

DRAM:(Dynamic RAM)动态RAM,DRAM只能将数据保存很短的时间,为保持数据,DRAM使用电存储,所以必须隔一段时间refresh一次,如果存储单元没有被刷新,存储的信息就会丢失。(掉电即消失)

集成度高,耗电低,读写一般,成本低

SDRAM:(Synchronous Dynamic Access Memory)同步动态随机访问存储器。同步指的是内存工作需要同步时钟。广泛应用于DDR4,DDR5等,已逐步替代DRAM

集成度高,耗电中(需时钟同步),读写一般,成本低

特性 SRAM DRAM SDRAM 存储结构 6管触发器 💾 1管1电容 💾 1管1电容 + 同步时钟 ⏱️ 数据保持 无需刷新 需每2ms刷新 ⚠️ 需刷新(异步策略优化) ⚠️ 读写延迟 1-10ns ⚡ 50-100ns 🐢 50-70ns(同步优化) ⚡ 集成度 低(10⁶ bits/mm²) 高(10⁷-10⁸ bits/mm²) 同DRAM,更高密度(3D堆叠) 成本 高($10-20/Gb) 💰 低($1-3/Gb) 💰 中等($2-5/Gb) 💰 功耗 高(触发器持续工作) 🔥 低(仅刷新时耗电) 🔋 中等(同步电路增加功耗) 🔋 典型应用 CPU高速缓存(L1/L2 Cache) 🚀 早期内存条、低端嵌入式系统 💾 现代内存条(DDR4/DDR5) 🖥️

- NOR FLASH:非易失闪存技术,intel1988年开发。

- NAND FLASH:非易失闪存技术,东芝1989年开发。

- ONENAND:三星推出的NAND

- iNand:SanDisk推出的NAND

SoC常用外部存储器

NorFlash/NandFlash

NorFlash:1988年intel开发的非易失性存储技术,可以总线式访问,接到SROM bank,一般用于启动。

NandFlash:1989年东芝开发的非易失性存储技术(分为SLC和MLC。SLC容量不大,稳定性好,价格高;MLC容量很大,容易坏块,价格低,必要ECC校验)

Nor和Nand的区别:

NorFlash的特点是芯片内执行(XIP,eXecute In Place),用户可以直接运行装载NorFlash里边的代码。这样可以减少SRAM的容量从而节约了成本。

Nor的传输速率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。

NandFlash的读取是以一次读取一块的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价。

NandFlash内部采用非线性宏单元模式,为固态大容量Memery的实现提供了廉价有效的解决方案。

CPU不能直接运行NandFlash上的代码,因此好多使用NandFlash的开发板除了使用NandFlash以外,还作上了一块小的NorFlash来运行启动代码。

eMMC/iNand/moviNand:(本质仍是nandflash)

eMMC(embeded MMC 嵌入式MMC卡)

iNand是SanDisk出的eMMC

moviNand是三星出的eMMC

eMMC在高端市场被UFS替代,低端市场因eMMC的稳定性仍占有一部分市场(嵌入式等场景)

oneNand:

oneNand是三星出的Nand

SD卡/TF卡/MMC卡:

MMC卡:早期的一种存储基础,基于narflash,部分基于nandflash,现已淘汰

SD卡/TF卡/SSD/UFS/eMMC:均是基于nandflash的存储技术

SSD&UFS&TF卡的关系

SSD、TF卡(Micro SD卡)和UFS都是基于NAND Flash闪存技术的存储设备,但它们在设计目标、性能和应用场景上有显著差异。以下是三者的核心关系与区别对比:

一、技术本质与共性

共同基础

三者均使用NAND Flash闪存颗粒作为存储介质,属于非易失性存储器(断电后数据不丢失)。

核心差异

- 控制器与接口:SSD和UFS采用高性能控制器和复杂接口协议(如PCIe/NVMe、UFS串行接口),支持高级功能(如磨损均衡、错误纠正);TF卡控制器较简单,接口标准(如SD协议)更侧重成本控制。

- 结构设计:SSD通常集成多颗闪存芯片并行操作以提升速度;UFS和TF卡多为单芯片设计,但UFS通过高速串行接口实现高性能。

二、关键特性对比

特性 SSD(固态硬盘) UFS(通用闪存存储) TF卡(Micro SD) 主要应用 💻 电脑、服务器、数据中心 📱 高端手机、平板、嵌入式设备 📷 手机扩展存储、相机、行车记录仪 接口/协议 SATA、PCIe/NVMe UFS 2.0/3.0/3.1(串行全双工) SD/UHS-I/II(并行半双工) 传输模式 全双工(读写同时进行) 全双工(读写同时进行) 半双工(读写不能同时) 速度 读写500MB/s~7GB/s(NVMe) 读写500MB/s~1.2GB/s(UFS 3.1) 读写10~300MB/s(UHS-III) 容量 128GB~8TB+ 32GB~1TB 8GB~2TB 功耗与体积 功耗较高,体积较大(2.5英寸/M.2) 低功耗,芯片级封装(直接焊接) 超低功耗,极小尺寸(15×11×1mm) 价格(同容量) 中等(NVMe > SATA) 较高(高端移动设备专用) 低(普及型扩展方案) 三、性能与场景适配

- SSD

- 优势:超高速度和并行处理能力,适合操作系统、大型软件加载及数据中心高频读写。

- 局限:体积和功耗限制其在移动设备的直接应用。

- UFS

- 优势:手机内置存储的理想选择,全双工和低延迟支持多任务与4K视频录制。

- 局限:成本较高,且需直接焊接在主板上,无法像TF卡灵活更换。

- TF卡

- 优势:极致便携和低成本,适合存储照片、音乐等非核心数据。

- 局限:速度和可靠性较低,频繁写入易损耗(无高级纠错机制),不适合安装系统或高频应用。

四、总结:关系与定位

- 技术演进:UFS可视为移动端的高性能替代方案(取代eMMC和部分TF卡场景),而SSD是PC/服务器领域的标杆。

- 互补性:高端手机可能同时采用UFS(内置系统存储) + TF卡(扩展用户数据);SSD则独立服务于计算密集型场景。

- 未来趋势:UFS持续提升速度(接近入门级SSD),而TF卡在速度瓶颈下主要定位低功耗扩展存储。

💎 一句话概括:三者本质都是闪存存储,但SSD主打高性能计算,UFS专注移动设备内核,TF卡则胜在便携扩容,共同覆盖了从数据中心到口袋设备的全场景存储需求。

eSSD

企业级固态硬盘

SATA硬盘

(机械式访问、磁存储原理、SATA接口)

2.ARM架构SoC启动过程

ARM架构SoC(System on Chip)的启动过程是一个从硬件上电到操作系统完全初始化的复杂流程,涉及多级固件、引导程序和内核的协同工作。以下按启动顺序详细解析各阶段的核心步骤与技术细节:

一、电源上电与复位(Power-On Reset)

- 硬件复位 电源接通后,SoC的复位电路触发硬件复位信号,强制所有逻辑单元(CPU核心、外设等)回到初始状态。

- 执行BootROM代码 CPU主核(通常为Cortex-A系列)从固定地址(如

0x00000000)开始执行芯片内置的BootROM代码。此阶段完成:

- 基础硬件初始化:配置时钟控制器、看门狗定时器、中断控制器等。

- 启动设备选择:根据Strapping GPIO引脚电平或熔断器(Fuse)设置,确定启动介质(如eMMC、SD卡、SPI-NOR)。

- 加载下一级固件:从启动介质读取二级引导程序(如SPL或BL2)到SRAM中。

二、初级引导阶段(BootROM → SPL/BL2)

- SPL(Secondary Program Loader)的作用

- 初始化关键外设:如DDR内存控制器、串口调试输出。

- 加载完整Bootloader:将U-Boot等主引导程序从存储设备拷贝至DDR内存(需先初始化DDR)。

- 小内存系统的优化:若SRAM空间不足,可能引入TPL(Tertiary Program Loader)作为中间层。

- 安全启动扩展(ATF) 在ARMv8+平台,ARM Trusted Firmware(ATF)作为安全固件层介入:

- BL1/BL2:由BootROM加载,负责初始化安全环境(如加密引擎)、DDR PHY校准。

- BL31:运行在EL3安全态,提供Secure Monitor Call(SMC)服务,最终将控制权移交非安全态(EL2/EL1)的U-Boot。

三、主引导程序阶段(U-Boot)

U-Boot作为通用引导加载程序,核心任务包括:

- 硬件深度初始化

- 配置网络控制器(如TFTP加载内核)、存储接口(eMMC/NAND)、显示设备等。

- 加载内核与设备树

- 从存储设备读取压缩内核镜像(如

Image.gz)和设备树二进制文件(.dtb)到DDR指定地址。- 传递启动参数

- 通过寄存器约定传递设备树地址(如ARM64的

x0寄存器)。- 跳转至内核入口

- 执行

bl arch_setup_and_jump,清理缓存/TLB后跳转到内核解压代码入口。

四、Linux内核初始化

内核启动分为底层汇编初始化与高层C语言子系统启动:

- 汇编入口(

head.S)

- 设置异常向量表:处理中断、缺页等异常。

- 启用MMU与缓存:配置页表、开启虚拟地址映射。

- 解压内核:若使用压缩镜像(如zImage),调用解压算法(gzip/lzma)展开内核。

- C语言阶段(

start_kernel())

- 初始化核心子系统:进程调度器(

sched_init())、内存管理(mm_init())、驱动模型。- 挂载根文件系统:通过initramfs或直接挂载Flash上的文件系统(如SquashFS)。

- 启动第一个用户进程:创建

init进程(PID=1),移交控制权。

五、用户空间初始化

- init进程

- 解析初始化脚本(如

init.rc),挂载/sys、/proc等虚拟文件系统。- 启动系统服务

- 启动守护进程(如网络管理、日志服务)、图形界面(如Android的SurfaceFlinger)。

- 应用程序就绪

- 执行登录管理器(如getty)或直接启动应用框架(如Android的Zygote)。

六、多核SoC的启动扩展

多核SoC(如Cortex-A多集群)需额外处理:

- 主核与从核分工

- 主核(Primary Core):执行完整启动流程,初始化共享资源(内存、外设)。

- 从核(Secondary Core):由主核通过写寄存器唤醒(如ARM的

PSCI接口),从指定地址(如0x00000004)开始执行。- 同步机制

- 从核启动前需等待主核完成基础设置,通常通过Spin-Table或中断唤醒实现同步。

总结

ARM SoC的启动流程是层层递进的“接力”过程:

- 硬件层:BootROM → SPL → U-Boot → Kernel → User Space。

- 安全层:BootROM → ATF(BL1/BL2/BL31) → U-Boot(非安全态)。

- 多核协同:主核主导初始化,从核按需启动。

此流程高度依赖芯片设计(如复位地址映射)、固件配置(如设备树),开发者需结合具体SoC手册调整启动代码。

3.SPL-二级引导程序

SPL(Secondary Program Loader)是嵌入式系统启动流程中的关键组件,尤其在基于ARM架构的SoC(System on Chip)中扮演核心角色。它作为BootROM后的第二级引导程序,主要负责在资源受限的早期启动阶段完成硬件初始化和环境准备,为后续主引导程序(如U-Boot)的运行奠定基础。以下是SPL在CPU启动过程中的具体作用及技术细节:

一、硬件初始化与基础环境搭建

- CPU核心配置

- 状态重置:SPL首先将CPU从复位状态解除,设置其运行模式(如ARMv8的EL3异常等级),并配置关键寄存器(如控制寄存器、协处理器寄存器),确保CPU进入可预测的稳定状态。

- 缓存与MMU设置:初始化指令/数据缓存(Cache),禁用内存管理单元(MMU),避免早期内存访问冲突。

- 内存控制器初始化

- DRAM配置:配置内存控制器的时序参数、电压及接口模式(如DDR3/DDR4的tRCD、CL值),确保内存稳定工作。

- 内存测试:执行简单的内存读写测试(如地址线/数据线校验),验证DRAM可用性。

- 时钟与电源管理

- 时钟树配置:设置PLL锁相环,分配核心时钟(CPU主频)、总线时钟(AHB/APB)及外设时钟源,确保各组件同步运行。

- 电源域初始化:启用关键模块(如存储控制器、调试接口)的供电,关闭未使用模块以降低功耗。

- 基础外设使能

- 调试接口初始化:启用串口(UART)输出调试信息,便于开发者追踪启动故障。

- GPIO配置:设置关键引脚状态(如复位信号、启动模式选择引脚),防止硬件冲突。

二、启动流程的衔接与加载控制

- 存储设备识别与访问

- 介质枚举:根据SoC启动模式(如eMMC、SD卡、SPI闪存),初始化对应存储控制器,读取分区表或固件头信息。

- 数据加载:从存储设备中定位并加载下一阶段镜像(如U-Boot、ATF信任固件),将其复制到指定内存地址(通常为DRAM或SRAM)。

- 执行权移交

- 跳转至主引导程序:设置程序计数器(PC)和栈指针(SP),将控制权移交至U-Boot入口地址,并传递硬件参数(如内存大小、时钟频率)。

- 重定位支持:在资源受限平台(如仅含SRAM的SoC),SPL可能先将自身重定位至DRAM以释放SRAM空间。

三、资源受限环境中的优化设计

- 代码体积压缩

- SPL需在极小内存(通常几十KB的SRAM)中运行,因此仅包含最精简的驱动(如存储访问、时钟配置),避免复杂功能(如网络协议栈)。

- 通过编译选项(如

CONFIG_SPL_BUILD)剥离U-Boot的非必要模块,生成独立二进制文件(如u-boot-spl.bin)。- 启动速度优化

- 跳过完整硬件检测(如详细内存测试),仅执行关键初始化,加速启动过程(适用于实时性要求高的嵌入式场景)。

- 支持XIP(eXecute In Place)技术,允许直接从闪存执行代码,减少加载时间。

四、安全与错误处理机制

- 安全启动支持

- 在支持信任根(Root of Trust)的SoC中,SPL可验证下一阶段镜像的数字签名,防止恶意固件加载。

- 与信任固件(如ARM Trusted Firmware)协作,构建安全启动链。

- 错误检测与恢复

- 硬件故障处理:若初始化失败(如内存检测错误),SPL通过串口输出错误码或触发LED告警。

- CPU热插拔校验:在支持动态扩展的系统中,SPL验证新增CPU的补丁状态,避免未修复错误的CPU上线引发系统崩溃。

SPL在不同SoC平台中的实现差异

SoC平台 SPL实现特点 典型应用场景 TI AM335x 集成于开发板固件,支持eMMC/SD卡双启动 BeagleBone Black嵌入式开发板 Rockchip RK3399 与TPL(芯片级初始化)协作,负责加载ATF和U-Boot 高性能平板/物联网网关 Allwinner H3 专注DRAM初始化,适配低成本DDR3内存 智能家居设备及开源硬件

总结

SPL是嵌入式系统启动流程中的“桥梁”,通过高效完成硬件初始化、存储访问和资源管理,为U-Boot及操作系统内核的加载提供稳定环境。其设计平衡了体积精简性、执行效率与功能必要性,尤其适合资源受限的嵌入式场景(如IoT设备、工业控制器)。理解SPL的作用,对优化启动速度、调试启动故障及定制化引导流程具有重要意义。

4.U-Boot-通用引导加载程序

U-Boot(Universal Boot Loader)是一种开源的通用引导加载程序(Bootloader),专为嵌入式系统设计,负责在设备上电后初始化硬件、加载操作系统内核,并移交控制权。以下是其核心特性与功能的详细解析:

一、核心功能

- 硬件初始化

- 基础配置:初始化CPU核心、内存控制器、时钟系统、外设(如串口、网络接口、存储控制器)等,确保硬件进入可工作状态。

- 内存管理:配置DRAM控制器并执行简单内存测试,为内核加载提供稳定环境。

- 操作系统加载与启动

- 内核加载:从存储介质(如Flash、SD卡、eMMC)或网络(TFTP/NFS)加载内核镜像到内存。

- 参数传递:通过环境变量(如

bootargs)向内核传递启动参数(如根文件系统路径、IP地址)。- 设备树支持:加载设备树二进制文件(DTB),为内核提供硬件配置信息(如ARM平台)。

- 交互式调试与配置

- 命令行接口(CLI):通过串口或网络提供交互式终端,支持命令如:

printenv/setenv:查看/修改环境变量。tftpboot:从TFTP服务器下载镜像。bootm/bootz:启动内核。- 固件更新:支持通过命令烧录新固件到Flash或eMMC。

- 环境变量管理

- 持久化存储配置参数(如启动顺序、网络设置),支持自定义启动脚本。

二、核心特点

- 跨平台支持

- 处理器架构:兼容ARM、MIPS、PowerPC、x86、RISC-V等主流架构。

- 开发板适配:支持数千种硬件平台(如树莓派、BeagleBone),通过

board/目录实现板级定制。- 开源与可定制性

- 遵循GPL协议,源码开放,允许深度裁剪(如移除非必要驱动)以适配资源受限设备。

- 通过

Kconfig配置系统灵活选择功能模块。- 多阶段引导机制

- 支持SPL(Secondary Program Loader),在资源受限时(如仅SRAM可用)分阶段初始化硬件,再加载完整U-Boot。

- 丰富的协议与文件系统支持

- 网络协议:TFTP、DHCP、NFS等,支持网络启动和远程调试。

- 文件系统:FAT、EXT4、UBIFS等,可直接读写存储设备。

三、典型应用场景

场景 说明 示例 消费电子 快速启动与系统恢复 路由器、智能电视 工业控制 高可靠性引导,支持远程固件更新 PLC、工业网关 物联网设备 低资源占用,适配定制硬件 传感器节点、智能家居设备 开发调试 通过CLI实时测试硬件(内存、网络)、修复启动故障 嵌入式开发板

四、与其他引导程序的对比

特性 U-Boot GRUB BIOS/UEFI 适用场景 嵌入式系统、定制硬件 PC/Linux服务器 通用PC 硬件支持 高度定制化,适配多样SoC 依赖标准硬件接口(如x86) 固定硬件规范 交互性 命令行调试功能强大 图形菜单为主 基础配置界面 可扩展性 支持深度裁剪与新硬件适配 功能固定,扩展有限 不可编程

五、代码结构与工作流程

- 代码架构

- 分层设计:

arch/:CPU架构相关代码(如ARM初始化)。board/:板级硬件适配代码。drivers/:外设驱动(网卡、Flash控制器)。common/:通用功能(环境变量、命令解析)。- 启动流程

- Stage 1(汇编层):关闭中断/MMU,初始化栈,配置内存控制器。

- Stage 2(C语言层):初始化外设→加载环境变量→执行

bootcmd启动内核。

总结

U-Boot是嵌入式领域的核心基础设施,兼具硬件初始化、内核引导、系统调试三大核心能力。其开源特性与跨平台能力使其成为物联网设备、工业控制器等场景的事实标准。开发者可通过其命令行接口灵活控制系统启动流程,并通过裁剪适配从微控制器到高性能SoC的各类平台。

5.Bootloader-引导加载程序

Bootloader(引导加载程序)是计算机或嵌入式系统启动时运行的第一段软件代码,负责初始化硬件、加载操作系统或应用程序,并为后续程序的执行准备运行环境。它是系统加电后执行的起点,位于操作系统内核之前,直接依赖于硬件架构实现。以下是其核心要点:

一、定义与核心作用

- 硬件与操作系统的桥梁 Bootloader是系统复位后从预定义地址(如ARM处理器的

0x00000000)加载的首段程序。它初始化CPU基本设置(寄存器、堆栈)、内存控制器、时钟等关键硬件,建立内存映射,确保软硬件环境达到可运行操作系统的状态。- 依赖硬件定制化 不同CPU架构(如ARM、x86)及外围设备配置需定制专属Bootloader,例如基于ARM系统常使用U-Boot,并需根据具体硬件(如Flash存储器地址分配)调整代码。

二、核心功能

硬件初始化

- 基础初始化:配置CPU工作模式、时钟频率、内存控制器,检测RAM健康状态。

- 外设准备:初始化串口、网络接口等通信设备,为后续加载提供支持。

加载与启动操作系统

- 从存储介质(Flash、SD卡等)读取操作系统内核映像到内存,验证完整性后跳转至内核入口点。

- 支持多重启动选项(如选择不同OS版本或恢复模式)。

固件更新与故障恢复

- 通过串口、USB或网络(如TFTP)更新系统固件,支持OTA(空中下载)更新。

- 提供安全模式或恢复出厂设置功能,应对主程序启动失败。

安全机制

验证操作系统签名,确保加载的代码未被篡改(如安全启动Secure Boot)。

三、两阶段工作原理(Stage1 & Stage2)

- Stage1(汇编实现,硬件相关)

- 执行底层初始化:关闭中断、设置堆栈指针、初始化关键外设。

- 拷贝Stage2到RAM:为高级语言代码准备运行环境。

- Stage2(C语言实现,功能扩展)

- 进一步初始化复杂外设(如网络、文件系统)。

- 加载内核映像到内存,传递启动参数(如内存布局),最终启动操作系统。

四、典型应用与常见类型

- 应用场景

- 嵌入式系统:如汽车ECU控制、物联网设备(U-Boot)。

- 移动设备:Android Bootloader支持解锁和刷机。

- 计算机:BIOS/UEFI加载GRUB、LILO等引导程序。

- 常见Bootloader

- U-Boot:开源、支持多架构(ARM/MIPS/x86),广泛用于嵌入式设备。

- GRUB/LILO:PC端Linux系统的标准引导程序。

- STM32 Bootloader:专用于STM32微控制器,支持串口/USB固件更新。

总结

Bootloader是系统启动不可或缺的“启动引擎”,承担硬件初始化、系统加载、安全校验等关键任务。其设计高度依赖硬件平台,需兼顾效率与功能性(如两阶段分工)。在嵌入式开发中,定制化Bootloader(如裁剪U-Boot)是确保系统稳定启动的基础。

6.启动地址&链接地址

在ARM体系结构中,链接地址(Link Address)和启动地址(Start Address)是两个关键概念,它们共同决定了程序在内存中的布局和执行流程。以下是两者的区别与联系分析:

一、定义与核心区别

概念 定义 性质 作用阶段 链接地址 链接器(Linker)在编译时指定的代码运行时“应该”所处的内存地址(虚拟或物理)。 绝对地址(编译时确定)编译链接阶段 启动地址 处理器复位后开始执行代码的实际物理地址(如 0x00000000或0xFFFF0000)。物理地址(硬件固定) 硬件启动阶段 关键区别:

- 链接地址是软件逻辑地址,由开发者通过链接脚本指定,用于生成符号地址;

- 启动地址是硬件执行地址,由CPU复位逻辑决定,是第一条指令的物理位置。

二、两者关系与协作机制

1. 一致场景(直接执行)

当链接地址与启动地址相同时(例如程序直接烧写到

0x00000000的Flash中),CPU可直接从启动地址执行代码,无需额外处理。示例:裸机程序在ROM中运行,链接地址设为

0x00000000。2. 不一致场景(重定位需求)

多数嵌入式系统(如Linux内核、U-Boot)需将代码从启动地址(如Flash)复制到链接地址(如RAM)执行,原因包括:

- 性能优化:RAM访问速度远快于ROM;

- 功能需求:RAM支持动态数据修改,而ROM只读。

重定位流程:

- 初始执行:CPU从启动地址(如Flash的

0x00000000)运行位置无关码(PIC);- 代码复制:将程序从Flash复制到链接地址对应的RAM区域(如

0x30000000);- 地址跳转:通过

LDR PC, =目标地址等指令跳转到RAM中的链接地址继续执行。✅ 关键点:重定位后,运行地址(PC值)与链接地址一致,确保绝对寻址指令(如LDR)正确执行。

三、技术实现依赖

1. 位置无关码(PIC)

- 作用:在重定位前执行的代码必须为PIC,仅使用相对跳转(B/BL)或PC相对寻址(ADR),不依赖绝对地址。

- 示例:U-Boot的初始阶段用

B指令跳转,避免直接加载绝对地址。2. 位置相关码(绝对寻址)

- 触发条件:跳转到链接地址后,可使用绝对地址指令(如

LDR PC, =label)。- 风险:若未完成重定位就使用绝对寻址,程序会因地址无效而崩溃。

3. MMU的影响

- MMU关闭时:链接地址需直接对应物理地址(如ZRELADDR);

- MMU开启后:链接地址可设为虚拟地址(如Linux内核的

0xC0000000),需通过MMU映射到物理地址。

四、总结

维度 链接地址 启动地址 本质 编译时逻辑地址 硬件固定物理地址 协作关系 重定位后需与运行地址一致 决定初始PC值 典型场景 程序在RAM中的目标地址 ROM/Flash的物理起始地址 依赖技术 位置无关码(PIC)实现重定位 硬件复位向量机制 💎 核心关系:启动地址是程序执行的起点,链接地址是程序运行的“理想位置”。通过重定位技术(依赖PIC),两者从分离状态转为一致,确保程序高效运行。

7.汇编获取启动&链接地址

在ARM汇编中,使用

ADR和LDR伪指令获取启动地址(运行时实际地址)与链接地址(编译时预设地址)是底层开发的关键技术,尤其在Bootloader、内核初始化等场景中。以下是核心区别、应用场景及实现方法:

一、核心区别与地址获取原理

特性 ADR指令 LDR伪指令 地址类型 启动地址(运行时实际地址) 链接地址(编译时预设地址) 生成方式 基于PC相对偏移动态计算( Rd = PC ± offset)加载链接脚本指定的绝对地址( Rd = [Label])位置相关性 位置无关码(PIC),依赖运行时PC值 位置相关码,依赖链接时固定地址 偏移范围 小范围(ARM模式:±4095字节) 大范围(支持32位地址) MMU依赖 MMU关闭时获取物理地址;开启时获取虚拟地址 需MMU开启且虚拟地址映射正确

二、应用场景分析

1. ADR:动态获取启动地址(运行时地址)

适用场景:

- Bootloader重定位:判断代码实际运行位置(Flash vs RAM)。

- 位置无关代码:如内核初始化阶段(MMU未开启)。

- 短距离跳转:同一代码段内的标签跳转(如循环、局部函数)。

典型代码:

_start:adr r0, _start @ 获取_start的运行时地址(实际物理地址)cmp r0, #0 @ 若在地址0运行,说明位于Flash中bne relocate @ 否则跳转到重定位逻辑2. LDR伪指令:加载链接地址

适用场景:

- 外设寄存器访问:加载绝对地址(如

0xFD800000)。- 全局符号引用:需匹配链接脚本定义的地址(如

_bss_start)。- 重定位代码:将数据/代码从Flash复制到RAM的链接地址处。

典型代码:

ldr r1, =_start @ 获取_start的链接地址(如0x30000000) ldr r2, =0xFD800000 @ 加载外设寄存器绝对地址

三、编译实现与底层机制

指令 编译转换方式 地址生成时机 ADR 替换为 ADD/SUB指令(如add r0, pc, #0x20)运行时动态计算 LDR伪指令 生成文字池(Literal Pool)存储绝对地址: - 小立即数→ MOV指令 - 大地址→从文字池加载(ldr r0, [pc, #offset])链接时固定写入 示例反汇编对比:

0x00000000: adr r0, _start → add r0, pc, #0x8 @ PC=0x8, r0=0x10(运行时地址) 0x00000004: ldr r1, =_start → ldr r1, [pc, #4] @ 从文字池0x0C加载0x30000000(链接地址)

四、关键注意事项

- ADR的范围限制:

- 偏移超过±4095字节时编译失败,需改用

LDR或ADRP(ARM64)。- LDR伪指令的可靠性:

- 若实际运行地址与链接地址不一致(如未重定位),加载的地址无效。

- MMU配置的影响:

- MMU关闭时:

ADR获取物理地址,LDR获取的链接地址可能无效。- MMU开启后:两者均需虚拟地址与链接地址匹配。

- ARM64差异:

- ARM64中

ADR是真实指令(非伪指令),寻址范围扩展至±1MB。

五、实战案例:U-Boot重定位

ENTRY(_start)adr r0, _start @ 获取当前运行地址(Flash中地址)ldr r1, =_start @ 获取链接地址(RAM中地址,如0x30000000)cmp r0, r1 @ 比较是否需重定位beq run_in_ram @ 若相等,直接跳转到RAM执行relocate:ldr r2, =_bss_start @ 复制源结束地址(链接地址)ldr r3, =_bss_end @ 复制目标结束地址 copy_loop:ldmia r0!, {r4-r7} @ 从Flash读取4字stmia r1!, {r4-r7} @ 写入RAMcmp r1, r2 @ 检查是否复制完成blt copy_looprun_in_ram:ldr pc, =main @ 跳转到RAM中的main函数

- 关键逻辑:

ADR动态检测启动位置 →LDR加载链接地址 → 比较后决定是否复制代码到RAM。

总结

ADR→ 启动地址:动态计算、位置无关,适用于运行时地址获取。LDR伪指令 → 链接地址:静态加载、位置相关,需与链接脚本一致。选择依据:- 需地址无关或MMU关闭 →

ADR- 需绝对地址或大范围偏移 →

LDR伪指令理解二者差异是实现重定位、位置无关代码及硬件初始化的基础。

8.地址重定位

地址重定位(Address Relocation)是操作系统内存管理的核心机制之一,指将程序中的**逻辑地址(相对地址)转换为物理内存中的实际地址(绝对地址)**的过程。这一过程解决了程序编译时无法预知实际内存分配位置的问题,是多道程序并发执行的基础。其核心在于建立程序逻辑地址空间与物理内存空间的映射关系。

一、地址重定位的分类与原理

根据转换时机和技术实现,地址重定位分为静态重定位和动态重定位两类:

1. 静态重定位

- 原理:在程序装入内存时一次性完成地址转换。装入程序根据程序在内存中的起始物理地址(重定位因子),修改目标模块中所有与地址相关的指令和数据(如跳转指令、数据加载地址)。示例:若程序逻辑地址从

0开始,实际装入内存起始地址为1000,则逻辑地址500会被修正为物理地址1500。- 特点:

- ✅ 优点:无需硬件支持,实现简单。

- ❌ 缺点:

- 程序必须占用连续内存空间,无法利用碎片化内存;

- 装入后无法移动位置,不支持内存动态调整(如交换、共享)。

2. 动态重定位

- 原理:在程序执行过程中实时转换地址。程序装入内存时保持逻辑地址不变,由硬件(如基址寄存器)在CPU访问内存前完成转换:物理地址 = 逻辑地址 + 基址寄存器值。示例:基址寄存器存储程序起始地址

1000,执行指令MOV EAX, [500]时,实际访问的物理地址为500 + 1000 = 1500。- 特点:

- ✅ 优点:

- 支持非连续内存分配(如分页、分段);

- 程序可动态移动或扩展(如内存紧缩、共享库加载);

- 实现虚拟内存的基础(如按需调入页面)。

- ❌ 缺点:需硬件支持(如MMU、基址/限长寄存器),软件算法更复杂。

二、技术实现依赖

- 静态重定位的流程:

- 链接器生成包含重定位项表的装入模块(记录需修改的地址位置);

- 装入程序根据实际内存起始地址修正所有重定位项,完成后丢弃重定位表。

- 动态重定位的硬件支持:

- 基址寄存器:存储程序起始物理地址;

- 限长寄存器:防止地址越界(保护内存隔离);

- MMU(内存管理单元):集成地址转换电路,自动完成计算。

三、静态重定位 vs 动态重定位

特性 静态重定位 动态重定位 转换时机 程序装入内存时一次性完成 指令执行时实时转换 硬件依赖 无需硬件 需基址寄存器/MMU等硬件支持 内存连续性要求 必须连续存储 可非连续(支持分页、分段) 程序移动支持 ❌ 装入后不可移动 ✅ 支持运行时移动(如内存碎片整理) 应用场景 早期单任务系统 现代多道程序操作系统(如Linux、Windows)

四、核心应用场景

- 多道程序并发: 多个程序共享内存时,通过重定位避免地址冲突(如进程A的逻辑地址

0x100映射到物理地址0x1000,进程B的0x100映射到0x2000)。- 内存共享与迁移:

- 共享库:多个进程通过动态重定位共享同一物理内存中的代码(如Windows DLL文件);

- 进程迁移:动态重定位允许进程换出后再换入不同内存区域(交换技术)。

- 虚拟存储扩展: 动态重定位结合分页机制,实现按需调页的虚拟内存(如逻辑地址空间 > 物理内存)。

总结

地址重定位的本质是逻辑地址到物理地址的映射,其实现方式决定了操作系统的内存管理能力:

- 静态重定位适用于资源受限的嵌入式系统,但灵活性差;

- 动态重定位凭借硬件协作支持现代操作系统的核心特性(虚拟内存、进程隔离、内存共享),成为当前主流方案。 理解二者差异,是掌握内存分配、进程调度及系统优化的关键基础。

9.Device Copy Function-iROM数据复制功能

在系统启动过程中,“Device Copy Function”特指嵌入式系统(如基于S5PV210芯片的设备)启动时,由芯片内部固化的iROM代码提供的关键数据复制功能。其核心作用是从外部存储介质(如SD卡、NandFlash等)读取启动代码(如BL1)到内部RAM(iRAM)中执行,确保系统正常启动。以下是详细解释:

1. 功能定位与作用

- 初始化外部存储设备:在启动的最初阶段(BL0),iROM中的代码通过Device Copy Function初始化外部存储介质(如SD卡、NandFlash),包括配置时序、接口参数等,使其可被正确读写。

- 复制启动代码:将存储在外部介质中的第一阶段启动代码(BL1,通常≤16KB)复制到芯片内部的iRAM(SteppingStone区域)中执行。BL1后续负责加载更复杂的启动代码(如BL2)和操作系统。

2. 实现机制与技术细节

- 固化在iROM中:Device Copy Function的代码由芯片制造商预先烧录在iROM中,开发者无法修改源码,只能通过函数指针调用。

- 多介质适配:针对不同存储介质(如SD卡、eMMC、NandFlash),iROM内置了对应的Device Copy Function实现。例如:

- SD卡:通过

CopySDMMCtoMem函数实现数据复制。- NandFlash:需特定时序初始化后读取数据。

- 块设备操作限制:由于存储设备以“块”(通常512字节)为单位读写,Device Copy Function必须按整块复制数据,无法读取部分扇区。

3. 调用方式(开发者视角)

开发者通过函数指针调用Device Copy Function,步骤如下:

- 获取函数地址:从iROM的固定地址读取函数入口(如

0xD0037F98对应CopySDMMCtoMem)。- 定义函数指针类型:根据函数签名(参数类型、返回值)定义指针类型。例如:

typedef bool (*CopyFuncPtr)(int, unsigned int, unsigned short, unsigned int*, bool);

- 调用函数:

CopyFuncPtr pCopy = (CopyFuncPtr)(*(unsigned int*)0xD0037F98); pCopy(channel, srcBlock, blockCount, destAddr, initFlag); // 复制SD卡数据到内存此过程需严格匹配参数类型,否则会导致启动失败。

4. 与启动流程的关联

Device Copy Function是启动链条中的关键环节:

- BL0阶段:芯片上电后执行iROM代码(BL0),通过读取引脚电平判断启动介质类型,调用对应的Device Copy Function初始化设备并复制BL1到iRAM。

- BL1阶段:BL1在iRAM中运行后,会初始化DDR内存,并调用Device Copy Function将更大规模的BL2或操作系统加载到DDR中。

- 容错机制:若第一启动介质(如SD卡)复制失败,会自动尝试第二介质(如eMMC)。

5. 与其他场景的区分

需注意“Device Copy Function”在系统启动中的特定含义,区别于其他类似概念:

- Windows API

CopyDeviceMemory:用于设备内存复制,关注内存对齐和编译器优化,与启动无关。- 应用层复制函数(如Power Apps的

Copy()):仅操作剪贴板文本,无硬件初始化功能。

总结

Device Copy Function是嵌入式系统启动的底层引擎,其本质是芯片厂商预置的、用于初始化存储设备并复制启动代码的固件功能。它解决了外部存储介质多样性带来的驱动问题,确保BL1能被可靠加载,是系统从“硬件上电”到“软件执行”的关键桥梁。

10.SteppingStone-NandFlash启动机制

SteppingStone(垫脚石)是ARM处理器中用于解决**NAND Flash无法直接执行代码(XIP)**问题的硬件启动机制,核心是通过内部SRAM缓存实现初始代码的加载与执行。以下从原理、实现、演进及应用等维度解析:

一、基本概念与核心作用

问题背景

NAND Flash作为低成本大容量存储,广泛用于嵌入式系统,但其接口特性(数据/地址线复用、需时序控制)导致无法像NOR Flash一样直接执行代码(XIP)。

SteppingStone的本质

是ARM处理器(如三星S3C2440)内部集成的4KB SRAM缓存(部分新型号如S5PV210扩展至96KB),位于芯片内部,物理地址固定(如S3C2440映射至

0x00000000)。核心作用

上电时,硬件自动将NAND Flash前4KB代码复制至此SRAM,并跳转执行,为后续完整Bootloader加载到SDRAM创造条件,实现从NAND Flash的间接启动。

二、硬件实现与工作流程

1. 启动流程(以S3C2440为例)

- 上电自检:硬件检测启动模式(OM引脚决定是否从NAND启动)。

- 自动拷贝:NAND控制器将Flash前4KB数据搬运至SteppingStone SRAM。

- 地址映射:SRAM被映射到ARM地址空间

0x00000000(复位向量起始地址)。- 执行初始代码:PC指针跳转至

0x00000000,执行SRAM中的代码(即Bootloader前4KB)。- 扩展引导:初始代码初始化SDRAM后,将完整Bootloader从NAND复制至SDRAM(如

0x30000000),并跳转执行。2. 初始代码的关键任务

- 初始化时钟、关闭看门狗、配置SDRAM控制器。

- 设置中断向量表与堆栈(堆栈需限制在4KB SRAM内)。

- 实现NAND到SDRAM的代码搬运(需处理坏块校验)。

三、技术优势与设计挑战

1. 优势

- 低成本:替代昂贵的NOR Flash启动方案,降低BOM成本。

- 快速启动:硬件自动拷贝+SRAM高速执行,缩短首条指令延迟。

- 可靠性:SRAM抗干扰性强,避免NAND读取不稳定导致的启动失败。

2. 挑战与解决

问题 原因 解决方案 4KB代码限制 SRAM容量固定 初始代码需精简,仅保留核心搬运逻辑 NAND坏块风险 初始区域存在坏块导致拷贝失败 硬件ECC校验或预留备份区块 堆栈溢出 SRAM仅4KB需共享代码与堆栈空间 堆栈深度严格限制(通常<1KB)

四、不同ARM处理器的实现演进

处理器型号 SteppingStone大小 启动流程特点 地址映射方式 S3C2440 4KB SRAM 全硬件自动拷贝,无固件层 直接映射至 0x00000000S3C6410 8KB SRAM 增加IROM固件(BL0),支持SD/NAND启动 镜像映射至0地址 S5PV210 96KB SRAM 多级引导(BL0→BL1→BL2),支持USB启动 IRAM映射至 0xD0020000

- 演进趋势:SRAM容量增大 → 支持更复杂初始代码;引入固件层(BL0)→ 增强启动灵活性(如多介质选择)。

五、应用场景与设计要点

1. 典型应用

- 低成本嵌入式设备:智能家居控制器、工业传感器(采用NAND Flash存储系统镜像)。

- 消费电子:MP4播放器、车载导航仪(需快速启动且成本敏感)。

2. 设计注意事项

- 代码精简性:初始4KB代码需用汇编编写,避免冗余操作。

- 地址对齐:Bootloader前4KB需连续无坏块,烧写时强制对齐。

- 功耗优化:SRAM在低功耗模式下维持数据,保障快速唤醒。

总结

SteppingStone是ARM处理器从NAND Flash启动的硬件桥梁,通过片上SRAM缓存+自动搬运机制,解决了非XIP存储介质的启动难题。其设计平衡了成本、速度与可靠性,在嵌入式领域持续演进(如增大SRAM容量、多级引导)。开发中需注重初始代码的优化与存储介质管理,以充分发挥其价值。

11.S5PV210(三星SoC)的SD卡启动详解

SoC为何要支持SD卡启动

(1)一个普遍性的原则就是:SoC支持的启动方式越多,将来使用时就越方便,用户的可选择性就越大,SoC的适用面就越广。

(2)SD卡有一些好处:譬如可以在不借用专用烧录工具(类似Jlink)的情况下对SD卡进行刷机,然后刷机后的SD卡插入卡槽,SoC即可启动;譬如可以用SD卡启动进行量产刷机(量产卡)。

像我们x210开发板,板子贴片好的时候,内部inand是空的,此时直接启动无启动,因为此时inand是空的,所以第一启动失败,会转入第二启动,就从外部SD2通道的SD卡启动了。

启动后会执行刷机操作对iNand进行刷机,刷机完成后自动重启(这回重启时iNand中已经有image可,所以可以启动了)。刷机完成后SD量产卡拔掉,烧机48小时,无死机即可装箱待发货。

SD卡启动的难点在哪里(SRAM、DDR、SDcard)

(1)SRAM、DDR都是总线式访问的,SRAM不需要初始化即可直接使用,而DDR需要初始化后才能使用,但是总之CPU可以直接和SRAM和DDR打交道;

而SD卡需要时序访问,CPU不能直接和SD卡打交道;NorFlash读取时可以总线式访问,所以NorFlash启动非常简单,可以直接启动,但是SD/NandFlash不行。

(2)以前只有NorFlash可以作为启动介质,台式机笔记本的BIOS就是NorFlash做的介质。后来三星2440中使用了SteppingStone的技术,让NandFlash也可以作为启动介质。

SteppingStone(启动基石)技术就是在SoC内部内置4KB的SRAM,然后开机时SoC根据OMPin判断用户设置的启动方式,如果是NandFlash启动,则Soc的启动部分的硬件直接从外部NandFlash中读取开头的4KB到内部SRAM作为启动内容。

(3)启动基石技术进一步发展,在6410芯片中得到完善,在210芯片时已经完全成熟。210中有96KB的SRAM,并且有一段iROM代码作为BL0,BL0再去启动BL1(210中的BL0做的事情在2440中也有,只不过那时候是硬件自动完成的,而且体系没有210中这么详细)。

S5PV210的启动过程回顾

(1)210启动首先执行内部的iROM(也就是BL0),BL0会判断OMPin来决定从哪个设备启动,如果启动设备是SD卡,则BL0会从SD卡读取前16KB到iSRAM中去启动执行(这部分就是BL1,这就是SteppingStone技术)

(2)BL1执行之后剩下的就是软件的事情了,SoC就不用再去操心了。

SD卡启动流程(bin文件小于16KB时和大于16KB时)

(1)启动的第一种情况是整个镜像大小小于16KB。这时候相当于我的整个镜像作为BL1被SteppingStone直接硬件加载执行了而已。

(2)启动的第二种情况就是整个镜像大小大于16KB。(只要大于16KB,哪怕是17KB,或者是700MB都是一样的)这时候就要把整个镜像分为2部分:第一部分16KB大小,第二部分是剩下的大小。

第一部分作为启动介质,负责去初始化DRAM并且将第二部分加载到DRAM中去执行(uboot就是这样做的)。

最重要的但是却隐含未讲的东西

(1)问题:iROM究竟是怎样读取SD卡/NandFlash的?

(2)三星在iROM中事先内置了一些代码去初始化外部SD卡/NandFlash,并且内置了读取各种SD卡/NandFlash的代码在iROM中。

BL0执行时就是通过调用这些device copy function来读取外部SD卡/NandFlash中的BL1的。

SoC支持SD卡启动的秘密(iROM代码)

三星系列SoC支持SD卡/NandFlash启动,主要是依靠SteppingStone技术,具体在S5PV210中支持SteppingStone技术的是内部的iROM代码。

iROM application note:block device copy function

12.S5PV210多级引导启动

S5PV210的多级引导启动机制采用分层设计,通过BL0、BL1、BL2三级引导实现从硬件初始化到操作系统的加载,其核心流程如下:

⚙️ 一、启动阶段划分与功能

- BL0(固化引导层)

- 位置与功能:固化于64KB内部ROM(iROM),上电后首先执行。负责初始化系统时钟、关闭看门狗、设置堆栈/堆区域,并根据OM引脚选择启动设备(如SD卡、NAND Flash等)。

- BL1加载:从启动设备复制BL1(最大16KB)到96KB内部SRAM(iRAM)的

0xD0020000地址,并校验其完整性(校验和与安全启动验证)。- BL1(初级引导层)

- 执行位置:在iRAM中运行(起始地址

0xD0020010,跳过16字节头部)。- 核心任务:初始化外部存储设备(如NAND控制器),加载BL2到iRAM剩余空间(最大80KB),并校验BL2完整性。

- BL2(完整引导层)

- 功能:初始化DRAM控制器,将操作系统内核从外部存储加载到SDRAM,并跳转至OS入口地址。

🔍 二、关键机制详解

- 启动设备选择与容错

- 通过OM引脚配置启动介质(如SD通道0、NAND等)。若首次启动失败(如校验错误),自动尝试第二通道(如SD通道2)或备用方式(UART/USB),形成多级冗余。

- 安全启动与校验机制

- 头部结构:BL1前16字节包含校验和、BL1尺寸等信息(地址

0xD0020000)。BL0通过累加BL1数据计算校验和,匹配失败则触发二次启动。- 安全模式:若芯片预烧录安全密钥,BL0/BL1会验证代码签名,防止恶意固件执行。

- 地址空间与内存映射

- iRAM布局:

0xD0020000~0xD003FFFF。BL1代码实际从0xD0020010开始执行(UART/USB启动除外)。- 全局变量区:存储启动设备参数(如SD卡容量地址

0xD0037480),供BL1直接调用。⚡️ 三、设计特点与优化

分层解耦

BL0处理硬件依赖(时钟/设备初始化),BL1/BL2实现引导逻辑分离,增强可移植性。

资源限制与突破

iRAM仅96KB,故BL1(16KB)+BL2(80KB)需精简。实际应用中可通过BL2初始化DRAM后加载更大UBOOT,突破空间限制。

快速启动策略

- 硬件加速:BL0使用PLL快速配置时钟。

- 并行初始化:BL1加载BL2时可预初始化关键外设。

四、典型启动流程

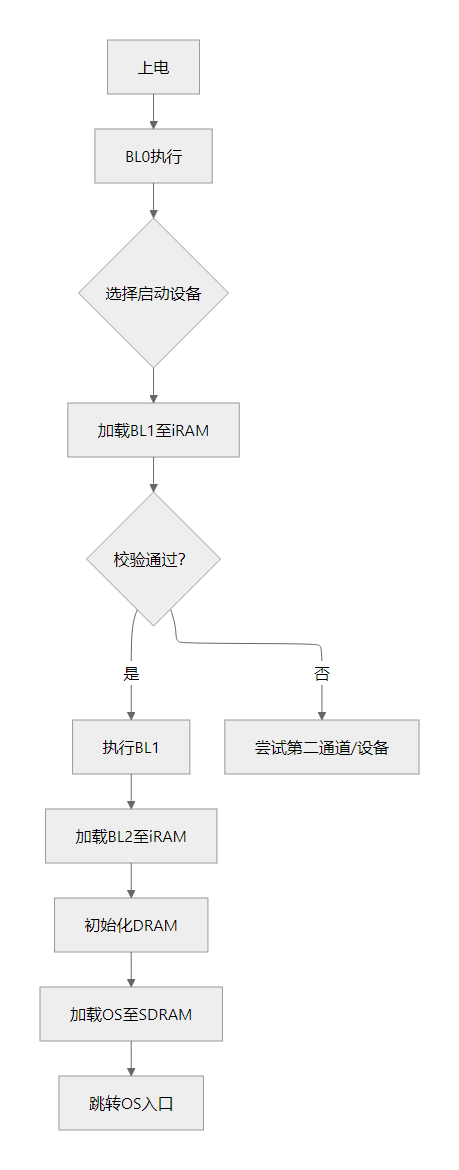

graph TDA[上电] --> B[BL0执行]B --> C{选择启动设备}C --> D[加载BL1至iRAM]D --> E{校验通过?}E -- 是 --> F[执行BL1]E -- 否 --> G[尝试第二通道/设备]F --> H[加载BL2至iRAM]H --> I[初始化DRAM]I --> J[加载OS至SDRAM]J --> K[跳转OS入口]

💎 总结

S5PV210通过三级引导(BL0→BL1→BL2)实现从固件到操作系统的过渡,其核心在于硬件初始化分层、安全校验及冗余启动设计。该机制平衡了启动安全性与灵活性,为嵌入式系统提供了可靠的引导基础。实际开发中需注意BL1的16字节头部校验和生成(工具如

mkv210_image.c)及启动设备配置(OM引脚),以避免启动失败。

13.中断

中断系统是计算机硬件与操作系统协同实现的事件响应机制,用于在CPU执行正常程序时,临时暂停当前任务,转而处理外部或内部的高优先级事件(如I/O请求、硬件故障、定时器到期等),处理完成后恢复原任务执行。其核心功能是协调CPU对外部事件的响应,实现多任务调度、实时控制和故障处理,从而提高计算机效率。

一、中断系统基础概念

- 定义与核心功能

- 中断:CPU对系统事件的响应机制,暂停当前程序转去执行中断服务程序(ISR),处理完成后返回原程序。

- 核心功能:

- 实时响应:处理紧急事件(如硬件故障、外设请求)。

- 多任务调度:通过中断嵌套和优先级机制协调并发任务。

- 资源优化:避免CPU轮询,提高资源利用率。

- 基本流程

- 中断请求:硬件或软件触发中断信号(如键盘输入、定时器到期)。

- 中断响应:CPU保存当前程序状态(程序计数器PC、状态寄存器PSWR),跳转至ISR入口。

- 中断处理:执行ISR逻辑(如读取数据、错误处理)。

- 中断返回:恢复现场,继续原程序。

二、中断分类与优先级管理

- 中断类型

- 外部中断:由外设触发(如I/O设备、时钟),通过中断请求线(IRQ)发送信号。

- 内部异常:程序错误或硬件故障(如除零错误、溢出),称为“异常”。

- 陷入(Trap):主动触发的系统调用(如应用程序请求操作系统服务)。

- 优先级与嵌套机制

- 中断优先级:多个中断同时发生时,按优先级排序响应(如硬件故障 > 外设请求)。

- 中断嵌套:高优先级中断可打断低优先级ISR的执行,支持多级嵌套(受堆栈深度限制)。

- 中断屏蔽:通过屏蔽寄存器(IMR)控制中断响应,灵活调整优先级。

三、中断处理机制

- 硬件与软件协同

- 硬件响应:自动保存断点(PC/PSWR),获取中断向量(ISR入口地址)。

- 软件处理:ISR保存现场(寄存器值)、执行逻辑(如数据处理)、恢复现场并返回。

- 关键技术

- 中断向量表:存储ISR入口地址的表格,CPU通过中断向量定位处理程序。

- 程序状态字(PSW):记录CPU状态(指令地址、中断屏蔽位等),用于现场恢复。

- 优化策略:缩短ISR执行时间、合理配置优先级、减少嵌套冲突。

四、应用场景

- 实时系统

- 工业控制:传感器数据通过中断实时采集,定时器中断触发周期性任务。

- 操作系统

- 任务调度:时钟中断实现时间片轮转(如Linux的SysTick中断)。

- 系统调用:应用程序通过软中断(如

INT 21H)请求内核服务。- 嵌入式与通信

- 嵌入式设备:响应外部事件(如智能家居传感器触发中断)。

- 网络通信:网卡数据到达时触发I/O中断,CPU处理数据包。

五、总结

中断系统是计算机高效运作的核心基础设施,通过硬件触发与软件处理的协同,实现了事件驱动的实时响应。其设计关键在于优先级管理(嵌套与屏蔽)、现场保护/恢复机制及中断向量定位。在实时控制、多任务操作系统和嵌入式领域,中断机制显著提升了系统的并发性、可靠性和资源利用率。

💡 深入可参考:

- 百度百科“中断系统”、Linux中断机制、STM32中断寄存器配置。

14.Linux中断机制

Linux中断机制是操作系统响应硬件事件和软件请求的核心机制,通过异步事件处理实现系统的高效调度与实时响应。以下从原理、分类、处理流程及优化策略等方面进行系统解析:

一、中断分类与原理

- 中断类型

- 硬件中断:由外设触发(如键盘输入、网卡数据到达),通过中断请求线(IRQ)通知CPU。

- 软件中断:由程序指令触发,例如系统调用(

int 0x80)或异常处理。- 异常(Exception):CPU执行指令时触发的同步事件,分为三类:

- 故障(Fault):可恢复错误(如缺页异常),返回原指令重试。

- 陷阱(Trap):主动触发(如调试断点、系统调用),返回后续指令。

- 终止(Abort):不可恢复错误(如硬件故障),导致进程终止。

- 中断向量表(IDT)

- 存储256个中断处理程序的入口地址,每个中断号(0-255)对应一个向量:

0-31:保留给异常和非屏蔽中断(如除零错误#DE占用向量0)。32-47:分配给可屏蔽硬件中断(如时钟中断IRQ0对应向量32)。128(0x80):系统调用入口(如syscall指令)。

二、中断处理流程与上下文管理

中断响应流程

- 硬件触发:外设发送中断信号至中断控制器(如8259A/APIC)。

- CPU响应:保存当前程序状态(PC、PSW、寄存器值)至内核栈,通过IDT定位中断处理程序。

- 执行中断服务例程(ISR):

- 上半部(Top Half):在中断上下文中快速处理紧急任务(如读取硬件状态),不可阻塞。

- 下半部(Bottom Half):推迟耗时任务(如数据处理),通过软中断、Tasklet或工作队列实现。

上下文区别

特性 中断上下文 进程上下文 关联进程 无特定进程 代表用户进程执行 阻塞/睡眠 禁止(可能导致死锁) 允许 执行环境 异步、高优先级 同步、受调度器管理 典型场景 ISR上半部、软中断 系统调用、下半部的工作队列 中断上下文需避免耗时操作,否则会导致中断延迟或丢失。

三、下半部处理机制

Linux为解决中断处理时效性与复杂性的矛盾,设计了三类下半部机制:

机制 运行上下文 阻塞支持 并发性 适用场景 软中断(Softirq) 软中断上下文 否 同类型可多核并发 网络包处理、定时器 Tasklet 软中断上下文 否 同类型串行执行(防竞争) 设备驱动中的轻量级任务 工作队列(Workqueue) 进程上下文(内核线程) 是 由线程调度决定 需阻塞的复杂任务(如I/O)

- 软中断:通过

raise_softirq()触发,高效但需处理多核竞争。- Tasklet:基于软中断封装,简化接口(如

tasklet_schedule())。- 工作队列:可睡眠,适用于长任务(如文件操作),但存在调度延迟。

四、应用场景与优化

- 典型应用

- 实时系统:传感器中断触发即时响应(如工业控制)。

- 多任务调度:时钟中断(如

tick_periodic)实现进程时间片轮转。- 设备驱动:网卡收包时触发中断,上半部确认数据,下半部通过软中断处理协议栈。

- 性能优化策略

- 中断屏蔽:通过中断屏蔽寄存器(IMR)控制低优先级中断。

- 线程化中断(Threaded IRQ):将中断处理移至独立内核线程,允许阻塞和优先级调整。

- 批处理与缓冲:高频率中断(如网络流量)采用缓冲区批量处理,减少切换开销。

总结

Linux中断机制通过硬件/软件协同(IDT索引与ISR)、分层处理(上半部/下半部)和优先级管理(嵌套与屏蔽),实现了高并发与低延迟的平衡。其核心挑战在于中断上下文限制与耗时任务分解,需结合场景选择下半部机制(实时性选Tasklet,复杂性选工作队列)。深入理解中断流程(如

do_IRQ()函数)及向量表初始化(trap_init()),是开发高性能驱动与实时系统的关键基础。

15.STM32中断寄存器配置

以下是STM32中断寄存器配置的核心要点及操作流程,结合硬件原理与实战步骤进行系统梳理:

一、中断寄存器核心组

STM32中断管理依赖NVIC(嵌套向量中断控制器)和EXTI(外部中断控制器)寄存器组,关键寄存器如下:

寄存器类型 寄存器名 功能描述 位宽/数量 中断使能控制 ISER[8]中断使能设置(写1使能) 8个32位寄存器(256位) ICER[8]中断除能设置(写1禁用) 中断状态管理 ISPR[8]/ICPR[8]手动挂起/清除中断请求 IABR[8]只读寄存器,标记当前活动中断 中断优先级配置 IPR[60]设置中断优先级(高4位有效) 240字节(60×32位) 系统控制 SCB->AIRCR中断优先级分组(位10-8) 32位 外部中断控制 EXTI_IMR中断线屏蔽使能(位0-15对应16条中断线) 32位 EXTI_RTSR/FTSR上升沿/下降沿触发选择 AFIO_EXTICR[4]GPIO引脚映射到EXTI线(如PA0映射至EXTI0) 4个寄存器(16组配置)

🔧 二、外部中断配置流程(以PA0为例)

1. 时钟使能

// 使能GPIOA和AFIO时钟(APB2总线) RCC->APB2ENR |= (1 << 2) | (1 << 0); // 位2: GPIOAEN, 位0: AFIOEN[2](@ref)[5](@ref)2. GPIO模式配置

// 配置PA0为上拉输入 GPIOA->CRL &= ~0x0000000F; // 清除原有配置 GPIOA->CRL |= 0x00000008; // 设置为上拉输入模式 (CNF=10, MODE=00) GPIOA->ODR |= 0x00000001; // 上拉使能3. EXTI线路映射

// 将PA0映射至EXTI0线 AFIO->EXTICR[0] &= ~0x0000000F; // 清除EXTI0配置 AFIO->EXTICR[0] |= 0x00000000; // 0000表示PA04. 触发方式与中断使能

// 下降沿触发 & 使能EXTI0中断线 EXTI->FTSR |= (1 << 0); // 下降沿触发 EXTI->IMR |= (1 << 0); // 使能EXTI0中断5. NVIC配置

// 使能EXTI0中断(中断号6) NVIC->ISER[0] |= (1 << 6); // ISER[0]的bit6对应EXTI0[2](@ref)[7](@ref)// 设置优先级(假设分组2:2位抢占+2位响应) uint8_t priority = (0x01 << 2) | 0x01; // 抢占优先级1,响应优先级1 NVIC->IP[6] = priority << 4; // IP[6]对应EXTI0,优先级值写入高4位三、中断优先级分组详解

通过

SCB->AIRCR的位10-8设置优先级分组方案:

分组 AIRCR[10:8] 抢占优先级位宽 响应优先级位宽 应用场景 组0 111 0位(无抢占) 4位(16级) 无嵌套的简单系统 组1 110 1位(2级) 3位(8级) 中等嵌套需求 组2 101 2位(4级) 2位(4级) 常用配置(平衡嵌套与响应) 组3 100 3位(8级) 1位(2级) 高嵌套需求 组4 011 4位(16级) 0位(无响应) 严格抢占控制 配置代码示例:

void NVIC_PriorityGroupConfig(uint32_t group) {uint32_t temp = SCB->AIRCR;temp &= ~0x00000700; // 清除原分组temp |= 0x05FA0000 | (group << 8); // 写入密钥+新分组SCB->AIRCR = temp; } // 调用:NVIC_PriorityGroupConfig(0x05); // 组2配四、中断服务函数(ISR)关键事项

- 函数声明:需与启动文件中的弱定义名称一致(如

EXTI0_IRQHandler)。- 清除挂起位:在ISR末尾必须清除中断标志,否则会持续触发:

void EXTI0_IRQHandler(void) {// 处理逻辑(如按键检测)EXTI->PR = (1 << 0); // 写1清除EXTI0挂起位 }

- 执行效率:ISR应短小精悍,避免复杂逻辑或阻塞调用(如delay_ms()),耗时任务应移交下半部机制(如工作队列)。

五、调试常见问题

- 中断未触发:

- 检查时钟使能(GPIO、AFIO、外设时钟)。

- 确认NVIC与EXTI中断线均使能(

ISER和IMR)。- 验证GPIO模式是否为输入(浮空/上拉/下拉)。

- 优先级配置错误:

- 确保整个系统仅设置一次优先级分组(重复设置导致紊乱)。

- 优先级数值需在分组位宽范围内(如组2中抢占优先级值0~3有效)。

六、扩展应用场景

- 多中断线复用:同一EXTI线(如EXTI0)可动态切换映射到不同引脚(PA0/PB0),需重配

AFIO_EXTICR。- 中断嵌套优化:高抢占优先级中断可打断低优先级ISR,适用于实时控制系统(如电机紧急制动)。

- 低功耗管理:在休眠模式中,配置唤醒中断(如EXTI线+上升沿触发)以恢复系统运行。

通过精准配置上述寄存器,可构建高效可靠的中断响应系统,满足从基础外设控制到实时多任务调度的复杂需求。

16.异常向量表

异常向量表(Exception Vector Table)是计算机体系结构(尤其是ARM架构)中用于处理异常和中断的核心数据结构。它定义了处理器在遇到特定异常事件(如复位、中断、指令错误等)时应跳转执行的代码位置。以下从多个维度详细解析其概念:

一、基本定义与位置

结构与组成

异常向量表是一组连续的内存地址,每个地址对应一种异常类型的处理程序入口。例如:

- 复位异常:0x00000000

- 外部中断(IRQ):0x00000018

- 快速中断(FIQ):0x0000001C 每个条目通常存储一条跳转指令(如

LDR PC, =Handler_Address),指向实际的异常处理函数。物理位置

在传统ARM架构中,向量表固定位于内存低地址(如0x00000000)。但现代系统(如ARMv8)通过**向量基址寄存器(VBAR_ELx)**动态配置基地址,允许开发者将向量表置于任意内存区域(如Flash起始地址0x08000000)。

二、核心功能与作用

异常响应机制

当异常发生时,硬件自动完成以下步骤:

- 切换处理器模式(更新CPSR寄存器);

- 保存返回地址到

LR_<mode>;- 根据异常类型跳转到向量表对应条目执行处理程序。

关键应用场景

- 快速错误处理:如数据访问错误触发“数据中止异常”,跳转至修复或日志记录代码。

- 中断路由:外设中断(IRQ)触发后,通过向量表调用驱动服务例程。

- 系统安全:非法指令等异常可触发安全监控程序,阻止恶意代码执行。

三、ARM架构的演进与差异

- ARMv7(AArch32)

- 每个向量条目仅4字节,通常仅容纳一条跳转指令。

- 向量表固定偏移量为4字节递增(如复位0x00、IRQ0x18)。

- ARMv8(AArch64)

- 动态基址:通过

VBAR_EL1/2/3寄存器设置每级异常级别(EL1-EL3)的独立向量表。- 扩展条目:每个条目占128字节(32条指令),可直接写入处理逻辑,无需额外跳转。

- 多维度选择:条目选择取决于:

- 异常类型(同步、IRQ、FIQ、SError);

- 异常级别是否变化;

- 执行状态(AArch32/AArch64)。

四、初始化与代码示例

- 初始化步骤

- 定义向量表区域(如

.section .vectors);- 填充各异常向量地址;

- 设置

VBAR_ELx寄存器指向向量表基址。- 代码片段(ARMv7)

AREA Vectors, CODE, READONLY LDR PC, Reset_Addr ; 复位向量 LDR PC, IRQ_Addr ; IRQ向量 ; ...其他向量 Reset_Addr DCD Reset_Handler ; 复位处理函数地址 IRQ_Addr DCD IRQ_Handler ; IRQ处理函数地址

跳转逻辑(Bootloader应用)

在双区Bootloader设计中,需将App的向量表复制到RAM并重定向向量基址,确保App中断正确触发。

五、实际应用场景

多级异常处理

高安全系统(如ATF固件)为不同异常级别(EL3监控模式、EL1内核态)分配独立向量表,实现权限隔离。

动态重定向

若硬件不支持修改向量基址(如某些MCU),需在Bootloader的向量表中添加跳转指令,将异常转发至App的处理程序。

调试与可靠性

开发者可通过覆盖默认向量(如未定义指令异常)注入调试代码,追踪非法操作。

总结

异常向量表是连接硬件异常与软件处理的核心枢纽,其设计直接影响系统的实时性、安全性和可维护性。在ARM架构中,从固定低地址到动态可配基址的演进,体现了对灵活性和多级安全需求的适应。开发时需结合硬件特性(如VBAR支持)和场景需求(如Bootloader设计),确保异常处理路径高效可靠。

17.定时器

STM32定时器是微控制器中功能强大的硬件外设,用于实现精确计时、波形生成、事件捕获等任务。其设计灵活,支持多种工作模式和应用场景。以下从核心特性、工作原理、应用实现等方面进行系统解析:

一、定时器分类与特点

STM32定时器分为三类,功能逐级增强:

- 基本定时器(TIM6/TIM7)

- 仅支持时基生成(定时中断或触发DAC)

- 无外部引脚,适用于简单定时任务。

- 通用定时器(TIM2-TIM5)

- 支持时基、输入捕获(测量脉冲)、输出比较(生成PWM)、单脉冲模式等

- 具备4个独立通道,可连接外部信号。

- 高级控制定时器(TIM1/TIM8)

- 在通用定时器基础上增加死区控制、互补输出、刹车输入等功能

- 适用于电机控制、电源管理等复杂场景。

定时器类型 核心功能 典型应用场景 基本定时器 时基生成、中断触发 简单延时、周期性任务 通用定时器 输入捕获、输出比较、PWM生成 传感器信号处理、LED控制 高级定时器 互补输出、死区控制、刹车输入 电机驱动、数字电源

二、工作原理与时基单元

定时器的核心是时基单元,由三个关键寄存器构成:

- 预分频器(PSC)

- 对时钟源分频,降低计数频率。分频系数 =

PSC + 1。- 例:系统时钟84MHz,设置

PSC=83,则计数频率为1MHz(84MHz / 84)。- 计数器(CNT)

- 16位或32位寄存器,根据分频后的时钟信号递增/递减计数。

- 自动重装载寄存器(ARR)

- 设定计数上限,当CNT达到ARR时触发溢出事件(更新中断)。

- 溢出时间公式:$T_{out} = \frac{(ARR+1) \times (PSC+1)}{T_{clk}}$ 其中 $T_{clk}$ 为输入时钟频率(单位MHz),$T_{out}$ 为溢出时间(单位μs)。

三、计数模式详解

STM32支持三种计数模式,适应不同应用需求:

- 向上计数模式

- 从0计数至ARR值,溢出后归零并触发中断。

- 适用场景:周期性任务(如LED闪烁)。

- 向下计数模式

- 从ARR值递减至0,溢出后重新加载ARR值。

- 适用场景:倒计时控制。

- 中央对齐模式

- 先向上计数至ARR-1,再向下计数至1,形成对称波形。

- 适用场景:PWM输出(减少开关器件损耗)。

四、功能应用场景

精确延时

- 通过计算PSC和ARR配置定时周期,替代软件延时(不精准)。

// 示例:1ms延时函数(系统时钟84MHz) void delay_ms(uint32_t ms) {TIM2->PSC = 84000 - 1; // 分频至1kHzTIM2->ARR = ms; // 重载值=延时毫秒数TIM2->CR1 |= TIM_CR1_CEN; // 启动计数器while (!(TIM2->SR & TIM_SR_UIF)); // 等待溢出标志TIM2->SR &= ~TIM_SR_UIF; // 清除标志 }PWM生成

- 通过输出比较模式,调节占空比控制外设(如LED亮度、电机转速)。

- 占空比 = $\frac{CCR}{ARR} \times 100\%$(CCR为比较寄存器值)。

输入捕获

- 测量外部信号脉冲宽度(如编码器信号)。

- 原理:记录信号边沿触发时计数器的值,计算时间差。

多任务调度

- 多个定时器协同工作(如TIM3控制LED闪烁,TIM4触发串口通信)。

五、配置与编程指南

以通用定时器TIM3为例,配置步骤:

使能时钟

RCC->APB1ENR |= RCC_APB1ENR_TIM3EN; // 使能TIM3时钟配置时基参数

TIM3->PSC = 8399; // 84MHz分频为10kHz (8400-1) TIM3->ARR = 999; // 计数1000次(周期100ms) TIM3->CR1 |= TIM_CR1_DIR_DOWN; // 向下计数模式启用中断

TIM3->DIER |= TIM_DIER_UIE; // 使能更新中断 NVIC_EnableIRQ(TIM3_IRQn); // 注册中断向量 NVIC_SetPriority(TIM3_IRQn, 1); // 设置优先级启动定时器

TIM3->CR1 |= TIM_CR1_CEN; // 启动计数器编写中断服务函数

void TIM3_IRQHandler(void) {if (TIM3->SR & TIM_SR_UIF) {TIM3->SR &= ~TIM_SR_UIF; // 清除中断标志// 用户代码(如翻转LED)} }

总结

STM32定时器是嵌入式系统的核心模块,其灵活性和强大功能使其适用于从简单延时到复杂电机控制的各种场景。开发者需深入理解时基配置、计数模式及中断机制,结合具体需求选择合适的工作模式。通过合理配置PSC和ARR,可实现纳秒级至秒级的高精度定时,显著提升系统效率与可靠性。

18.定时器和看门狗、RTC、蜂鸣器的关系

定时器、看门狗(Watchdog Timer, WDT)、实时时钟(RTC)和蜂鸣器在嵌入式系统中均与时间管理相关,但功能定位和协作方式各有不同。它们的关系可概括为:定时器是基础计时单元,看门狗是系统监控器,RTC是持久时间记录器,蜂鸣器是定时驱动的执行器。以下是详细解析:

一、定时器:时间管理的核心基础

定时器是SoC中最常见的外设,本质是一个计数器,通过固定时钟周期累加或递减实现时间测量。

- 工作原理:

- 时钟源(如APB总线)经分频器生成周期信号,计数器(如TCNT)根据该信号增减,触发中断或事件。

- 定时时间公式:

定时周期 = 计数值 × 时钟周期。- 功能扩展:

- PWM输出:驱动蜂鸣器、电机等,通过调节占空比控制音调或转速。

- 中断触发:执行周期性任务(如数据采集),解放CPU资源。

二、看门狗:基于定时器的系统守护者

看门狗本质是一种特殊定时器,但增加了复位功能,用于检测系统故障。

- 工作原理:

- 初始化后,计数器开始递减,需程序定期“喂狗”(重置计数器)。若超时未喂狗,触发复位或中断。

- 例:充电器IC中,看门狗超时可能强制复位MCU或切换电源路径。

- 类型差异:

- 独立看门狗(IWDG):独立时钟源,主CPU故障时仍可复位系统。

- 窗口看门狗(WWDG):需在特定时间窗口内喂狗,否则复位,对时序要求更严。

三、RTC:独立运行的实时时钟

RTC与定时器核心区别在于:定时器关注时间段,RTC记录绝对时间点(年/月/日/时/分/秒)。

- 关键特性:

- 依赖独立晶振(如32.768kHz),备用电池供电,断电仍计时。

- 支持闹钟中断、唤醒低功耗系统(如STM32的待机模式唤醒)。

- 与系统协同:

- Linux系统启动时从RTC读取时间初始化系统时钟,关机时回写校准。

- 长期运行时需同步(如NTP网络校准或

adjtimex微调频率)。

四、蜂鸣器:定时器的执行输出单元

蜂鸣器是发声设备,依赖定时器产生特定频率的驱动信号。

- 驱动方式:

- 无源蜂鸣器:需定时器生成PWM方波(频率决定音调)。

- 有源蜂鸣器:通电即响,但仍可用定时器控制鸣响时长。

- 实现案例:

- 单定时器控制:中断中翻转引脚电平,生成固定频率声音。

- 双定时器协同:一个控制频率(音调),另一个控制持续时间(节奏)。

五、四者关系总结

组件 与定时器的关系 核心功能 典型应用场景 定时器 基础模块,提供计时能力 时间段测量、PWM生成 任务调度、蜂鸣器驱动 看门狗 特殊定时器,增加复位逻辑 系统故障检测与恢复 工业设备抗干扰 RTC 独立计时单元,关注时间点 持久化记录绝对时间 日志时间戳、闹钟功能 蜂鸣器 依赖定时器输出驱动信号 声音提示或报警 设备状态提示

六、协同工作示例

- 安全监控系统:

- RTC记录事件时间点 → 定时器周期性采集数据 → 看门狗监控程序运行 → 异常时复位并触发蜂鸣器报警。

- 低功耗设备:

- RTC闹钟唤醒休眠系统 → 定时器执行短期任务 → 完成后继续休眠,看门狗确保唤醒流程无阻塞。

定时器是嵌入式系统时间管理的“心脏”,看门狗是其“守护盾”,RTC是“持久记忆”,蜂鸣器则是“声音执行者”。四者各司其职,共同构建稳定可靠的嵌入式应用。

19.WDT-看门狗

CPU中的看门狗(Watchdog Timer,WDT)是一种硬件或软件监控机制,主要用于检测系统异常(如程序死锁、跑飞或硬件故障)并触发自动恢复措施(通常是系统复位)。其核心目标是提升系统的可靠性与稳定性,尤其在嵌入式系统、服务器等无人值守环境中至关重要。

一、基本工作原理

- 定时计数与喂狗

- 看门狗本质是一个倒计时定时器,启动后从预设值开始递减计数。

- 系统正常运行时,需周期性重置定时器(称为“喂狗”),防止其超时。例如,通过写入特定寄存器或发送电平信号实现。

- 超时复位

- 若系统故障导致未按时喂狗,定时器溢出(减至0),看门狗会触发复位信号强制CPU重启,使系统恢复初始状态。

💡 形象比喻:看门狗如同一条需定时投喂的狗,若超时未喂食,它就会“咬人”(复位系统)。

二、类型与特点

根据实现方式,看门狗分为两类:

- CPU内部看门狗

- 集成于CPU内部,通过软件配置定时器实现。

- 优点:灵活性高,可编程超时时间,可随时禁用。

- 缺点:依赖CPU初始化,若程序在启动前崩溃或禁用了看门狗,则失效。

- 独立硬件看门狗

- 外部专用芯片(如CAT706),与CPU通过GPIO连接。

- 优点:上电即工作,无法禁用,可靠性更高(不依赖CPU时钟)。

- 缺点:超时时间固定,灵活性低。

三、STM32中的典型实现

以STM32微控制器为例,包含两种看门狗:

- 独立看门狗(IWDG)

- 时钟源:低速内部时钟(LSI),独立于主系统时钟。

- 适用场景:高可靠性需求(如主时钟故障时仍有效)。

- 窗口看门狗(WWDG)

- 时钟源:主时钟分频(如HCLK)。

- 特点:需在指定时间窗口内喂狗,过早或过晚均触发复位,适合时序敏感场景。

四、应用与局限性

- 应用场景:

- 嵌入式设备(工业控制、物联网设备)。

- 服务器/实时系统,应对程序死锁、外部干扰。

- 局限性:

- 无法修复故障根源,仅提供恢复机制。

- 复位期间服务中断,可能造成数据丢失(需额外保护机制)。

五、软件控制示例

在Linux系统中,用户可通过设备文件操作看门狗:

int fd = open("/dev/watchdog", O_WRONLY); // 启动看门狗 write(fd, "\\0", 1); // 喂狗(写入任意字符) close(fd); // 关闭看门狗需周期调用

write()喂狗,否则超时触发重启。总结

看门狗是CPU的“安全卫士”,通过硬性监控-复位机制保障系统持续运行。其设计平衡了灵活性与可靠性:内部看门狗适合可配置场景,外部独立芯片则用于高鲁棒性需求。正确使用时需注意喂狗周期匹配系统业务逻辑,避免误复位。

20.RTC-实时时钟

一、RTC基本定义与核心功能

实时时钟(RTC) 是一种独立计时集成电路,用于持续提供精确的时间和日期信息,即使在系统断电时也能通过备用电源(如纽扣电池)维持运行。其核心功能包括:

- 时间追踪:精确记录年、月、日、时、分、秒,支持12/24小时制。

- 日历功能:自动处理闰年、月份天数调整。

- 闹钟与中断:支持多组闹钟设置和周期性中断,用于定时任务或唤醒低功耗设备。

- 时间戳记录:通过外部引脚触发记录事件发生的精确时间,用于日志或调试。

- 电源备份:主电源断开时自动切换至电池供电,确保时间连续性。

二、核心工作原理

- 时钟源

- 晶振频率:通常采用 32.768 kHz 石英晶振,因其为 $2^{15}$,经15级分频后可精准得到1Hz秒信号。

- 时钟源选择:可选外部晶振(LSE)、内部RC振荡器(LSI)或分频后的高速时钟(HSE),其中LSE精度最高且支持低功耗模式。

- 计数器与分频器

- 晶振信号经分频器转换为秒脉冲,驱动计数器累加时间值(如32位秒计数器可计时约136年)。

- 时间数据以BCD码或二进制格式存储于寄存器(如

RTC_TIME和RTC_DATE),并自动校验合法性(如拒绝“32日”等非法值)。- 电源管理

- 双电源设计:主电源(VCC_PSAUX)和备用电池(如CR2032),断电时无缝切换。

- 低功耗特性:典型电流低至 250nA,适用于物联网设备等电池供电场景。

- 通信接口

- 通过 I²C、SPI 等接口与主控芯片交互,实现时间设置与读取。

三、技术演进

- 早期RTC:并行接口、高功耗(约0.5μA),无闰年处理功能。

- 中期RTC:串行接口(I²C/SPI)、功耗降至0.5μA以下,集成万年历和自动闰年调整。

- 新一代RTC:

- 超低功耗(250nA)与小封装(2×2mm)。

- 内置温度补偿,精度达 ±3.4ppm(-40℃~85℃)。

- 抗漏电设计,增强工业环境稳定性。

四、应用场景

- 消费电子

- 智能手表、数码相机的时间显示与闹钟功能。

- 工业与物联网

- 数据记录仪的时间戳标记、传感器定时唤醒。

- 汽车电子

- 车载系统维护提醒、驾驶时长记录。

- 服务器与网络设备

- 日志时间同步、故障时间定位。

- 安防系统

- 监控录像时间标识、报警事件同步。

五、选型与设计要点

- 关键参数

- 精度:温补RTC精度达±3.4ppm,普通RTC约±5ppm。

- 功耗:电池寿命敏感场景选择<1μA的型号。

- 接口:I²C接口简化布线,SPI适用于高速通信。

- 设计注意事项

- 晶振选型:外部晶振需远离干扰源,布局时缩短走线。

- 电源隔离:备用电池电路需防止漏电,添加二极管隔离。

- 软件校准:利用内部RC时钟源校准频率偏差(如CW32L083的自动校准)。

六、编程示例(STM32)

// 1. 初始化RTC与时钟源 void RTC_Init(void) {RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR | RCC_APB1Periph_BKP, ENABLE);PWR_BackupAccessCmd(ENABLE); // 启用备份寄存器访问RCC_LSEConfig(RCC_LSE_ON); // 启动外部32.768kHz晶振while (RCC_GetFlagStatus(RCC_FLAG_LSERDY) == RESET); // 等待晶振就绪RCC_RTCCLKConfig(RCC_RTCCLKSource_LSE); // 选择LSE为RTC时钟源RCC_RTCCLKCmd(ENABLE); // 使能RTC时钟RTC_WaitForSynchro(); // 等待同步 }// 2. 设置时间 void RTC_SetTime(uint8_t hour, uint8_t min, uint8_t sec) {RTC_TimeTypeDef sTime;sTime.RTC_Hours = hour;sTime.RTC_Minutes = min;sTime.RTC_Seconds = sec;RTC_SetTime(RTC_Format_BIN, &sTime); // BIN格式写入 }// 3. 读取时间 void RTC_GetTime(uint8_t *hour, uint8_t *min, uint8_t *sec) {RTC_TimeTypeDef sTime;RTC_GetTime(RTC_Format_BIN, &sTime);*hour = sTime.RTC_Hours;*min = sTime.RTC_Minutes;*sec = sTime.RTC_Seconds; }

总结

RTC是嵌入式系统的“时间守护者”,通过 晶振分频+计数器+电池备份 实现全时区精准计时。选型需平衡 精度、功耗与接口需求,设计时注重晶振布局和电源隔离。在物联网低功耗设备、工业时间戳记录等场景中不可或缺,未来将向 更高集成度(如融合温补电路)和 更小封装 发展。

21.BCD码和RTC的关系

BCD码(二进制编码的十进制)与实时时钟(RTC)的关系主要体现在时间数据的存储、表示和硬件交互设计上。以下是两者的核心关联及技术细节:

一、BCD码在RTC中的核心作用

时间数据的标准化存储

RTC内部的时间寄存器(如年、月、日、时、分、秒)通常以BCD格式存储。例如:

- 十进制时间

23:59:50→ BCD码表示为0010 0011 : 0101 1001 : 0101 0000(每个字段4位一组)。- 优势:直接对应十进制数字,避免二进制转换的复杂性,提升硬件处理效率。

自动日历逻辑的实现

RTC需处理闰年、月份天数差异等复杂日历规则。BCD码的分字段存储特性(如月份十位仅需1位,日期十位仅需2位)简化了硬件逻辑设计。例如:

BCDMON寄存器:月份十位仅占1位(0或1),个位占4位。BCDDATE寄存器:日期十位占2位(0-3),个位占4位。抗干扰与数据完整性

BCD码仅使用0-9的合法组合(0000-1001),非法值(1010-1111)可被硬件检测为错误,增强系统鲁棒性。

二、硬件设计优势

简化显示驱动

七段数码管、LCD屏等显示设备可直接使用BCD码驱动,无需额外译码电路。例如:

- 数码管显示数字“5”时,直接输入BCD码

0101即可点亮对应段位。低功耗与高效接口

RTC常通过I²C/SPI等串行接口与主控通信。BCD码的紧凑格式(每数字4位)减少数据传输量,降低功耗,尤其适合电池供电场景(如IoT设备)。

三、软件交互中的转换处理

BCD与二进制的转换

RTC寄存器读取的BCD数据需转换为二进制(BIN)格式供CPU计算,写入时需反向转换。例如STM32中的转换函数:

// BCD转二进制 uint8_t bcd_to_bin(uint8_t bcd) {return ((bcd >> 4) * 10) + (bcd & 0x0F); // 高4位为十位,低4位为个位 } // 二进制转BCD uint8_t bin_to_bcd(uint8_t bin) {return ((bin / 10) << 4) | (bin % 10); }RTC配置中的格式选择

部分RTC芯片(如STM32)支持

RTC_Format_BCD和RTC_Format_BIN双模式:

- BCD模式:直接读写寄存器(如

RTC->BCDHOUR = 0x23表示23时)。- BIN模式:需软件转换,适合频繁计算的场景。

四、实际应用场景

嵌入式系统

- 路由器、智能电表使用RTC的BCD码记录事件时间戳,断电后由纽扣电池维持计时。

- 汽车电子:仪表盘显示车速/油量时,BCD码直接驱动数码管。

高精度时间同步

温补RTC(如±3.4ppm精度型号)通过BCD格式存储时间,结合GPS/NTP校准,用于基站、服务器日志同步。

实时操作系统(RTOS)

RTC的滴答计数器(Ticker)以BCD格式提供定时中断,触发任务调度。

总结

BCD码是RTC实现高效、可靠时间管理的核心技术:

- 硬件层面:简化电路设计,直接驱动显示设备,降低功耗。

- 软件层面:需与二进制格式转换以平衡可读性与计算效率。

- 场景适配:从消费电子到工业控制,BCD码的直观性和抗干扰性使其成为RTC的通用时间表示方案。

未来随着RTC向更高精度(如±1ppm)发展,BCD码仍将作为基础数据格式,结合温度补偿和网络校准技术提升系统可靠性。

22.PWM-脉宽调制

以下是关于单片机中PWM(脉冲宽度调制)技术的详细解析,结合核心原理、实现方式、配置方法及应用场景进行系统说明:

一、核心原理与关键参数

基本概念

PWM通过调节数字脉冲的宽度(占空比)控制模拟电路,实现数字信号模拟连续变量的效果。其理论基础是面积等效原理:不同形状的脉冲在惯性系统(如电感、电容)上产生的平均效果相同。

关键参数

频率(Hz):1秒内脉冲周期数,决定输出平滑度(高频减少纹波,但增加开关损耗)。

占空比(%):高电平时间占周期的比例,直接控制平均输出电压。

计算公式:平均电压 = 电源电压 × 占空比

例如:5V电源,50%占空比 → 平均输出2.5V。

周期(T):单个脉冲的持续时间,T = 1/频率。

二、单片机中的PWM实现方式

1. 软件模拟PWM

原理:通过定时器中断或循环延时控制IO口电平切换。

缺点:占用CPU资源,精度受中断延迟影响,仅适用于低频场景(如LED调光)。

示例(51单片机):

void Timer0_ISR() interrupt 1 {if (PWMOUT == 1) {TH0 = LowRH; TL0 = LowRL; // 切换低电平PWMOUT = 0;} else {TH0 = HighRH; TL0 = HighRL; // 切换高电平PWMOUT = 1;} }2. 硬件PWM模块

- 原理:利用单片机内置定时器自动生成PWM,无需CPU干预。

- 优势:精度高、资源占用低,支持高频输出(如电机控制)。

- 配置核心寄存器:

- 预分频器(PSC):分频系统时钟,设定计数频率。

- 自动重装载值(ARR):决定PWM周期(T = (ARR+1) / 分频后时钟)。

- 比较寄存器(CCRx):设定占空比(脉宽 = CCRx / ARR)。

硬件 vs 软件实现对比:

特性 硬件PWM 软件模拟PWM 精度 高(纳秒级) 低(受中断延迟影响) CPU占用 低(自动输出) 高(需持续干预) 适用场景 电机控制、电源转换 简单LED调光、低频应用

三、配置与编程示例(以STM32为例)

1. 硬件初始化步骤:

// 1. 使能时钟 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE); RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2, ENABLE);// 2. 配置GPIO为复用推挽输出 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; GPIO_Init(GPIOA, &GPIO_InitStructure);// 3. 定时器时基配置 TIM_TimeBaseStructure.TIM_Prescaler = 8399; // 分频至10kHz TIM_TimeBaseStructure.TIM_Period = 999; // 周期1ms (频率1kHz) TIM_TimeBaseInit(TIM2, &TIM_TimeBaseStructure);// 4. PWM模式配置 TIM_OCInitStructure.TIM_OCMode = TIM_OCMode_PWM1; TIM_OCInitStructure.TIM_Pulse = 500; // 占空比50% TIM_OC1Init(TIM2, &TIM_OCInitStructure);// 5. 启动PWM TIM_Cmd(TIM2, ENABLE);2. 动态调节占空比:

void PWM_SetDuty(TIM_TypeDef* TIMx, uint16_t duty) {uint16_t pulse = (TIMx->ARR + 1) * duty / 100;TIMx->CCR1 = pulse; // 修改通道1的占空比 }

四、典型应用场景

- LED调光

- 通过占空比调节亮度(>200Hz避免人眼频闪)。

- 示例:10%占空比亮度最暗,90%占空比接近全亮。

- 电机速度控制

- 直流电机:占空比正比于转速(如30%占空比对应30%最大转速)。

- 步进电机:PWM脉冲数控制步进角度,频率控制转速。

- 电源管理

- 开关电源(Buck/Boost电路):调节占空比稳定输出电压。

- 光伏逆变器:SPWM/SVPWM技术将直流转为交流。

- 音频与通信

- DAC模拟:PWM经低通滤波还原模拟信号。

- 射频调制:脉冲宽度编码增强抗干扰能力。

五、优势与挑战

- ✅ 优势:

- 高效节能:开关损耗低(效率>90%)。

- 精确控制:数字抗干扰,支持微秒级调节。

- 简化电路:替代线性稳压器,减少发热。

- ⚠️ 挑战:

- 高频噪声:需加LC滤波或屏蔽降低EMI。

- 器件要求:高频场景需快恢复二极管/低栅极电荷MOSFET。

总结

PWM是单片机中通过数字脉冲宽度调制模拟输出的核心技术,其核心在于占空比控制与面积等效原理。无论是软件模拟还是硬件模块实现,均需合理配置频率、占空比以适应不同场景(如LED调光需>200Hz,电机控制需kHz级频率)。掌握PWM配置方法(如STM32的ARR/CCRx寄存器)及抗干扰设计,可显著提升嵌入式系统的控制精度与能效。

23.死区生成器

死区生成器(Dead Time Generator)是电力电子控制中的关键硬件或软件模块,主要用于在PWM(脉宽调制)信号中插入可控的时间间隔(死区时间),以防止功率开关器件(如MOSFET、IGBT)的上下桥臂同时导通,避免短路损坏。以下从核心原理、实现方式、应用场景及优化策略等方面系统解析:

一、核心原理与作用

1. 死区时间的定义

死区时间(Dead Time)指在互补PWM信号切换过程中,上管关断到下管导通(或反之)之间插入的一段无信号重叠时间。其核心作用是防止“直通”(Shoot-Through)现象——即上下桥臂同时导通导致电源短路,引发大电流烧毁器件。

2. 物理机制

- 开关延迟:功率器件的关断延迟(Turn-off Delay)通常大于导通延迟(Turn-on Delay)。若不加死区,关断延迟可能导致上下管短暂同时导通。

- 续流路径:死区期间,感性负载(如电机绕组)的电流通过反并联二极管续流,避免电压突变。

3. 死区效应与误差

死区会导致输出电压畸变(图1):

- 电流正方向(i>0):死区使输出电压损失 $U_{dc}/2 \times t_d$;

- 电流负方向(i<0):输出电压增加 $U_{dc}/2 \times t_d$ 。

图1:死区效应导致输出电压误差(黄色区域)。

二、实现方式与技术分类

1. 硬件实现

数字逻辑电路:通过逻辑门(与、或、非)和延时单元生成死区(图2)。

- 上管信号:原始信号延时 $t_d$ 后与原始信号“与”操作;

- 下管信号:延时信号与原始信号“或”操作后取反。

专用芯片:如专利技术中的死区生成电路,通过倍频器提升时钟精度,结合直通保护模块实时监测PWM信号。

单片机集成模块:如STM32的BDTR寄存器、LPC553X的eFlexPWM模块,通过配置寄存器直接设置死区时间。

// STM32设置死区时间示例(10μs) TIM2->BDTR |= (10 << TIM_BDTR_DTG_Pos); // DTG位写入时钟周期数[6](@ref)2. 软件实现

中断延时:在PWM中断服务程序中插入空操作(NOP)延时:

for (uint32_t i = 0; i < 10; i++) __asm__("nop"); // 10个NOP指令≈10μs延时[6](@ref)高级算法:在SVPWM等算法中嵌入死区补偿逻辑,结合电流方向动态调整占空比。

3. 仿真工具实现

Simulink模型:使用

Dead Zone模块或自定义SVPWM模型插入死区,参数化配置关断/导通延时:set_param('PWM Generator', 'dtuoff', '5e-6'); // 上管关断延时5μs set_param('PWM Generator', 'dtlon', '7e-6'); // 下管导通延时7μs[8](@ref)

三、关键参数与设计挑战

1. 死区时间计算

死区时间需根据器件开关特性设定:

- 最小值:大于开关管的关断延迟时间(Datasheet参数);

- 典型值:0.5–5μs(IGBT)或 10–100ns(SiC MOSFET)。

公式:$t_d = \text{关断延迟} - \text{导通延迟} + \text{裕量}$。

2. 设计挑战

问题 原因 解决方案 死区过长 输出电压损失,电机转矩脉动 动态补偿算法 死区过短 直通风险,器件烧毁 示波器监测+裕量设计 多通道不一致 电机抖动 硬件同步或专用发生器 死区补偿相位误差 电流过零检测不准 低通滤波+矢量角计算

四、典型应用场景

1. 电机驱动

- H桥/三相逆变器:死区生成器确保上下管不同时导通,保护IGBT模块(如电动汽车驱动)。

- 死区补偿:低速时通过电压补偿消除死区引起的转矩脉动(公式):$\Delta u = U_{dc} \times \frac{2T_d}{T_{pwm}} \times \text{sign}(i)$ 。

2. 开关电源

- Buck/Boost电路:防止同步整流管直通,提高转换效率(>90%)。

3. 屏幕触控优化

- Android死区生成器:屏蔽屏幕指定区域(如游戏防误触),通过修改输入事件处理机制实现。

五、死区补偿技术

死区导致的输出电压误差需通过补偿消除:

- 电流方向检测:

- 通过定子电流矢量角 $\theta = \theta_s + \arctan(i_q/i_d)$ 判断各相电流极性。

- 补偿电压生成:

- 在αβ坐标系注入补偿电压:$U_{\alpha\text{comp}} = \frac{2}{3} \left( \text{sign}(i_a) - \frac{1}{2}\text{sign}(i_b) - \frac{1}{2}\text{sign}(i_c) \right)$$U_{\beta\text{comp}} = \frac{2}{3} \left( \frac{\sqrt{3}}{2}\text{sign}(i_b) - \frac{\sqrt{3}}{2}\text{sign}(i_c) \right)$ 。

- 仿真验证:

- Simulink模型显示补偿后电流波形正弦度显著提升(图2)。

图2:死区补偿前后电机相电流对比(过零畸变消除)。

总结

死区生成器是电力电子系统的“安全卫士”,通过精准插入死区时间避免功率器件直通损坏。其实现需结合硬件特性(开关延迟)与系统需求(如电机控制精度),并通过补偿算法消除输出电压误差。未来随着SiC/GaN器件普及,纳秒级死区控制与自适应补偿技术将成为研究重点。

推荐实践:

- 电机控制:优先使用单片机硬件死区(如STM32 BDTR、LPC553X eFlexPWM);

- 高精度场景:选择专用死区生成芯片(抗干扰+纳秒级精度);

- 算法验证:通过Simulink模型预演死区效应及补偿效果。

24.链接脚本

链接脚本(Linker Script)是编译链接过程中的核心配置文件,用于指导链接器(如GNU ld)如何将输入文件(如目标文件

.o)中的程序段(Section)组合成输出文件(如可执行文件或库),并控制其在内存中的布局。其核心作用在于精确管理程序的内存地址映射、符号解析和段排列顺序。一、核心功能

- 内存布局控制

- 定义段的位置:指定程序段(如代码段

.text、数据段.data、未初始化数据段.bss)在内存中的加载地址(VMA,虚拟内存地址)和存储地址(LMA,加载内存地址)。例如,嵌入式系统中常将代码段定位到Flash地址(如0x08000000),而数据段定位到RAM地址(如0x24000000)。- 地址对齐:通过

ALIGN(n)确保段起始地址按指定字节对齐(如4字节对齐),提升内存访问效率。- 符号解析与重定位

- 定义全局符号:在脚本中声明符号(如

bss_start = .;),记录段的起始/结束地址,供程序代码直接引用(例如在C语言中用&bss_start获取BSS段地址)。- 解决外部引用:确保跨文件的全局变量和函数正确关联到内存地址(如

extern变量)。- 输入文件段映射

- 合并同类段:将多个输入文件的相同段(如所有

.text段)合并到输出文件的单一连续段中。- 指定文件顺序:控制关键代码的优先执行(如将启动文件

start.o置于代码段首)。二、脚本结构与语法

链接脚本主要由以下命令构成:

SECTIONS:核心命令,定义输出文件的段布局。 示例:SECTIONS {. = 0x30000000; /* 设置起始地址 */.text : { *(.text) } /* 合并所有输入文件的.text段 */.data : { *(.data) } /* 合并.data段 */.bss : { /* 合并.bss段并记录起止地址 */bss_start = .;*(.bss);bss_end = .;} }

MEMORY:定义物理内存区域(如ROM、RAM)及其属性(可读/可写)。

ENTRY:指定程序入口点(如ENTRY(_start))。

OUTPUT_FORMAT:设置输出文件格式(如ELF小端格式)。三、典型应用场景

- 嵌入式系统开发 定制内存布局以适应硬件约束(如分离Flash和RAM地址),优化启动速度和资源占用。

- 操作系统内核构建 控制内核符号表、初始化函数(如

__initcall)的位置,确保启动流程正确。- 性能优化 将关键代码段加载到高速RAM(如缓存锁定),或通过段重定位(

AT(LMA))实现运行时动态加载。四、与默认脚本的关系

链接器始终使用链接脚本。若未显式提供(

-T参数),则使用内置默认脚本。自定义脚本在复杂需求下不可或缺,例如需要精确控制段位置或定义特殊符号时。总结

链接脚本是链接过程的“蓝图”,通过控制段布局、符号解析和内存映射,直接影响程序的可执行结构、性能和硬件兼容性。其在嵌入式开发、内核构建等场景中尤为重要,是深入理解程序底层机制的关键工具。

25.Checksum-校验和机制

系统启动中的Checksum校验和是一种用于确保关键数据(如固件、引导程序或操作系统文件)在启动过程中完整性和一致性的错误检测机制。其核心原理是通过算法计算数据的校验值,并与预存值比对,若不一致则判定数据损坏,从而防止系统因文件篡改或损坏而异常启动。以下是其详细解析:

一、Checksum的基本概念与作用

定义与原理

Checksum是通过特定算法(如累加求和、哈希函数)将数据转换为固定长度的校验值(如8位、16位)。系统启动时,BIOS/UEFI或引导程序会重新计算关键数据的校验值,并与预先存储的值比对。若两者一致,说明数据未损坏;若不一致,则中断启动并报错。

核心目的

- 数据完整性验证:检测固件、引导程序等是否被篡改或损坏(如传输错误、存储介质故障)。

- 安全防护:防止恶意代码注入或硬件故障导致系统异常启动。

二、系统启动中Checksum的应用场景

- BIOS/UEFI固件验证

- 开机时,BIOS首先对自身代码计算Checksum,若与存储值不匹配,则提示“Checksum Error”并停止启动(如CMOS电池失效导致配置丢失)。

- 例如:BIOS校验失败可能导致无法进入POST(上电自检),需重置或刷新固件。

- 引导加载程序(Bootloader)验证

- 如GRUB(Linux)或Windows Boot Manager在加载内核前,会校验引导文件的Checksum,确保未被破坏。

- Linux系统可通过工具(如

sha1sum)生成引导文件的哈希值,Bootloader比对后决定是否继续启动。- 操作系统内核与驱动校验

- 现代操作系统(如Linux)在挂载文件系统时,通过元数据中的Checksum验证内核文件完整性。若校验失败,系统可能进入恢复模式或提示文件损坏。

- 示例:Linux的Btrfs/ZFS文件系统默认启用Checksum,实时监控数据一致性。

- 固件升级(刷机)过程

- 刷机工具(如Flash_Tool)在写入固件前计算文件的Checksum,若与设备预设值不符,则报错终止,避免写入损坏文件导致设备“变砖”。

- 解决方法:使用专用工具(如

CheckSum_Gen.exe)重新生成固件的校验值并更新配置文件(如**um.ini)。

三、Checksum的计算方法与类型

简单累加和

- 原理:将数据字节累加后取模(如模256),生成校验值。

- 示例:字符串“ABCD”的ASCII码和为

65+66+67+68=266,取模后Checksum为10(266 % 256)。- 适用场景:嵌入式系统、串行通信(如RS-485协议)。

哈希算法(如SHA-256、MD5)

原理:通过复杂哈希函数(如SHA-256)生成唯一指纹,微小改动会导致结果剧变。

示例:Linux使用

sha256sum命令计算文件哈希值。代码实现(Python):

import hashlib def calculate_checksum(file_path):sha256_hash = hashlib.sha256()with open(file_path, "rb") as f:for byte_block in iter(lambda: f.read(4096), b""):sha256_hash.update(byte_block)return sha256_hash.hexdigest()与CRC的对比

特性 Checksum CRC 计算复杂度 低(加法/取模) 高(多项式除法) 错误检测能力 弱(仅检测单比特错误) 强(可检测多比特错误) 应用场景 轻量级场景(BIOS) 高可靠性场景(网络协议)

四、Checksum的优缺点与替代方案

- 优点

- 低开销:计算简单,对启动性能影响小(如BIOS校验仅需毫秒级时间)。

- 广泛兼容:适用于资源受限的嵌入式设备或基础固件。

- 局限性

- 弱错误检测:无法识别复杂错误(如数据位交换或多字节错误)。

- 无纠错能力:仅能报错,无法修复数据(需依赖备份或重新写入)。

- 替代方案

- CRC(循环冗余校验):适用于网络传输或存储设备,检测能力更强。

- ECC(纠错码):在内存等硬件中实时纠正比特错误,常见于服务器。

五、实际应用与故障处理

- 典型错误:刷机时出现“CheckSum Error”需重新生成固件校验值;BIOS校验失败需更换CMOS电池或刷新固件。

- 设计建议:

- 关键系统(如工业控制器)可结合Checksum与看门狗机制(Watchdog),实现错误检测与自动复位。

- 高安全场景推荐使用SHA-256等强哈希算法,避免Checksum被恶意绕过。

总结

系统启动中的Checksum是保障初始化阶段数据完整性的基础机制,尤其在固件、引导程序等关键环节不可或缺。尽管其错误检测能力有限,但凭借低计算开销和易实现性,仍是BIOS、嵌入式设备和文件系统的首选校验方案。在高可靠性场景中,可结合CRC或哈希算法提升防护强度。

26.ELF & BIN文件的关系

ELF(Executable and Linkable Format)文件和BIN(Binary)文件是程序编译后的两种关键格式,它们在结构、功能和应用场景上存在显著差异,但又有紧密的生成关系。以下从关系、区别、转换和应用场景四方面详细解析:

一、核心关系

生成依赖

BIN文件通常由ELF文件转换而来,是ELF的纯数据切片。编译器首先生成ELF文件(含完整元数据),再通过工具(如

objcopy)提取其代码段(.text)、数据段(.data)等关键部分,生成连续的二进制镜像(BIN文件)。转换命令示例:

arm-none-eabi-objcopy -O binary firmware.elf firmware.bin # ELF转BIN功能互补

- ELF:面向开发阶段,包含符号表、调试信息、重定位记录等,支持链接、调试和动态加载。

- BIN:面向部署阶段,仅含机器码,可直接烧录到硬件Flash或内存中执行,无需解析。

二、核心区别

对比维度 ELF文件 BIN文件 结构 分层结构(ELF头+程序头表+节头表+多节) 连续二进制流,无内部结构 内容 机器码+符号表+调试信息+重定位数据 纯机器码,无额外元数据 文件大小 较大(含冗余信息) 较小(仅保留有效数据) 地址处理 含虚拟地址标记( e_entry指定入口)无地址信息,需外部指定烧录位置 可调试性 ✅ 支持源码级调试(GDB) ❌ 无符号信息,仅能反汇编 适用阶段 开发、链接、动态加载 量产烧录、裸机执行 💡 典型场景对比:

- 调试程序崩溃:需ELF文件定位源码行(如

gdb -e firmware.elf)。- 烧录STM32芯片:用BIN文件通过ST-Link工具写入Flash(指定起始地址0x08000000)。

三、转换方法与限制

- ELF → BIN

- 工具:

objcopy(交叉编译工具链)。- 原理:剥离ELF的元数据,仅保留需加载的段(如

.text,.data)。- 限制:转换后丢失调试能力,需保留ELF副本用于调试。

- BIN → ELF(不可逆)

本质:BIN转ELF是伪转换,生成的ELF无原始符号表和重定位信息。

工具:可通过

objcopy将BIN包装为ELF,但仅填充基础头信息:objcopy -I binary -O elf32-littlearm input.bin output.elf用途:便于反汇编分析(如

objdump -d output.elf),但无法恢复高级调试功能。- ELF/BIN → HEX

- ELF转HEX:直接可行(

objcopy -O ihex input.elf output.hex)。- BIN转HEX:需手动指定基地址(因BIN无地址标记),工具如

bin2hex。

四、应用场景选择

- 操作系统环境(如Linux)

- ELF:直接执行(

./app),内核加载器解析程序头表,动态链接库(.so)。- BIN:通常不直接使用,除非内核引导等底层场景。

- 裸机/嵌入式系统

- BIN:烧录至Flash的首选,因无OS解析ELF头,需直接跳转到机器码入口。例:STM32上电后从0x08000000执行BIN镜像。

- ELF:仅用于调试(如JTAG连接时下载ELF,实时查看变量)。

- 固件分发与量产

- BIN/HEX:优先使用,体积小且兼容烧录器。HEX因含地址和校验,更防错。

- ELF:仅保留在开发端用于问题追踪。

总结

ELF与BIN是同一程序的两种表达形式:

- ELF是“开发视图”:丰富元数据支撑调试和链接,是编译的起点;

- BIN是“硬件视图”:纯净机器码适配物理内存,是部署的终点。 转换时需注意信息损耗(ELF→BIN可逆但丢失元数据,BIN→ELF不可逆)。在开发中保留ELF文件、发布时使用BIN/HEX,是平衡效率与功能的通用实践。

27.MMU-内存管理单元

MMU(Memory Management Unit,内存管理单元)是计算机硬件中的关键组件,负责处理CPU的内存访问请求,主要实现虚拟地址到物理地址的转换、内存保护及缓存控制等功能。其核心作用是为现代操作系统提供内存管理的硬件支持,确保系统安全性和多任务运行的稳定性。以下是MMU的详细解析:

一、核心功能

地址转换

MMU通过页表(Page Table)将程序使用的虚拟地址映射为实际的物理地址。每个进程拥有独立的虚拟地址空间(如32位系统为4GB),而MMU动态地将虚拟页面映射到物理内存的页帧(Page Frame)上。

- 转换过程:CPU发出虚拟地址 → MMU查询页表 → 返回物理地址 → 访问内存数据。

- 加速机制:MMU内置TLB(快表)缓存常用映射关系,减少页表查询延迟。

内存保护

MMU通过页表中的权限位(可读/可写/可执行)限制程序的内存访问:

- 防止进程越权访问其他进程或内核空间的内存(如用户程序试图修改内核数据);

- 非法操作会触发段错误(Segmentation Fault),由操作系统终止违规进程。

虚拟内存管理

MMU支持将部分内存数据暂存到磁盘(交换空间),使程序可使用超过物理内存容量的虚拟内存。当访问未加载的页面时,MMU触发缺页异常,操作系统从磁盘调入数据。

缓存与总线控制

在简单系统中,MMU还可能管理CPU高速缓存(Cache)和总线仲裁,优化数据访问效率。

二、工作原理

页表机制

- 页表由操作系统维护,存储虚拟页号到物理页帧号的映射关系;

- 多级页表(如x86的4级页表)减少内存占用。

地址转换流程

graph LR A[CPU发出虚拟地址] --> B{TLB命中?} B -->|是| C[直接获取物理地址] B -->|否| D[查询页表] D --> E[生成物理地址并更新TLB] E --> F[访问物理内存]

权限检查

MMU在转换地址时同步验证访问权限(如用户模式程序不可访问内核页面),失败则引发异常。

三、系统依赖性与应用场景

- 操作系统支持

- 必需MMU的系统:Linux、Windows等通用操作系统依赖MMU实现内存隔离与虚拟内存;

- 无需MMU的系统:部分嵌入式系统(如FreeRTOS)可在无MMU的SOC上运行,但仅支持有限的多任务与内存保护。

- 硬件集成方式

- 现代CPU(如x86、ARM)将MMU集成在核心内;

- 早期系统(如SUN工作站)采用独立MMU芯片。

四、重要性总结

MMU是现代计算系统的基石,它:

✅ 实现多进程隔离,避免内存冲突;

✅ 通过虚拟内存扩展可用内存空间;

✅ 提供硬件级安全防护,防止恶意代码破坏系统稳定性。

提示:MMU的具体实现(如页表结构、TLB大小)因处理器架构(x86/ARM/RISC-V)而异,需参考对应手册。