Linux开发——中断

前面我们已经了解了ARM内核的工作模式

ARM处理器支持多种工作模式,不同的模式决定了寄存器和系统的访问权限:

User 模式:非特权模式,大多数应用程序运行在此模式。

FIQ (Fast Interrupt Request):高速中断模式,响应高优先级中断。

IRQ (Interrupt Request):普通中断模式,响应低优先级中断。

Supervisor (SVC):管理模式,系统调用、复位后进入此模式。

Abort:存取异常模式,用于处理存储器访问错误。

Undef:未定义指令模式。

System:与User模式类似,但具备特权权限。

今天我们学习linux开发基础中的一个重点:中断。

硬件开发中最小系统:电源,时钟,控制。

中断学习是控制的重要环节,主要用于处理突发状况并维持原有状态运行。

中断流程

(1)中断源发出中断请求。

(2)CPU检查是否响应中断以及该终端是否被屏蔽。

(3)检查当前产生的中断的中断优先级。

(4)保护现场

(5)执行中断服务函数

(6)恢复现场

kernal:被打断的

外设: 发出中断

GPIO发出的中断:外部中断(EINT)

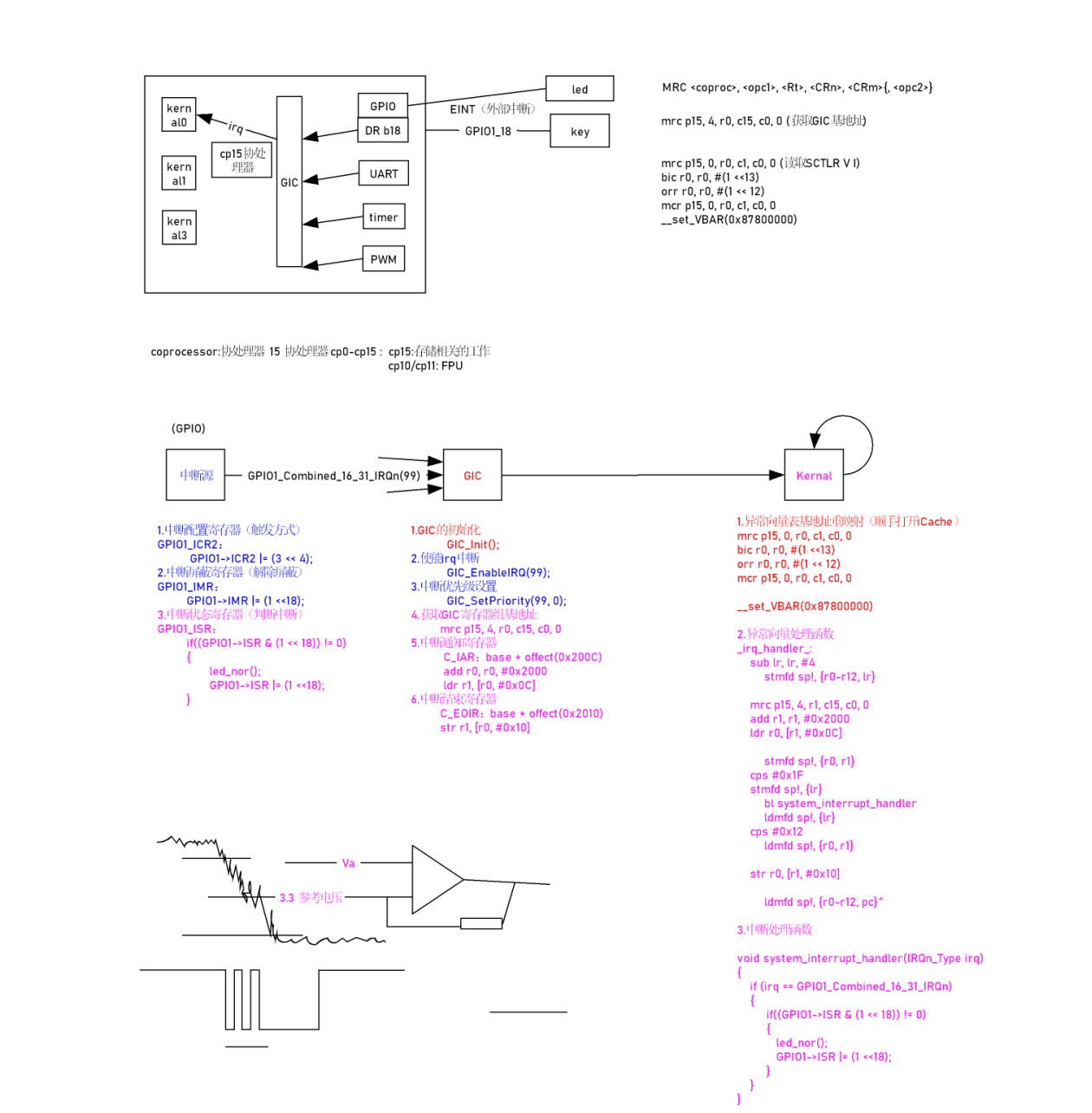

中断控制器GIC

GIC(Generic Interrupt Controller):通用的中断控制器

我们使用的IMX6ULL只有一个内核,图中所示只有processor 0

每个内核能够相应1020个中断源,其中0~15是SGI,16~31是PPI,能够作为外设中断源的是SPI32~1019

(2)Distributor(分发器):

(1)SGI(Software-generated Interrupt),软件中断:

由软件触发引起的中断,通过向寄存器GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信。

(2)PPI(Private Peripheral Interrupt),私有中断:

我们说了 GIC 是支持多核的,每个核肯定有自己独有的中断。这些独有的中断肯定是要指定的核心处理,因此这些中断就叫做私有中断;

(3) SPI(Shared Peripheral Interrupt),共享中断:

(注意!不是 SPI 总线那个中断),这类中断泛指所有的

(3)CPU interface x(CPU接口0-7):

II.参考文档:《IMX6ULL参考手册.pdf》

(1)3.2 Cortex A7 interrupts

Table 3-1. ARM Cortex A7 domain interrupt summary

中断编号:0 - 128

III.参考文档:《MCIMX6Y2.h》

IRQn_Type:0-159 外设中断;

(4)协处理器(coprocrssor):cp0-cp15

Cortex-A7技术参考手册:《Cortex-A7 Technical ReferenceManua.pdf》

位置:章节4 System Control

协处理器cp15:负责与存储类相关任务

(1)功能

• Overall system control and configuration. (所有系统控制与配置)

• Memory Management Unit (MMU) configuration and management.(MMU的配置与管理)

• Cache configuration and management. (Cache的配置与管理)

• Virtualization and security. (虚拟化和安全设置)

• System performance monitoring. (系统性能监视)

(2)寄存器组:c0-c15

• c0 registers on page 4-4.

• c1 registers on page 4-5.

• c2 registers on page 4-6.

• c3 registers on page 4-6.

• c4 registers on page 4-6.

• c5 registers on page 4-7.

• c6 registers on page 4-7.

• c7 registers on page 4-8.

• c8 registers on page 4-10.

• c9 registers on page 4-11.

• c10 registers on page 4-12.

• c11 registers on page 4-12.

• c12 registers on page 4-13.

• c13 registers on page 4-13.

• c14 registers on page 4-13.

• c15 registers on page 4-14.

(3)cp15寄存器读写

读 MRC<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

写 MCR<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

(4)中断相关寄存器组

c0 registers:

MIDR(Main ID Register):存储内核的一些基本信息

c1 registers:

SCTLR(System Control Register):

bit13:V

0 Normal exception vectors, base address 0x00000000. Software can remap this base address using

the VBAR.

1 High exception vectors, base address 0xFFFF0000. This base address is never remapped.

bit12:I

0 Instruction caches disabled, this is the reset value.

1 Instruction caches enabled.

demo:

mrc p15,0,r0,c1,c0,0

bic r0, r0, #(1 << 13)

orr r0, r0, #(1 << 12)

mcr p15,0,r0,c1,c0,0

c12 registers:

VBAR(Vector Base Address Register):

demo:

__get_VBAR(0x87800000);

c15 registers:

CBAR(Configuration Base Address Register):Holds the physical base address of the memory-mapped GIC registers.

demo:

mrc p15, 4, r0, c15, c0, 0