【FPGA 开发分享】如何在 Vivado 中使用 PLL IP 核生成多路时钟

EsteemPCB Academy 是一个专注于 FPGA、嵌入式系统与硬件开发的技术学习平台,致力于通过通俗易懂的课程内容,帮助工程师和学习者快速掌握前沿技术。

在他们的一支教学视频中,使用了 ALINX AX7020 FPGA 开发板,演示了如何在 Vivado 中调用 PLL(Phase-Locked Loop,相位锁定环)IP 核,实现不同频率的时钟信号生成。本图文教程基于该视频的完整过程整理而来,将介绍如何在 Verilog 代码中例化 PLL IP 核,编写 Verilog 仿真测试平台(Testbench),最后通过 JTAG 将设计烧录到实际的开发板。

原视频链接:

https://www.youtube.com/watch?v=B1T0t3xpvxM

ALINX AX7020 开发板:

https://alinx.com/en/detail/273

Zynq 7000 资料详情:

https://www.amd.com/en/products/adaptive-socs-and-fpgas/soc/zynq-7000.html#documentation

Vivado 下载安装:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/archive.html

在开始今天的主题之前,我先抛出一个问题。我们知道,目前使用的 AX7020 开发板自带一颗 50 MHz 的 PLSysRef 时钟。

那么,如果某个应用需要 100 MHz、250 MHz 甚至更高频率的时钟,该怎么实现呢?这时就需要用到 PLL(锁相环)。今天的视频主要讲解:

1. 什么是 PLL;

2. 如何在 Vivado 中使用 PLL IP 核。

接下来,我们会通过仿真展示如何利用 PLL IP 核实现时钟倍频,然后把程序烧录到实际的 AX7020 开发板,并观察输出波形。

(ALINX 基于 AMD Zynq 7000 SoC 开发板 AX7020)

Part 1:理解 FPGA 内部的 PLL

如果只想了解如何使用请直接滑到Part2~

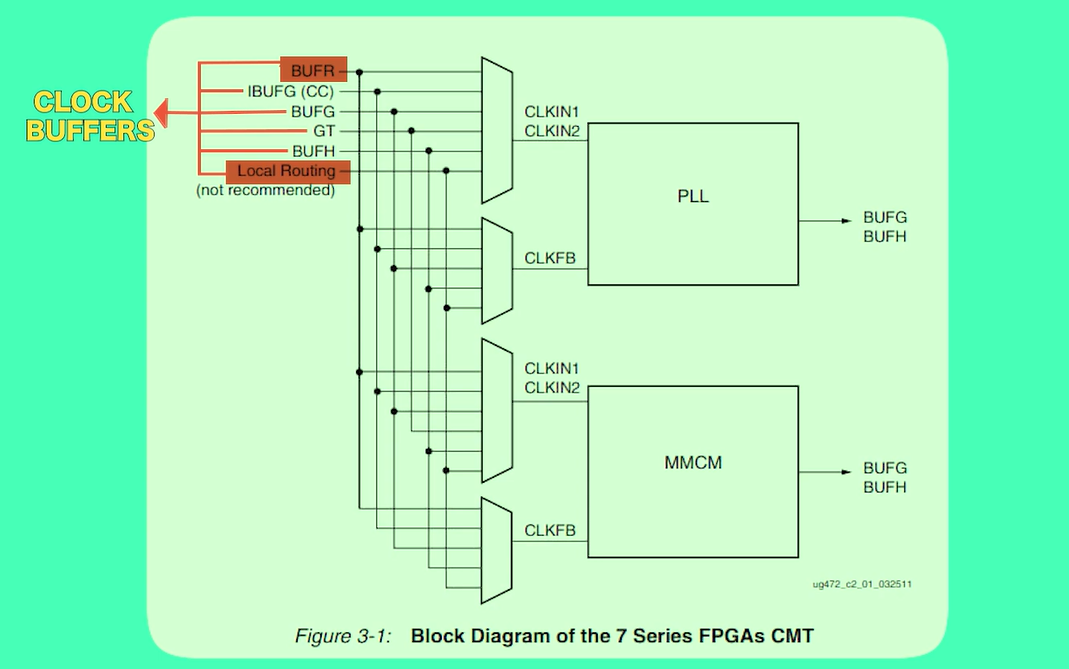

首先我们来看看 PLL 在 FPGA 内部是如何集成的。除了 PLL,FPGA 里还有其他的时钟管理资源,比如 MMCM(混合模式时钟管理器),它可以实现更高性能的相位同步和时钟合成。

PLL 在 FPGA 中是非常重要的资源。因为一个复杂的 FPGA 系统通常需要多个不同频率、不同相位的时钟信号,而这些功能都必须依靠 PLL 来实现。因此,一个 FPGA SoC 中 PLL 的数量,往往可以作为衡量其能力的一个重要指标。

回到 AX7020 开发板

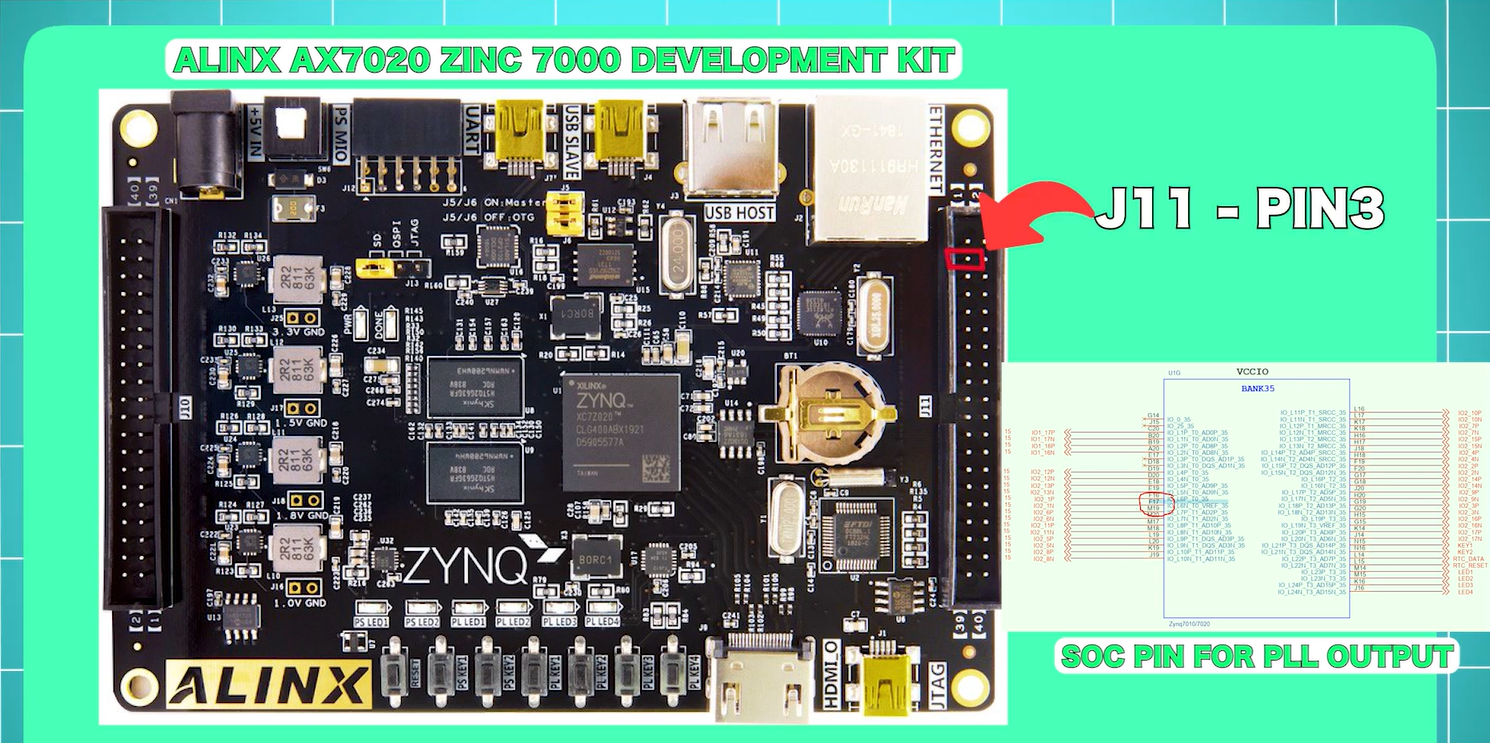

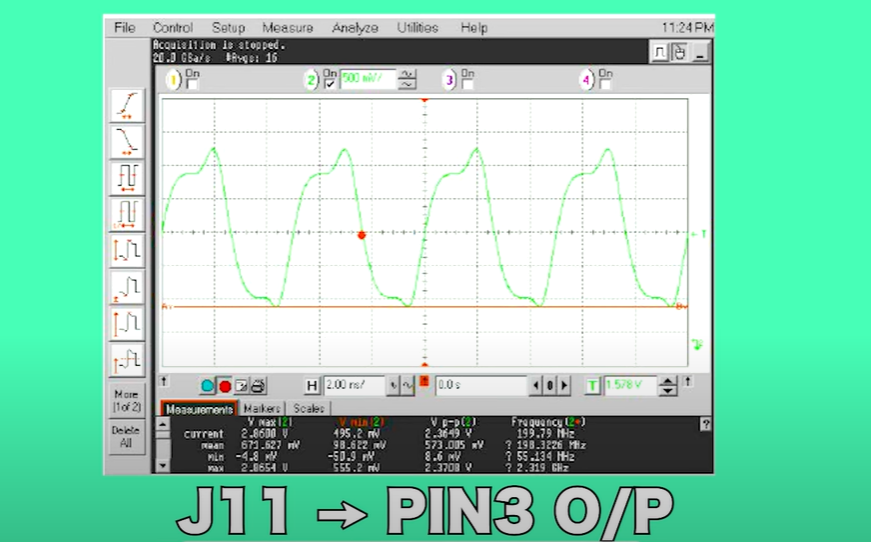

在 AX7020 Zynq 7000 开发板上,有一个引脚与 PLL 相连。你可以在屏幕上的示意图看到,我标注的部分是 J11 接口的第 3 脚,它直接输出来自 PLL 的时钟信号。这个引脚可以被用作外部应用的时钟源。除此之外,PLL 还有多个输出通道,可以在 Verilog 代码中调用。

在正式使用 PLL IP 核之前,我们先要理解它在 FPGA 内部的结构。

时钟管理单元

(Clock Management Tile, CMT)

在 Xilinx 7 系列 FPGA 中,芯片内部设计了专用的全局(Global)和区域(Regional)时钟资源,用来处理各种时钟需求。这些资源被称为时钟管理单元(Clock Management Tile, CMT),它们提供:

时钟频率合成(frequency synthesis)

时钟偏移校正(de-skew)

抖动抑制(jitter removal)

从下面的模块框图中可以看到:

从区域缓冲器(Buffer R)到本地布线的部分,都是时钟缓冲器;

这些缓冲器通过 FPGA 内部的时钟专用引脚相互连接;

PLL 和 MMCM 共用这些缓冲资源。

此外,从框图还能看到,如果要使用 PLL 的输出引脚,必须接入 Buffer G(全局时钟缓冲器) 或 Buffer H(水平时钟缓冲器),否则时钟信号无法被正确分发。

还记得我刚才提到的 J11 接口的第 3 脚吗?这个引脚实际上就是 Buffer G 或 Buffer H 的输出引脚之一,我们稍后会在实测中看到它的作用。

接下来,我们会先配置 PLL IP 核。通过它,我们可以对参考时钟(在本例中是 50 MHz)进行倍频或分频。随后,我们会在 J11 接口的第 3 脚上探测到对应的输出时钟。

简单来说,这里需要强调的一点是:

你可以根据应用对频率和相位的需求选择 MMCM 或 PLL。

在我们的案例中,输入时钟就是 50 MHz。

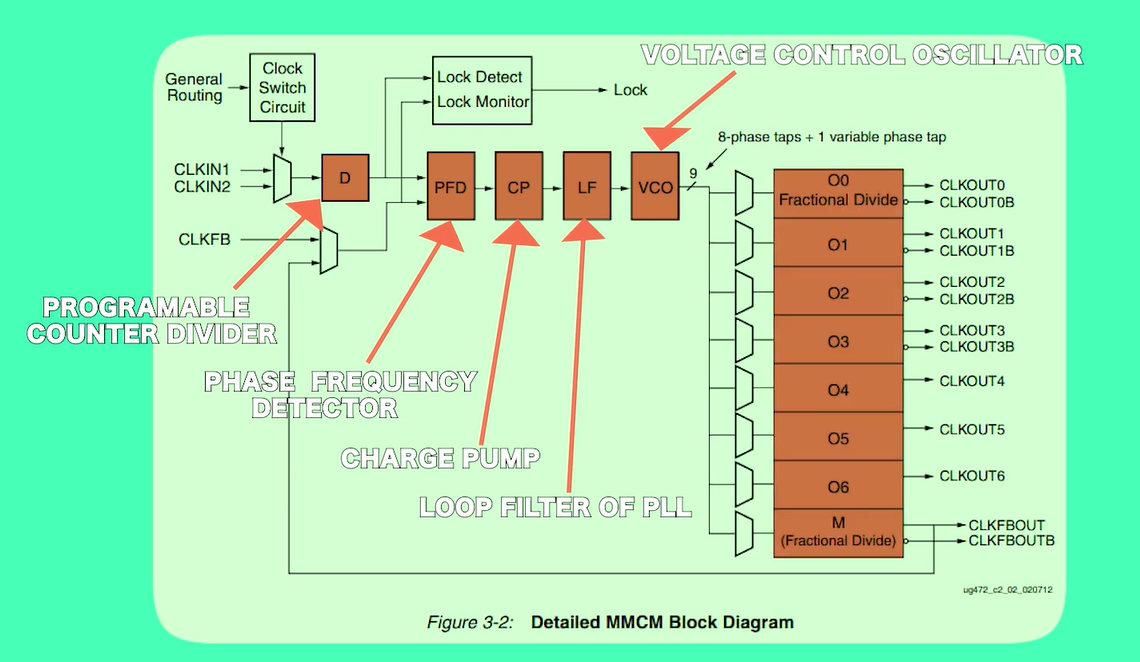

如果你使用 MMCM 来生成不同的时钟频率和相位,MMCM 提供了非常强大的时钟管理功能。下图所示的模块框图中:

D 表示可编程分频计数器(programmable counter divider);

PFD 表示鉴频鉴相器(phase frequency detector);

CP 表示电荷泵(charge pump);

LF 表示环路滤波器(loop filter);

VCO 表示压控振荡器(voltage control oscillator);

最终可以得到 8 路 MMCM 时钟输出,用于频率合成。

至于 PLL,它实际上是 MMCM 的一个子集。从 PLL 的框图可以看到,它也包含了上述主要模块。不过,如果你问我 PLL 和 MMCM 的区别,答案是:

MMCM 具备分数倍频/分频功能,可以灵活生成输入时钟与输出时钟之间的分数关系;

而 PLL 更适合用于频率合成,主要用来生成多路整数倍频的时钟信号。

因此,如果你需要精确的分数倍频,推荐使用 MMCM;如果只是做常规倍频或分频,PLL 就足够了。

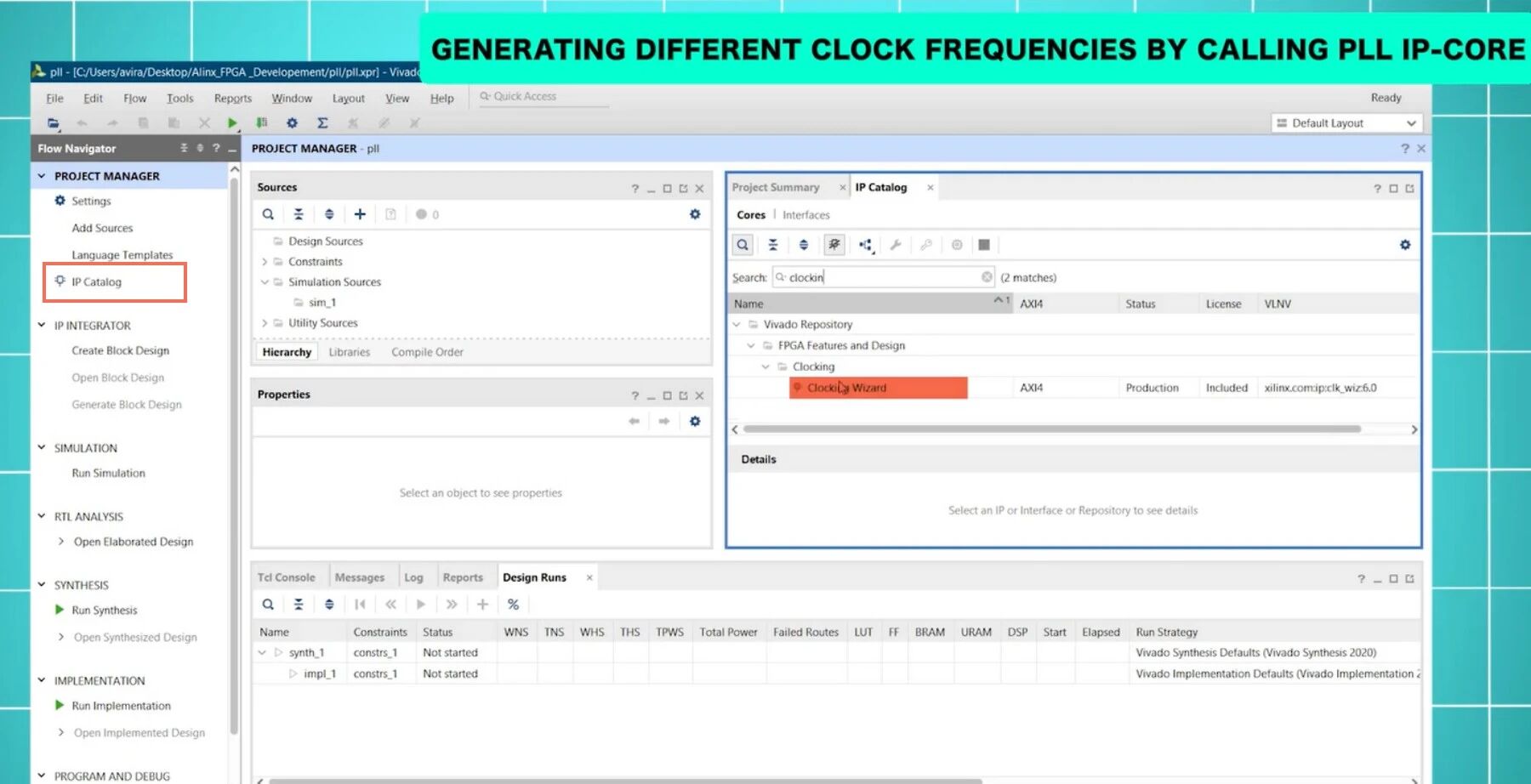

Part 2:在 Vivado 中调用 PLL IP 核

接下来,我会演示如何在 Vivado 中调用 Xilinx 提供的 PLL IP 核,来生成不同的时钟频率。随后我们会把 FPGA 的某个外部引脚配置为时钟输出。

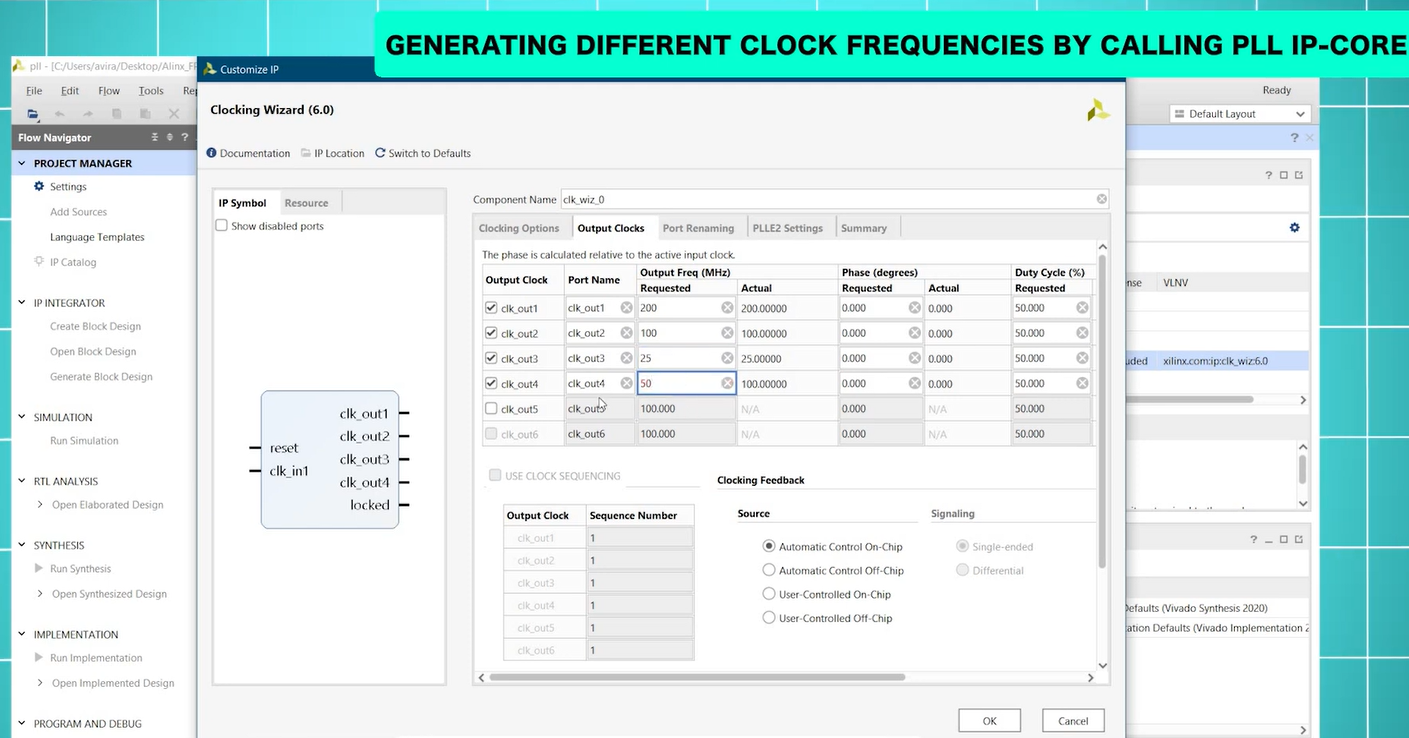

先创建一个 Vivado 工程,然后从 IP Catalog(IP 库) 中搜索并添加 PLL IP 核,这里IP核的名称是 Clocking Wizard。双击它,就会打开 IP 自定义窗口,进入参数配置环节。

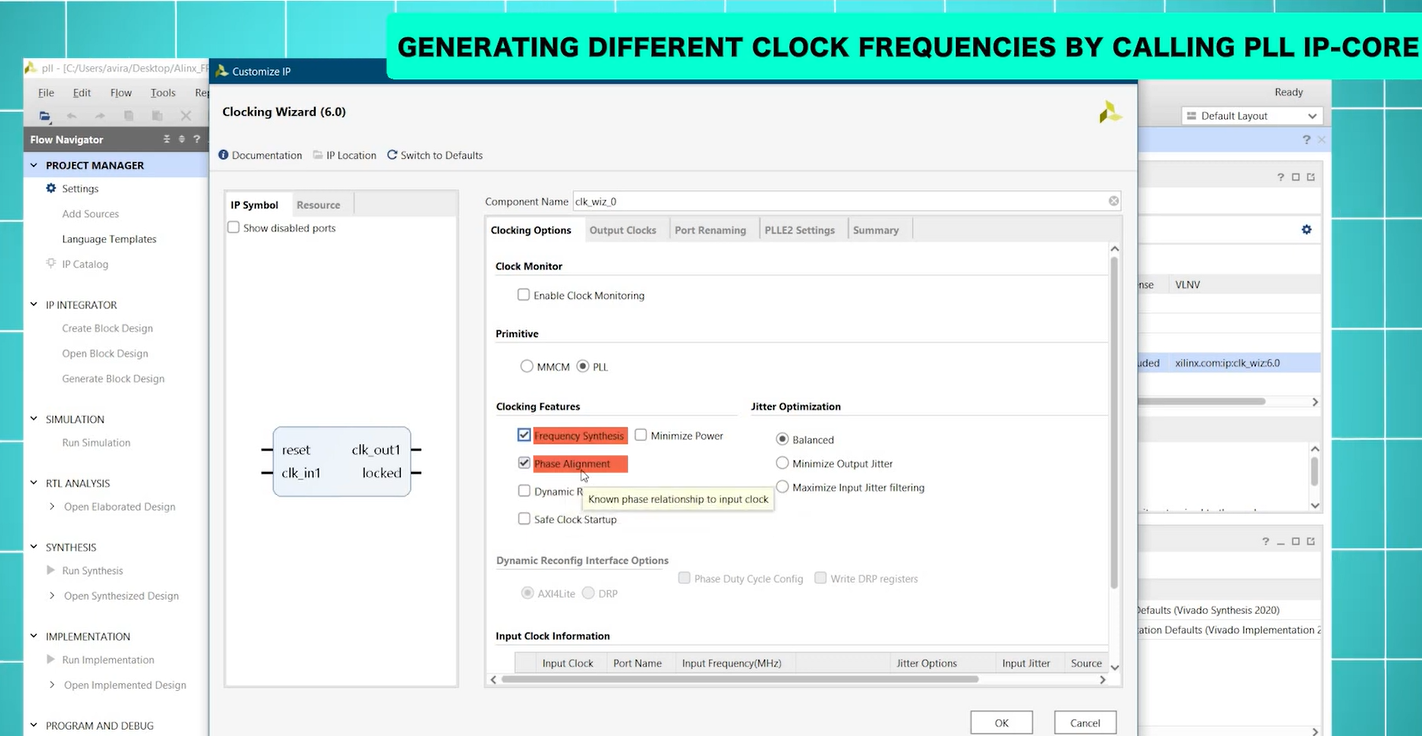

在 Clocking Wizard 配置界面中,选择 PLL 作为时钟生成方式。

勾选频率合成(frequency synthesis)和相位对齐(phase alignment)。

将抖动优化(jitter optimization)设置为 Balanced(平衡模式)。

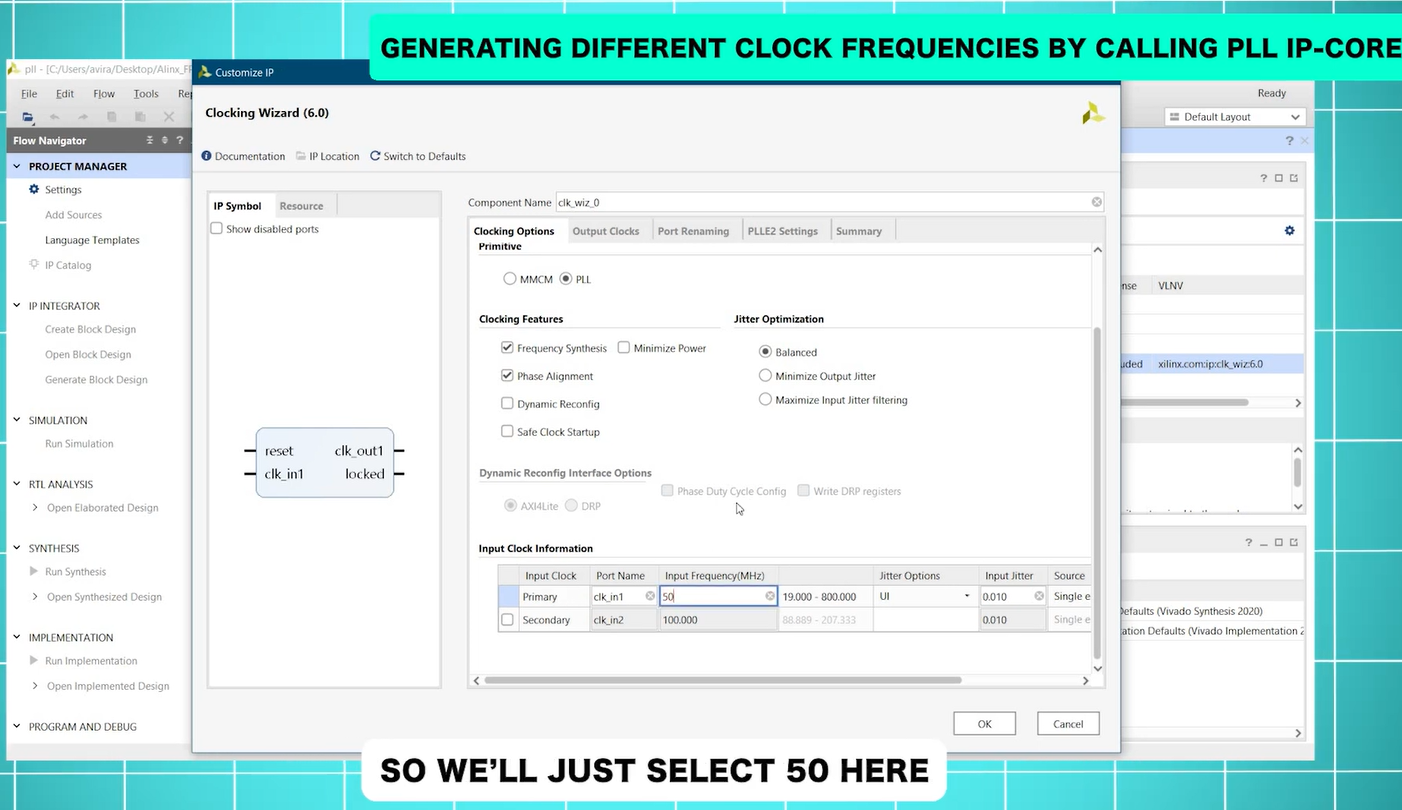

往下拉,可以看到主时钟输入(Primary Clock Input)和辅助时钟输入(Secondary Clock Input)的选项。本例中只有一个输入时钟,也就是 50 MHz,没有辅助时钟,所以直接选择 50 MHz 即可。

接下来设置输出时钟

进入输出时钟(Output Clocks)标签页,生成四路输出,设定为:

输出1:200 MHz(输入的 4 倍)

输出2:100 MHz(输入的 2 倍)

输出3:25 MHz(输入的 1/2)

输出4:50 MHz(与输入相同,用于验证)

设置好后点击 OK,在框图中会看到 locked 信号,它表示 PLL 是否已经锁定。如果该信号为高电平,则说明 PLL 锁定成功。PLL 的输入包括一个 50 MHz 时钟输入和一个复位信号,这里的复位(rst_n)就是常用的低电平有效复位。

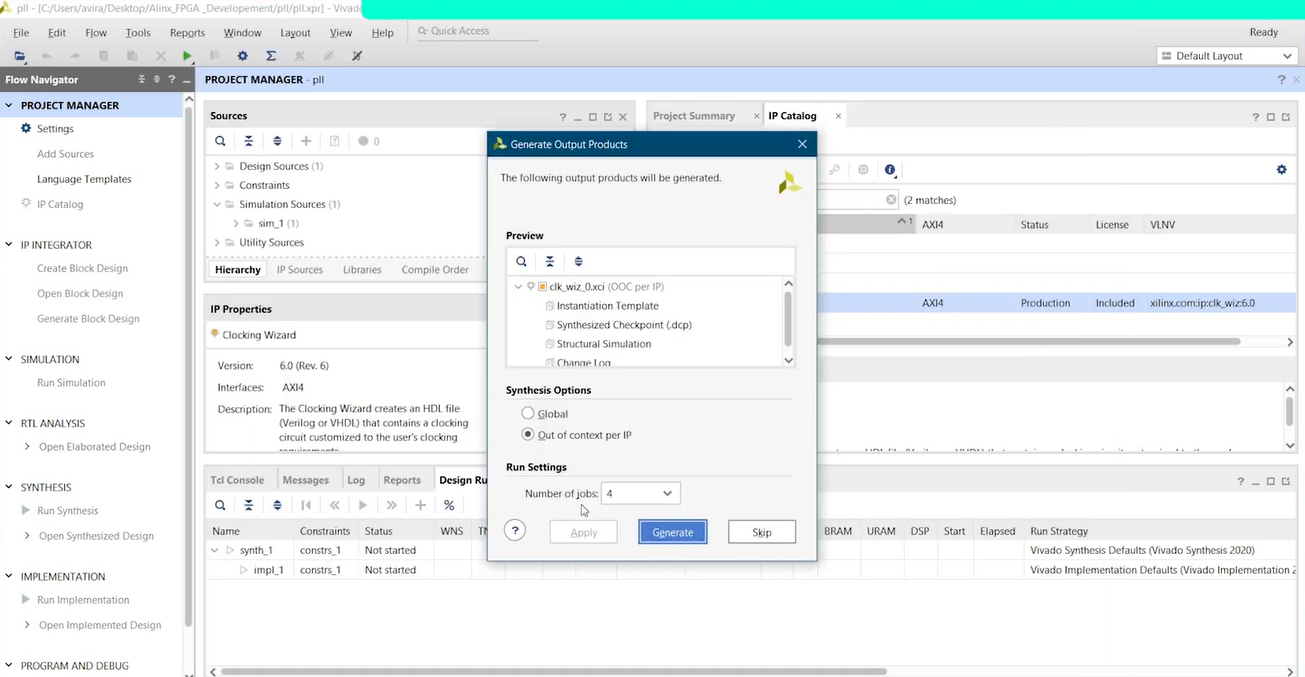

点击 OK 后,会提示选择生成任务数,选择 4 个,然后点击生成。这样,PLL IP 核就会自动加入工程,接下来我们就能在设计中调用它。

Part 3:在 Verilog 中实例化 PLL IP 核

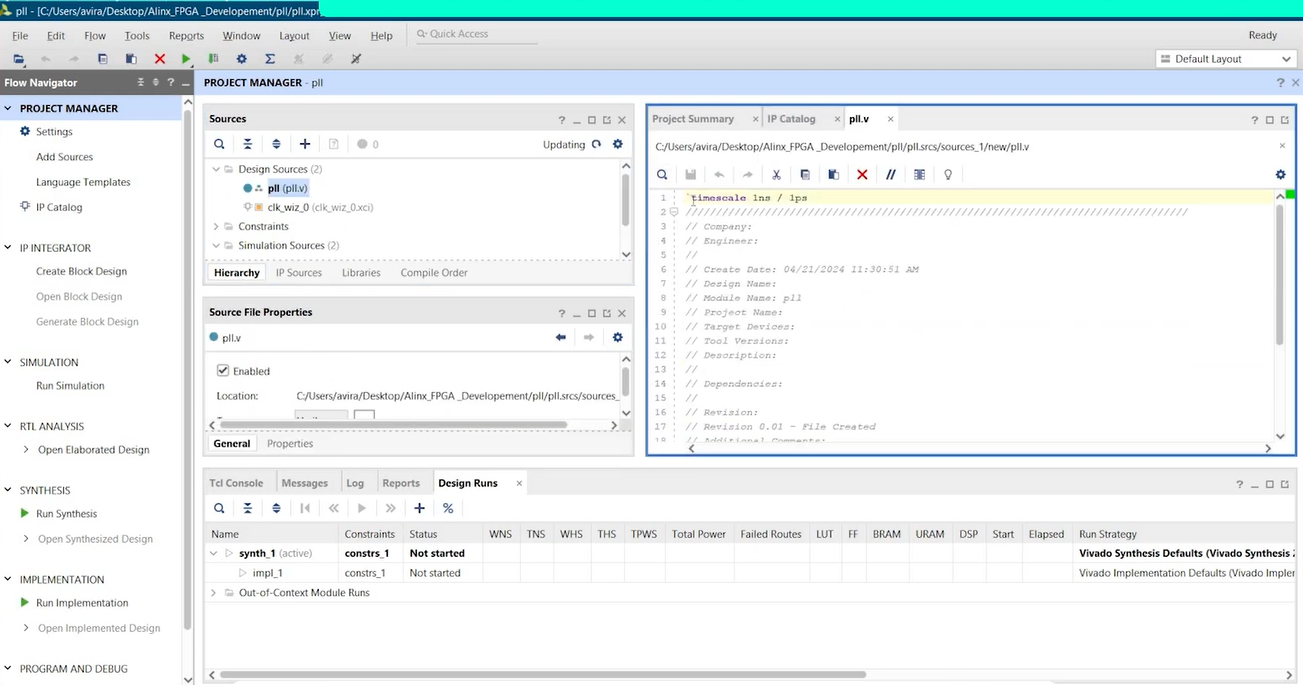

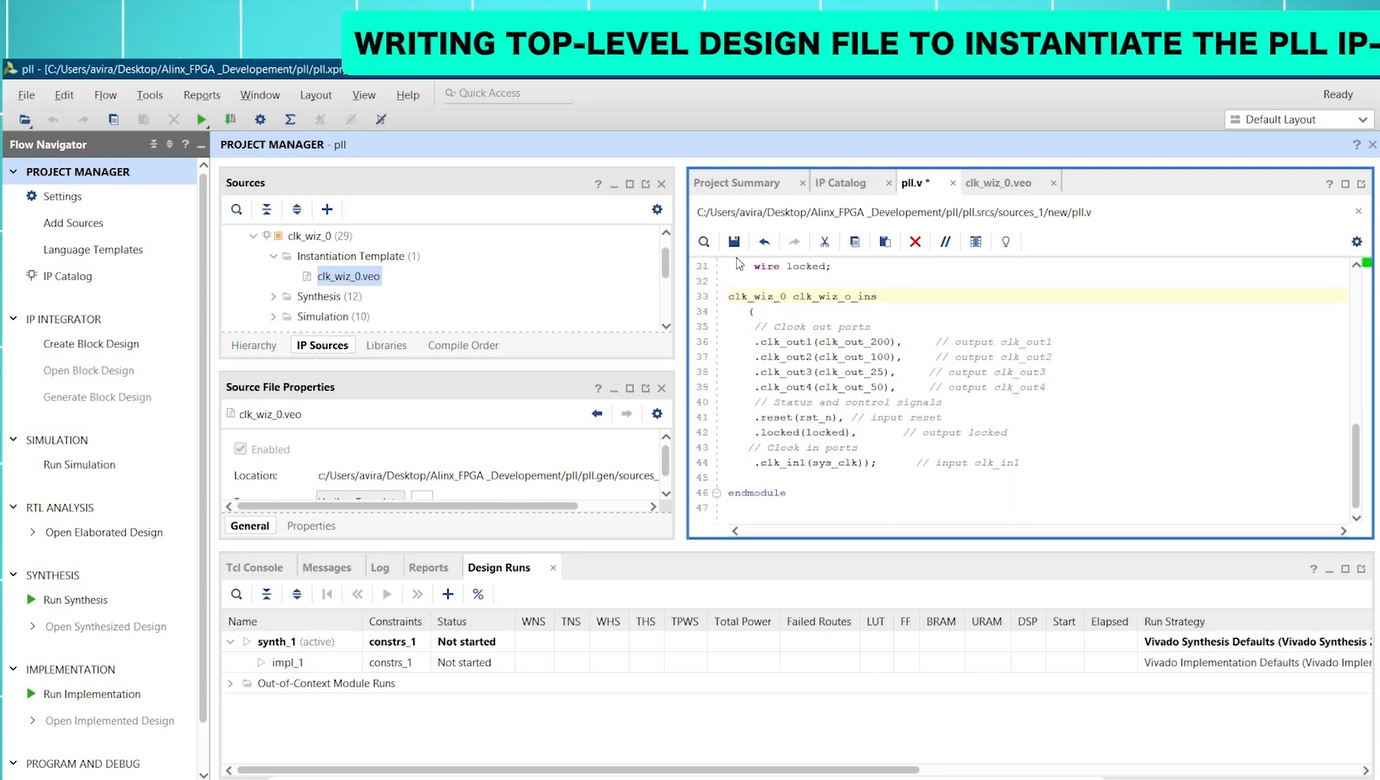

下一步,我们需要编写一个顶层设计文件来实例化 PLL IP 核,并进行仿真。

1. Project Manager → Add Sources → Add or Create Design Sources → Next。

2. 点击 Create File,新建一个名为 PLL 的源文件(pll.v)。

3. 新建完成后,点击 Finish 即可,当前阶段暂不添加任何 IOPorts,直接点击 OK。

双击打开该文件,会看到文件中自动生成了时间精度指令(timescale 1ns/1ps)和一个空模块(module pll)。

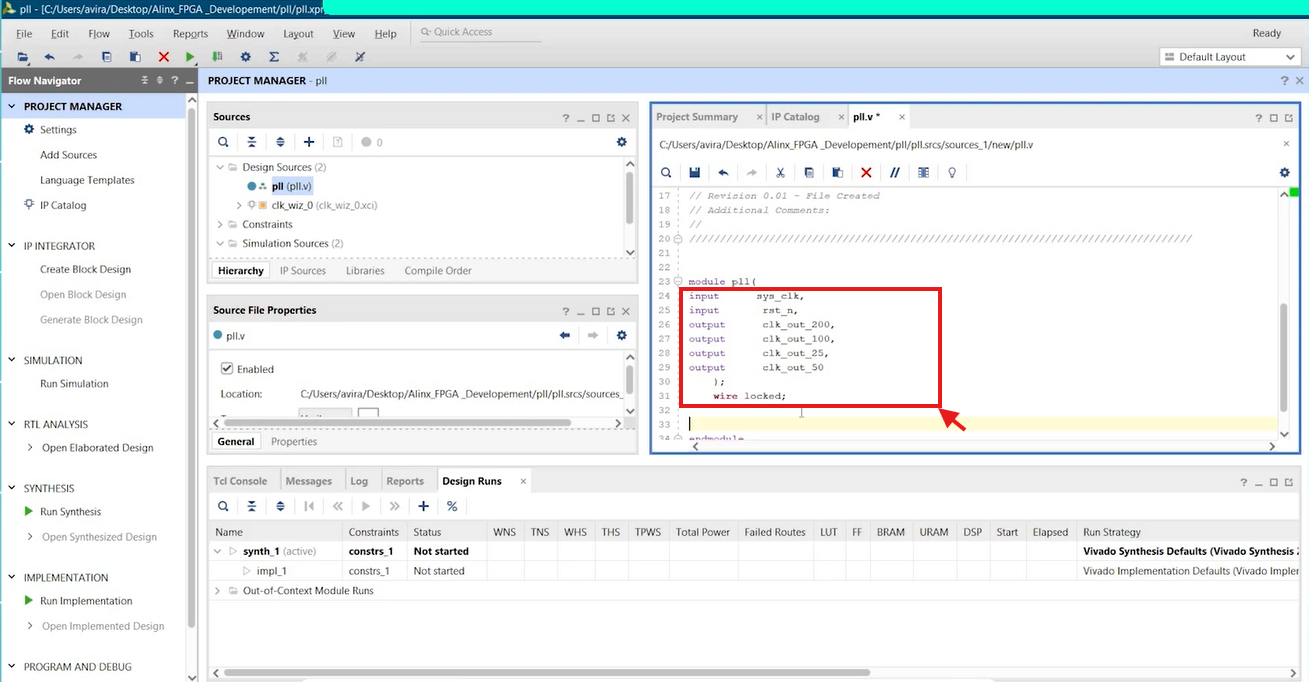

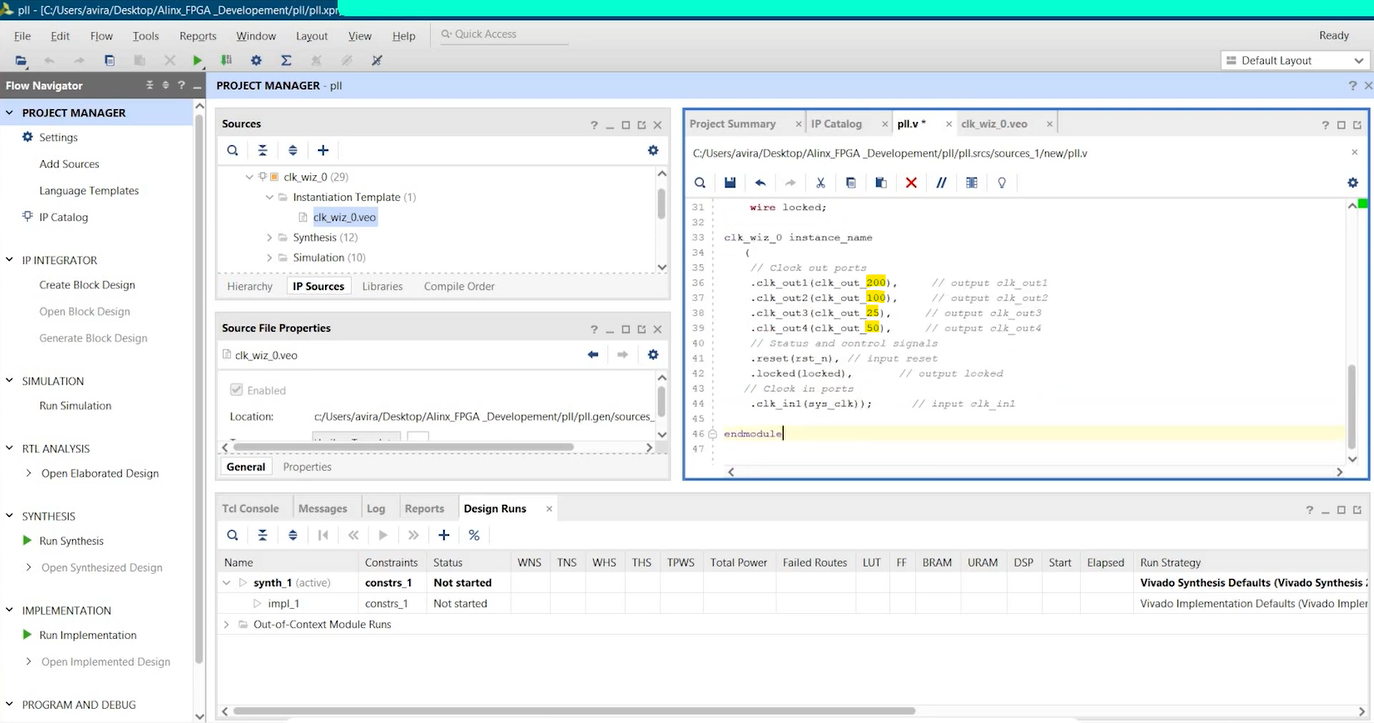

在这个空模块中,我们需要先定义输入输出:

输入:

系统时钟(sys_clk)

复位信号(rst_n),低电平有效,当 rst_n 引脚变为低电平时,开发板就会进入复位状态。

输出:

四路时钟输出(clk_out_200、clk_out_100、clk_out_25、clk_out_50):分别代表200 MHz、100 MHz、25 MHz、50 MHz

锁定信号(locked):定义一个额外的输出线网(wire),用于表示 PLL 模块是否已完成 “锁相”(locked)

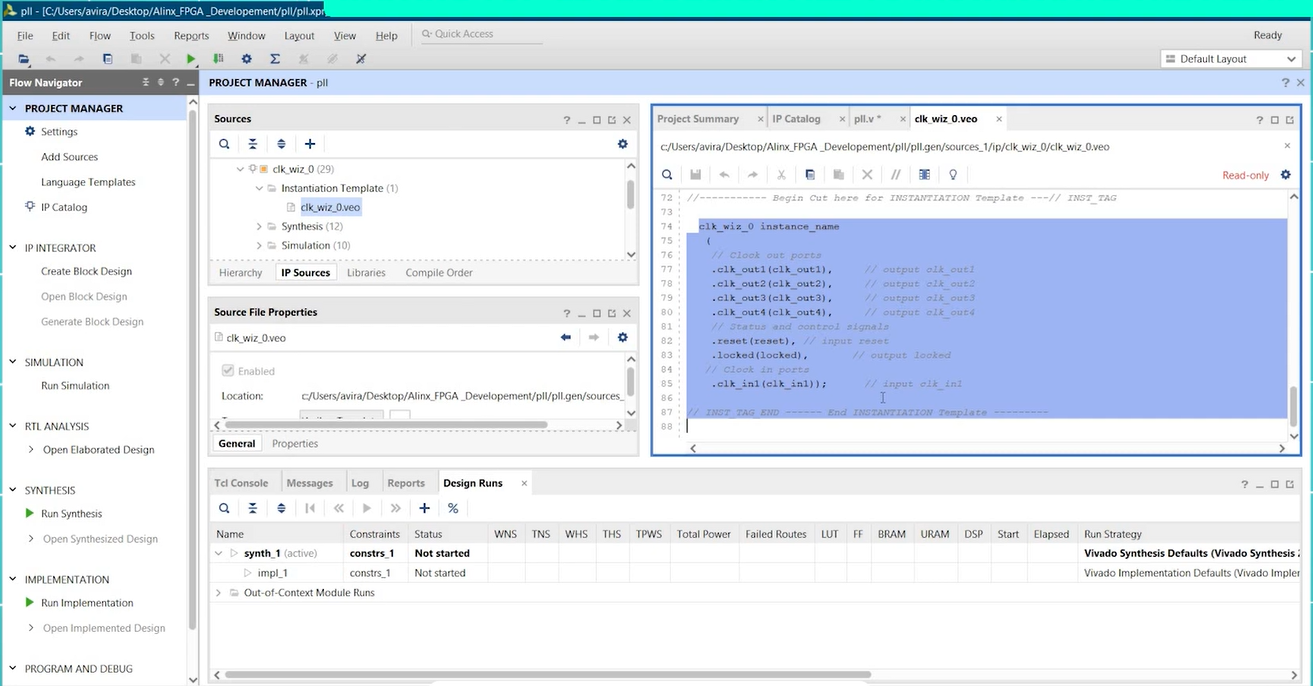

接下来去 IP Sources,打开 PLL IP 核的实例化模板(Instantiation Template),复制模板代码粘贴到顶层文件 ppl.v 中,并把前面定义好的输入输出信号映射进去。

映射完成后,可以将该例程命名为 clk_0_ins,点击保存。

保存后,就能在工程层次结构(Hierarchy)中看到 PLL IP 已成为设计的一部分。

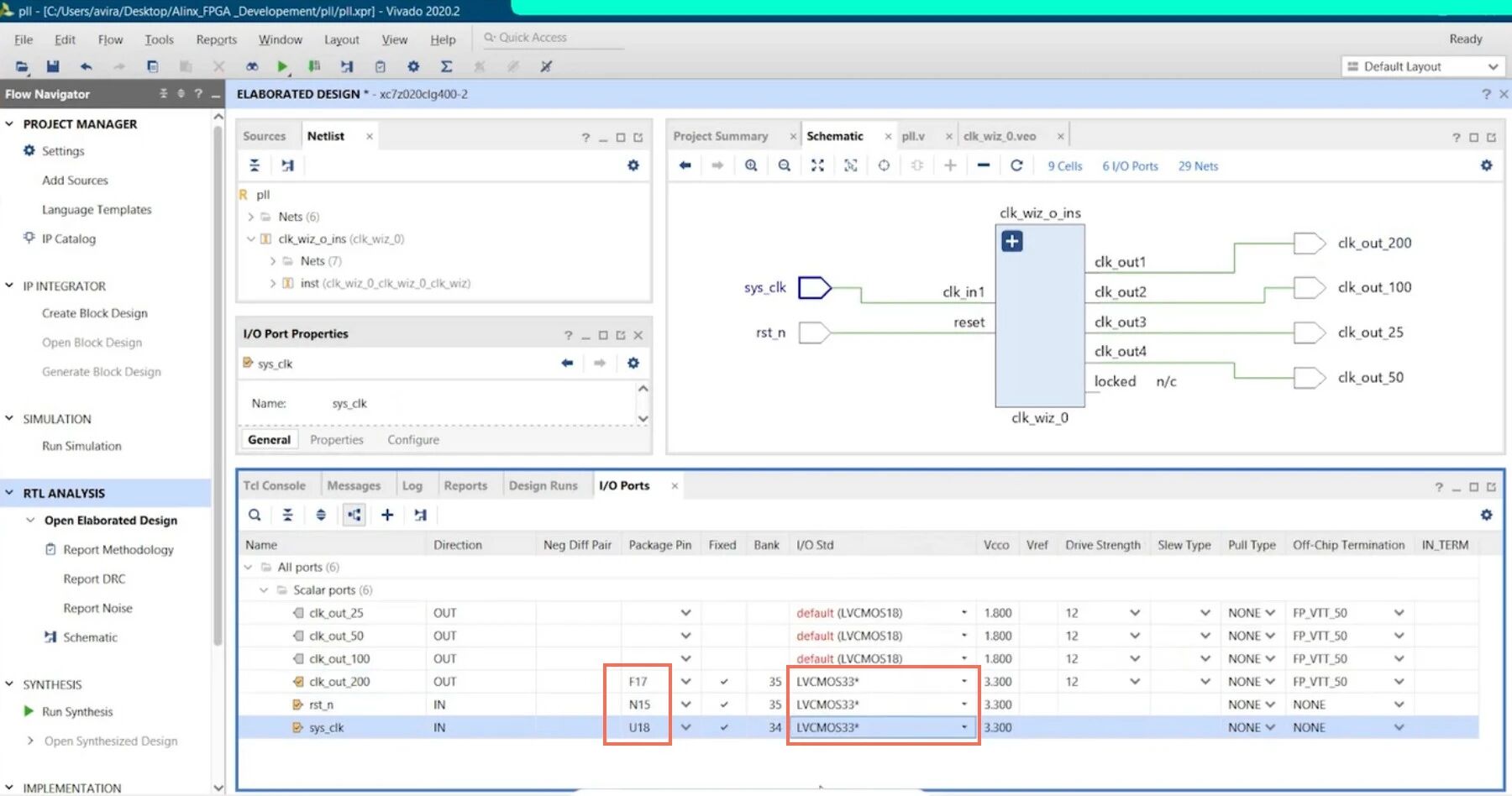

Part 4:约束文件(XDC)配置

接下来要添加输入输出约束:

1. 打开 Window → 点击 I/O Ports 窗口,展开所有输入输出端口。

2. 分配引脚:

rst_n → N15

sys_clk → U18

clk_out_200 → J11 接口的第 3 脚(对应 FPGA 引脚 F17)

3. 设置电压标准:原本默认 1.8V,查阅开发板原理图后可知实际应使用 3.3V LVCMOS,所以改为 LVCMOS33。

保存为 pll.xdc 文件

此时回到 Sources 界面,就能看到新创建的约束文件,双击打开,里面能看到所有引脚分配及对应的 IO 电压标准都已正确配置。

然后我们还需要添加时序约束:使用 create_clock 语句创建系统时钟。

create_clock -period 20 [get_ports sys_clk]

这里 20ns 对应 50 MHz 输入时钟。

Part 5:仿真验证

在烧录硬件之前,先通过仿真验证功能,步骤如下:

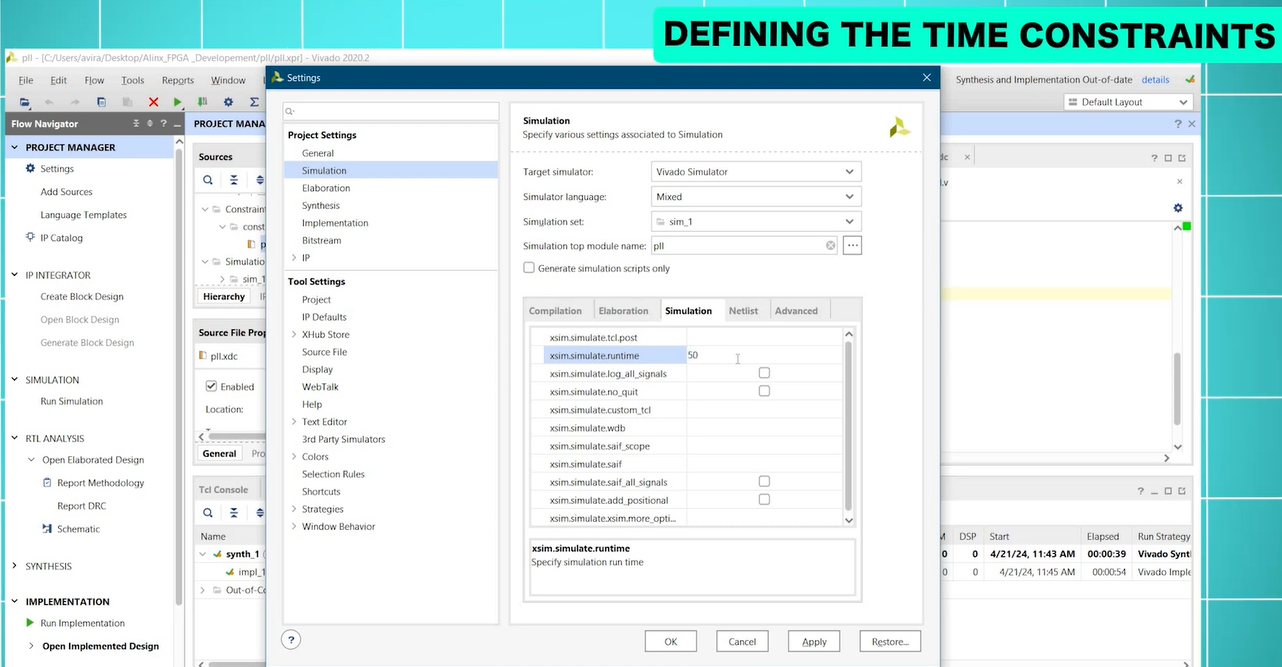

打开 Simulation Settings,将仿真时间设置为 50 ms。

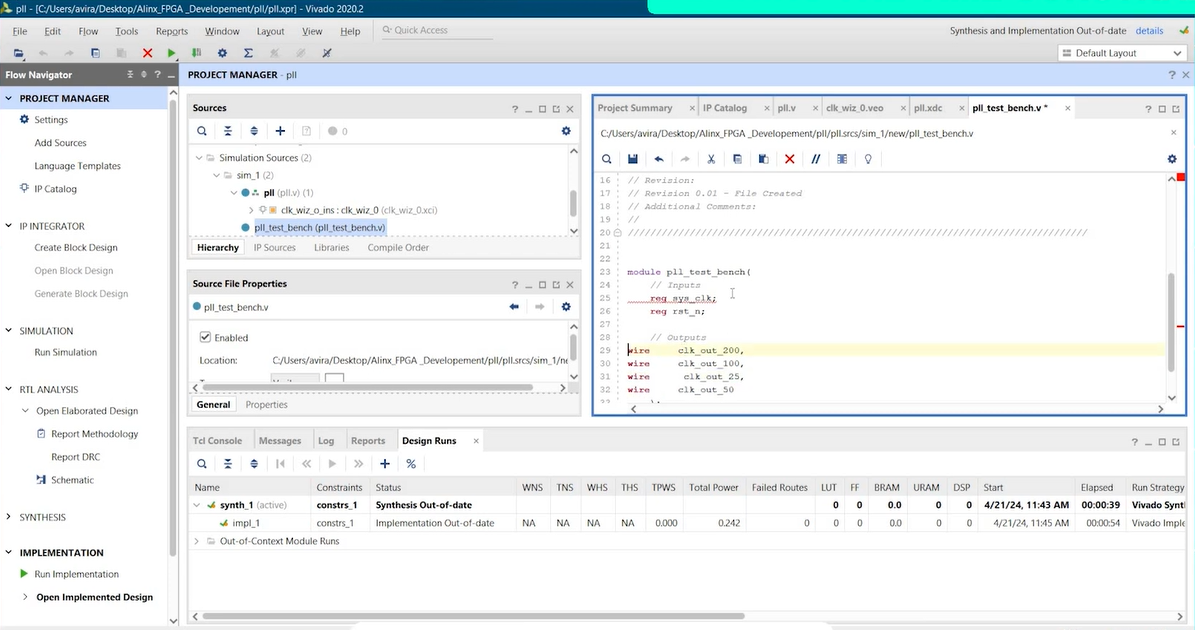

2. 创建仿真文件:Add Sources → Add or create simulation sources → Create,将仿真文件命名为“pll_test_bench”,确认后点击“完成”。当前无需添加 IO 端口,直接点击“确定”。

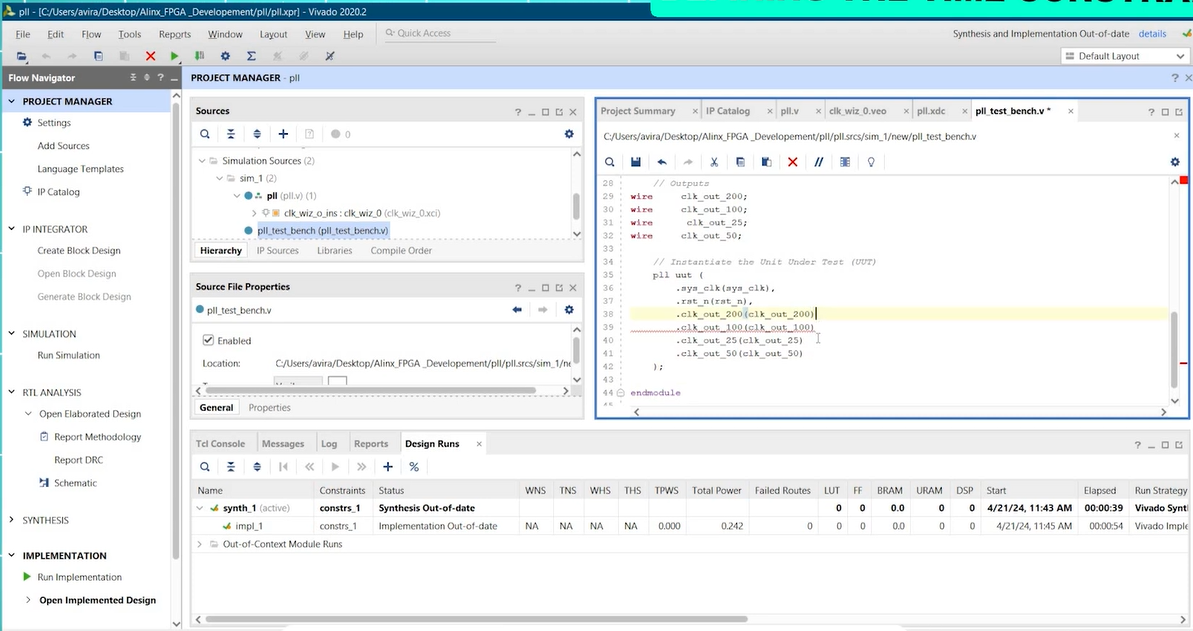

3. 双击打开“pll_test_bench”文件,编写测试代码:

定义输入:sys_clk、rst_n

定义输出:四路时钟clock_out_200、clock_out_100、clock_out_25、clock_out_50

在 testbench 中例化 pll.v,并将输入输出正确连接。

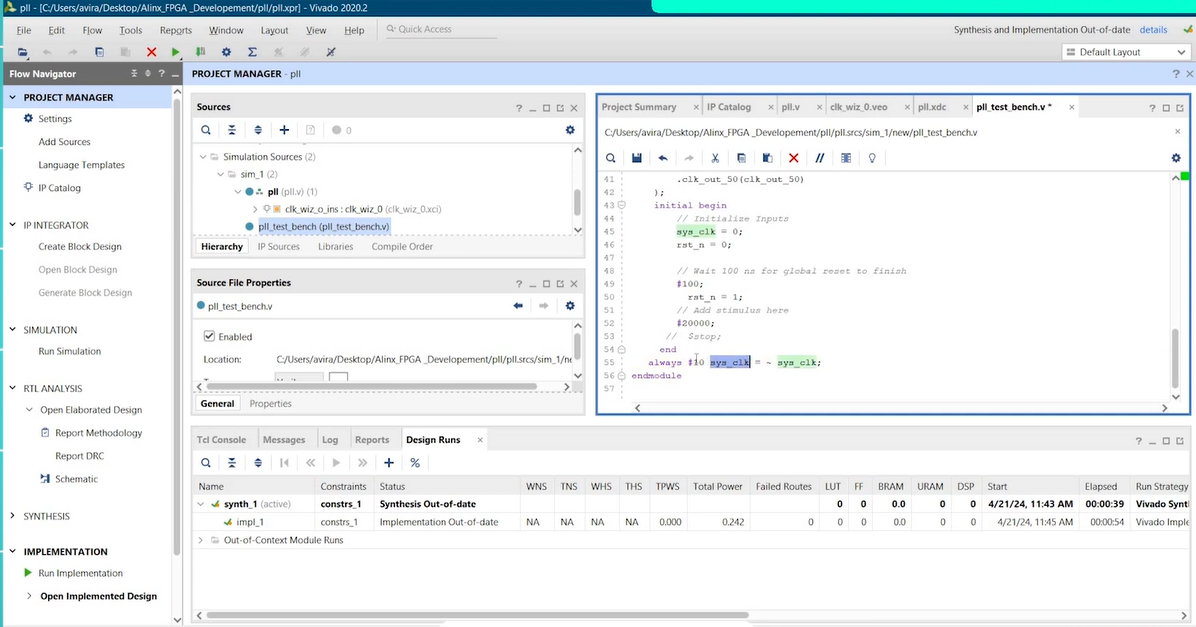

信号初始化:初始时保持复位,rst=0,clk=0。100ns 后释放复位,rst=1。

用 always 语句生成 50 MHz 的输入时钟,即让时钟每 10 纳秒翻转一次,得到周期 20ns 的输入时钟,即 50 MHz。

保存后运行行为仿真(Run Behavioral Simulation)。

在波形窗口中,可观察到四路时钟输出:

200 MHz

100 MHz

25 MHz

50 MHz(与输入同步)

通过波形周期测量,可验证频率正确性。

Part 6:硬件验证

点击 Generate Bitstream,生成 Bitstream 文件,然后点击 Program Device,选择刚才生成的 Bitstream 文件,点击 Program,现在 FPGA 已经烧录完成,PLL IP 核也在 FPGA 上运行了。

用示波器探测 J11 接口第 3 脚,就可观察到对应的 200 MHz 输出波形,和仿真结果一致,说明 PLL IP 正确配置,功能正常。

本教程基于 ALINX AX7020 开发板完成。作为国内领先的 FPGA 开发平台和解决方案提供商,ALINX 提供 AMD Zynq/Versal/Virtex/Kintex 等系列、紫光同创 Kosmo/Titan 等系列的多款高性能开发板与配套资料,广泛应用于智能汽车、工业控制、通信工程、医疗电子等领域。

选择 ALINX,不仅能获得性能优异、接口丰富的硬件平台,还能享受到完善的技术支持与学习资源,助力工程师与开发者快速上手、加速项目落地。