教育培训门户网站模板下载网上有什么做兼职的网站

一、什么是RISC、CISC?

(一)RISC(Complex Instuction Set Comptuer)复杂指令集架构

1.定义:设计理念强调通过单条指令完成复杂操作,指令长度可变,操作码和寻址模式多样。典型代表包括x86架构(如Intel、AMD处理器)。

2.特点

指令数量庞大,支持高级语言直接映射(如内存到内存操作)。

微码解码机制:复杂指令由内部微程序控制单元分解为微操作。

硬件利用率高,但功耗和设计复杂度显著增加。

3.应用场景

适合通用计算,尤其在代码密度敏感的场景(如早期嵌入式系统)。

向后兼容性强,利于历史软件生态维护

桌面/服务器CPU

(二)(Reduced Instuction Set Comptuer)精简指令集架构

1.定义:通过简化指令集提高执行效率,指令长度固定,采用加载-存储架构。代表架构包括ARM、RISC-V、MIPS。

2.特点

指令数量少(通常不足100条),仅支持基础操作(如算术逻辑运算)。

流水线友好:单周期指令执行,依赖编译器优化复杂操作。

寄存器数量多(通常32个以上),减少内存访问延迟。

3.应用场景

低功耗设计主导移动设备(如智能手机、物联网终端)。

可扩展性强,RISC-V等开源架构推动定制化芯片发展

移动/嵌入式处理器

二、冯·诺伊曼架构和哈弗架构有什么区别?ARM内核属于哪一种?

(一)冯·诺伊曼架构和哈弗架构的区别

1.冯·诺依曼架构:指令和数据没有加以区分,而是把程序看成一种特殊的数据,都通过数据总线进行传输。因此指令读取和数据访问不能同时进行,数据吞吐量低,但总线数量相对较少且管理统一。大多数通用计算机的处理器(Intel X86)和嵌入式系统中的ARM7处理器均为冯·诺伊曼结构。

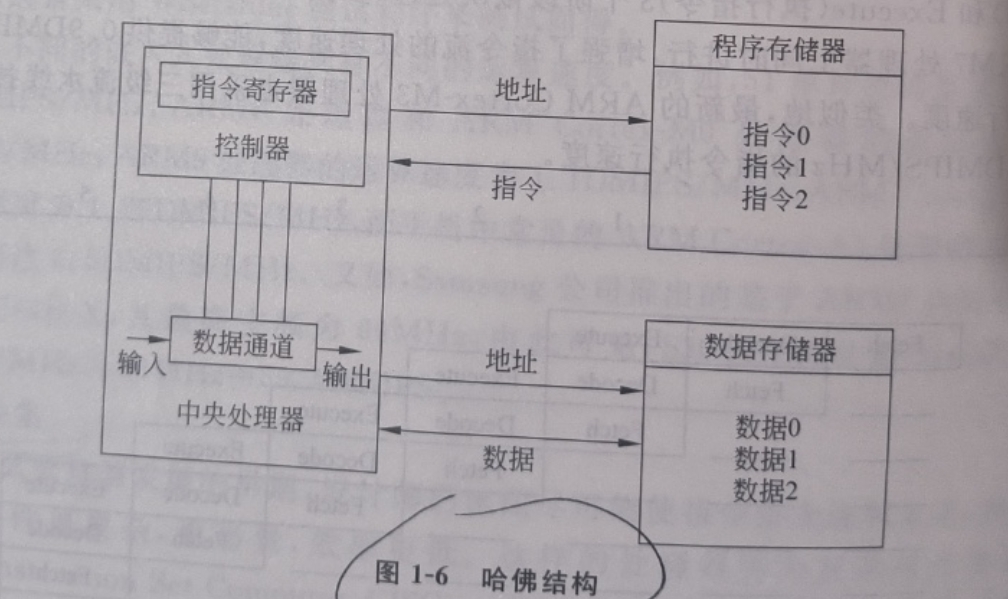

2.哈弗结构:指令和数据分开存储在不同存储空间,使得指令读取和数据访问可以并行处理,显著提高了系统性能,只不过需要较多的总线。常用于对实时性要求高的嵌入式系统或DSP(数字信号处理器)。

(二)ARM内核属于哪一种

经典ARM7系列(冯·诺依曼结构)

①.如ARM7TDMI使用单一总线访问指令和数据,共享存储器空间。

②.优势是设计简单,但可能存在“冯·诺依曼瓶颈”(指令和数据争抢带宽)。

2.ARM9及以后的改进型哈佛结构

①.ARM9系列引入分离的指令和数据总线(如AMBA AHB总线),但共享同一物理存储器(逻辑分离)。

②.允许CPU同时获取指令和加载数据,提升性能。

3.Cortex系列的混合架构

①.Cortex-M/R/A系列进一步优化:

指令缓存(I-Cache)与数据缓存(D-Cache)物理分离,实现哈佛式并行访问。

②.外部存储器仍可能统一编址(冯·诺依曼特征)。

例如:Cortex-M7采用双总线(I-Bus和D-Bus),支持指令预取与数据加载并发执行

三、ARM-A系列内核中都有什么?

(一)ALU(Arithmrtic Logic Unit)算术逻辑单元

(二)16个通用寄存器,倒数第一:PC、倒数第二:LR、倒数第三:SP

(三)MMU(Memory Management Unit)内存管理单元(裸机关闭)

(四)Cache(高速缓存)

1.date cache:缓存数据(关闭)

2.instruction chche:指令(打开)

(五)CPSR(Current Program Status Register)当前程序状态寄存器:N,溢出标志位

(六)SPSR(Save Program Status Register)备份程序状态寄存器:备份CPSR

四、ARM有几种工作方式?

(一)用户模式(User Mode)

特权级别:非特权模式。

用途:普通应用程序运行的环境,无法直接访问受保护的硬件资源或执行某些特权指令。

特点:安全性高,权限受限。

(二)特权模式

1.系统模式(System Mode)

用途:运行操作系统内核代码,与用户模式共享寄存器组。

特点:权限高,但寄存器组与用户模式一致

2.快速中断模式(FIQ Mode, Fast Interrupt Mode)

用途:处理高速中断请求,如DMA传输或高优先级外设中断。

特点:独立的寄存器组(R8-R14),减少上下文切换开销。

3.普通中断模式(IRQ Mode, Interrupt Mode)

用途:处理普通中断请求。

特点:与FIQ模式相比优先级较低,寄存器组部分独立。

4.管理模式(Supervisor Mode, SVC Mode)

用途:处理器复位或执行软件中断指令(SWI)时进入,通常用于操作系统的内核代码。

特点:默认的异常处理模式。

5.中止模式(Abort Mode)

用途:处理内存访问异常(如缺页或权限错误)。

特点:用于虚拟内存或内存保护机制。

6.未定义模式(Undefined Mode)

用途:处理未定义指令异常。

特点:用于扩展指令集或调试。

(三)监控模式(Monitor Node)

适用架构:ARMv7及更高版本(如支持安全扩展的Cortex-A系列)。

用途:在安全状态(Secure World)和非安全状态(Non-secure World)之间切换。

特点:仅存在于支持TrustZone技术的处理器中。

(四)虚拟化扩展模式(Hyp Mode)

适用架构:ARMv7及更高版本(如支持虚拟化扩展的Cortex-A15)。

用途:运行虚拟机监控程序(Hypervisor),管理虚拟化环境。

特点:提供额外的特权级别(EL2)。

五、什么是异常向量表?

(一)定义:是处理器中用于处理异常和中断的机制,通常由一组预定义的地址组成。每个地址对应特定类型的异常或中断,当事件发生时,处理器会自动跳转到对应的地址执行处理程序。

(二)作用

集中管理异常处理程序:为每种异常分配固定入口地址,简化硬件和操作系统的交互逻辑。

快速响应:通过硬件直接跳转,减少查找处理程序的时间,提高实时性。

标准化设计:不同架构(如ARM、x86)均有类似机制,便于跨平台开发。