【思考】作为“纯硬件”的ADC芯片,它是如何识别并处理SPI命令的?

目录

壹 \\ 问 题

贰 \\ ADC芯片的内部架构

叁 \\ ADC芯片处理SPI指令的流程

壹 \\ 问 题

作为一个嵌入式从业者,与ADC打交道算是家常便饭;

都知道ADC是将模拟信号采样、量化成数字信号,以便进行处理;

通常Soc或MCU可以处理各类指令和复杂逻辑,是因为内部集成了通用的计算内核,如Arm或RISC-V架构的IP核;

但作为纯硬件架构的ADC芯片是如何处理MCU下发的各种指令的呢?

贰 \\ ADC芯片的内部架构

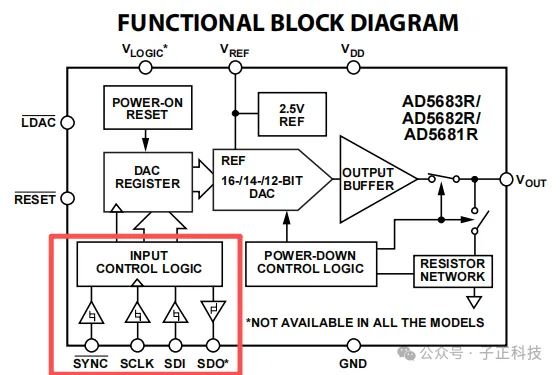

某款ADC内部功能图

上面是某款ADC内部的功能框图,可以看出它的核心功能只有A/D转换涉及的各种硬件功能块,并没有类似ARM或者RISC-V这样通用的IP核出现;那么它是怎么处理指令的呢?

ADC芯片之所以能够处理相应的控制指令,核心就藏在标记出的“INPUT CONTROL LOGIC”功能块中,这个功能块并不只是SPI通信接口那么简单;

实际上,它还包含了一个“状态机”,也叫做“控制逻辑单元”,这个逻辑单元不运行操作系统,也不执行通用程序;

这个模块承担的任务是:

· 解析SPI/I²C传来的数据帧(如寄存器地址+数据);

· 将配置写入内部寄存器(如采样率、增益、通道选择等)

· 控制ADC的启动、校准、电源管理等状态切换。

其实看到这里就很清晰了,虽然这个控制逻辑单元不是通用CPU,但从功能上来说,类似于一个专用微型内核,专用于ADC的配置管理和状态切换;

它完全由数字逻辑电路(门电路、触发器)实现,没有软件或固件运行,在硅片上“硬连线”实现,专为执行单一指令设计,这也是为什么只能识别厂商提供的控制指令,无法识别通用软件或逻辑。

叁 \\ ADC芯片处理SPI指令的流程

通常MCU利用SPI总线向ADC发送各种配置指令,ADC是如何接收这些指令并进行处理的呢?

回顾一下SPI通信的基本结构:

1、CS或NSS:片选信号,用于选中芯片;

2、SCLK:通信时钟,由MCU提供,同步数据传输;

3、MOSI:主发送、从接收,主控下发指令;

4、MISO:主接收、从发送,用于芯片返回应答数据;

基于SPI通信的这种固定结构,ADC在接收到指令后,处理流程就相对容易得多;

第一步:当CS或NSS被拉低,ADC芯片知道自己被选中,即将会有命令下发;

第二步:在SCLK的边沿进行采样,(至于是上升沿还是下降沿有效,取决于厂商规定的SPI配置),每个边沿ADC都会从MOSI数据线上获取一个bit的数据;

第三步:ADC使用寄存器地址译码器来识别数据中的寄存器地址,并将收到的指令写入对应的寄存器中;

第四步:ADC中的“控制逻辑单元”根据写入的指令进行状态调整,例如修改采样频率、PGA增益选择、启动转换等操作;

经过这样一套流程,就可以完成一次指令的识别和处理;

整个过程全部由硬件处理,确定性极强、速度极快。

这种结构设计,也是为了保证在高速、高精度场景下的低延迟、高可靠性和确定性行为。

那么反过来,DAC芯片的指令识别和处理也类似。